(34) ШИФРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1985 |

|

SU1298801A2 |

| Шифратор | 1980 |

|

SU920835A1 |

| Шифратор | 1981 |

|

SU1005187A2 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Полевая телеметрическая сейсмическая станция | 1986 |

|

SU1368837A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ, ОТОБРАЖЕНИЯ И ОБРАБОТКИ ПЕРЕХОДНЫХ ПРОЦЕССОВ В КОНТАКТНОЙ ЦЕПИ МАГНИТОУПРАВЛЯЕМЫХ ПРИБОРОВ | 1990 |

|

RU2060552C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Шифратор | 1978 |

|

SU752470A2 |

..:. I . Изобретение относится к запоминающим устройствам. По основному авт. св. № 590825 известен шифратор, содержащий ячейки пам ти, выходы которых подключены к первому входу соответствующих элементов считывания; вторые входы которых подключены к шине разрешения считывания, формирователи сигналов сброса, выходы которых подключены к входам соответствующих ячеек памяти, дешифратор, формирователи входных сигналов, входы которых подключеныК выходам соответствующих элементов считывания, а выходы - к входам дешифратора и входам роответствующих- формирователей сигналов сброса, и элементы ИЛИ, первые вх ды которых соединены с выходами соответствующих, ячеек памяти, кроме первой, второй вход первого элемента ИЛИ соединен с выходом первой ячейки памяти и с третьим входом последующего элемента считывания, а выходы всех эле ментов ИЛИ соединены со вторыми входами последующих элементов ИЛИ и с третьими входами последующих элементов считывания 1 . При поступлении сигналов на входные шины этого шифратора на его выходе появляется Код адреса, соответствующий номеру шины, на которой появился сигнал. Если на входные шины шифратора сигнал не поступает, то коды адреса соответствующих номеров шин на выходе шифратора отсутствуют. При использовании этого шифратора в устройствах автоматизированных систем управления, контроля и обработки инфо(мации он не может обеспечить пресбра- зование в код уровней сигналов на его входаых , что сужает его область. применения. Цель изобретения - расширение области применения ши4ратора за счет обеспечения возможности его исполээования не только для фиксирования факта появ;юния сигнала, но и для преобразования

код уровня входных сигналов на его шиах.

. Посгавленна цель цосгигаегся гам, что в шифратор ввеоены компараторы по ч№:лу ячеек памяти, генератор тактовых импульов, элемент И, реверсивный счетчик, дополнательный дешифратф и анфроаналогоёый предбразовате|К, вюсод которрго под к одннм нз входов KriLmapaTopa, цругае входы которых явлшотся входами шифратфа, а выходы подключены соответсгвенно ко входам ячеек памяти, выход генератсфа тактовых импульсов подклк чен к первому входу элемента И, второй вход которого соединен с выходом пос- Шего элемента ИЛИ, а выход - с oftним из входов реверсивного счетчика, другие входы которого соединены с выходами дополнительного дешифратора, вход котсрого подключен ко входу цнфроаналогов лч) преофазователя и выход) реверсивного счетчика, йвлякицемуся одним из выходов ши4 атора.

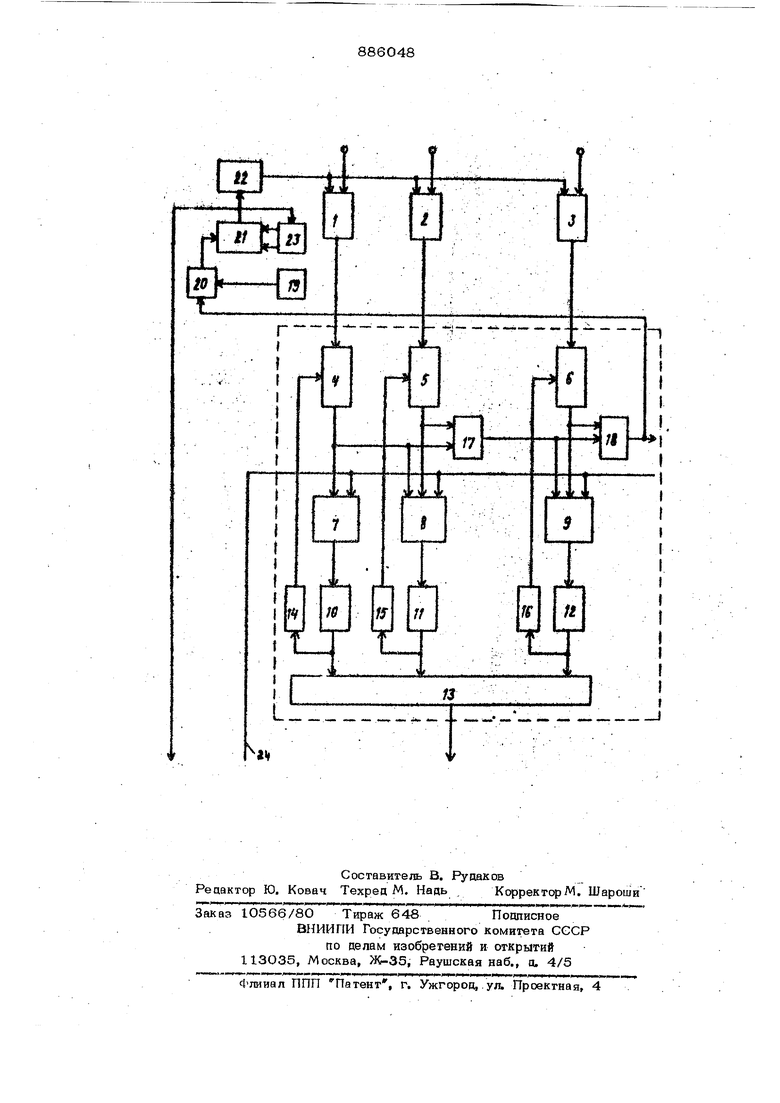

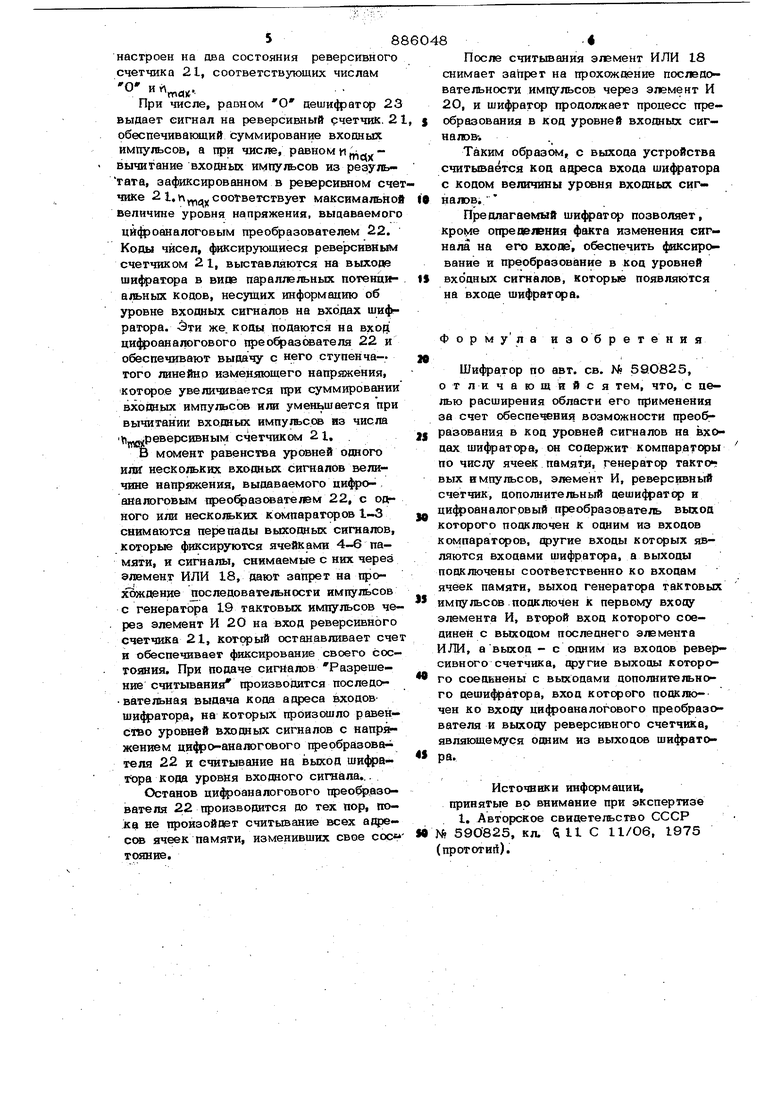

На чертеже изображена функциональная схема шифратора.

Шифатф содержит компаратор 1-3, ячейки 4-6 памяти, Э1юменты 7-9 считывания, ф(фм|фоввтели входных сигналов, ойшифчэагор 13, формирователи 14-16 сигна1Ш сброса, элементы ИЛИ 17 и 18, генератеч5 19 тактовых импульсов, элемент И 20, реверсивный счетчак

21,цифроаналопгвый преобразователь 2,

дополнительный дешифратор 23 я шину 24.

Выход преобразователя 22 подалючен к одним из входов компараторов 1-.3, 1фугие входы которых являк тся входами (аифратора, а выходы подключены соотве гGTBSHHO ко входам памяти. Выход генератора 19 подключен к первоц; входу элемента И 20, второй В|;кодкоторого соединен с выходом элемента ИЛИ 18, а выход - с одним из входов счетчика 21, цруше входы которого соединены с выходами дешиф|}атора 23, вход которого подключен Ко входу преобразователя 22 и выходу счетчика 2 I, являкяцемуся выходом устройства.

Шифратор работает следующим образом..

Входные сигналы поступают на один из входов компаратфов 1-3, на другие входы которых поступает ступенчатое линейно изменяющееся напряжение с вь хода нифроаналогового преофазователя

больше, чем сигнал на Bbixoite цифроана/югового преобразователя 22, а если .Входной аналоговый сигнал меньше, чем сигнал на выходе цифчроаналогового преобразователя 22, то выходной сигнал Компаратора принимает второе состояние, т.е. на выходе компаратора в момент равенства уровня входаого сигнала с уровнем сигнала с вьосода цифроанапогового tipeоф ователя 22 происходит перепад выходного сигнала компаратрра из первого во втфое состояние и наоборот. Ячейки 4-5 памяти фйКснруют этот перепад и выходнь1ми сигналами открывают элементы

5 7-8 считывания. При подаче сигнала на шиву Разрешение считывания 24 он прокоцкт через э|емент 7 считывания и поступает на формирователь 10 входных сигналов. Выходной сигнал с формирователя 1О подается на дешифратор 13 и на формирователь 14 сигналов сброса. На дешифраторе 13 сигнал превращается в код ячейки 4 памяти и поступа- ет с выхода д цифратора на выход ратора.

Сигнал с выхода формирователя 14 сигналов сброса попадает на вход ячейки 4 памяти и устанавлив т ее в состояние О.

Сигнал считывания с шины Разрешен нив счйтьшания 24 через элементы, 8 и 9 считьшания не проходит, так как они закрыты запрещающим сигналом, поступающим на один из их входов.

Прс;ю установки в О ячейки 4 памяи ти элемент 8 считывания открывается и сигнал с шины Разрешение считывания 24 проходит через формирователь 11 и 15 и деши;фратср 13 аналогично снгн&лу от эламента 7 считывания. После считывания ацреса ячейки 5 памяти происходит аналогичный прсщесс считывания ащэеса ячейки 6 пам$1ти. Бели на ячейку памяти входной сигнал не поступил, соотвйгствующий элемеит считывания не открывается и код адреса соответствующей ячейки памяти на вько№ дешифратс а 13 отсутствует.

Таким образом, перепады с выхода компараторов феобразуются в коды ад

0 ресов ячеек памяти и указанные коды выдаются с шя атара,

Генератор 19 тактовых имц)льсов выдает последовательность нмгцгльсов через элемент И 20 на вход реверсивного

5 счетчика- 21, который производит суммйрсжание или вычитание входных импульсш в зависимости от сигналов выдаваемых дешифратором ,23. Дешифратор 23 58 настроен на два состояния реверсивного счетчика 21, соответствующих числам При числе, равном О дешифратор 23 выдает сигнал на реверсивный счетчик. 2 обеспечивакщий суммирование входных импульсов, а при , равном ц д вычитание входных импульсов из результата, зафиксированном в реверсивном сче чике 2 l,h(,j( соответствует максимально величине уровня напряжения, выдаваемог цифр оан а логов ым преобразователем 22. Коды чисел, фиксирующиеся реверсивным счетчиком 2 1, вьгставляются на выходе шифратора в ви( параллельных потенанальных Кодов, несущих информацию об уровне входных сигналов на входах шифратора. Зти же. коды подаются на вхоц ци4роаналогового {фвобразсжателя 22 и обеспечивают выдачу с него ступенчатого линейно изменяющего напряжения, которое увеличивается при суммировании входных импульсов или уменьшается при вычитании входаых импуга сов из числа 11п.реверсивным счетчиком 21, . В момент равенства уровней одного или нескольких входных сигналов величине напряжения, выдаваемого ци4 оаналоговым преобразователэм 22, с одг його или нескольких компараторе 1-3 снимаются перепады выходных сигналов, которые фиксируются ячейками 4-6 памяти, и сигналы, снимаемые с них через элемент ИЛИ 18, дают запрет на прохождение последовательности импульсов с генератора 19 тактовых импульсов через Э1юмент И 20 на вход реверсивного счетчика 21, который останавливает сче и обеспечивает фиксирование своего состояния. При подаче сигналов Разрешение считывания производится последовательная выдача кода адреса входов шифратора, на которых произошло равенство уровней входных сигналов с напряжением цифро-аналогового треобразова теля 22 и считывание на выход шифратора кода уровня входного сигнала.. Останов цифроаналогового преобразователя 22 производится до тех пор, пока не произойдет считывание всех адресе ячеек памяти, изменивших свое сос тояние. 8 После считьюания элемент ИЛИ 18 снимает запрет на прохождение последовательности импульсов через элемент И 2О, и шифратор продолжает процесс преобразования в код уровней входных сигналов-. Таким образом, с выхода устройства считывается код адреса входа шифратора с кодом величины ур(жня входных сигналов.; Предлагаемый шифратор позволяет, кроме опреоеяения факта изменения сигнала на его входе, обеспечить фиксирование и преобразование в код уровней входных сигналов, которые появляются на входе шифратора. Формулаизобретения . . . Шифратор по авт. ев, № 59.О825, отличающийся тем, что, с целью расширения области его применения за счет обеспечения возможности преобразования в код уровней сигналов на входах шифратора, он содержит компараторы по чисду ячеек памяти генератор тактов вых импульсов, элемент И, реверсивный счетчик, дополнительный дешифратор и цифроаналоговый преобразователь выход которого подключен к одним из входов компараторов, сругие входы которых являются входами шифратора, а выходы подключены соответственно ко входам ячеек памяти, выход генератора тактовых импульсов подключен к первому входу элемента И, втсфой вход которого соединен с выходом последнего элемента ИЛИ, а выход - с одним из входов реверсивного счетчика, другие выходы которого соединены с выходами дополнительного дешиф атора, вход которого подключен ко входу цифроаналогового преобраз1 вателя и выхоцу реверсивного счетчика, являющемуся одним из выходов шифратора. Источники информации, принятые во внимание при экспертизе I. Авторское свидетельство СССР 59О825, кл. 5 It С 11/06, 1975 (прототий).

Авторы

Даты

1981-11-30—Публикация

1980-02-06—Подача