1

Изобретение относится к импульсной технике и может быть использовано при создании интегральньтх схем (на МП транзисторах).

Известен преобразователь уровней напряжения на дополняющих ОДП транзисторах, содержащий двухтактный инвертор на двух транзисторах, двухтактный повторитель -на двух транзисторах, два форсирующих р -канальных транзистора, два двухвходовых элемента ИЛИ с задержкой по первому входу, входную шину, прямую и инверсную выходные шины ij .

Недостатками этого преобразователя являются использование большого количества транзисторов и наличие шин двух источников питания.

Наиболее близким к предлагаемому по технической сущности является ус ройство согласования уровней напряжения на ЩП транзисторах, содержащее первый р-канальный и первый П -канальный транзисторы, затворы которых соединены с входной шиной и затвором второго П -канального транзистора, истоки - соответственно с шиной питания и общей шиной, а стоки - с истоком второго р -канального транзистора и затвором третьего П -канального транзистора, сток которого соединен с шиной питания, а исток с затвором второго р-канального транзистора, со стоками третьего р -канального и второго П-канального транзисторов и с затворами четвертых р -канального и П-канального транзисторов, стоки которых соединены с выходной шиной, а истоки - соответственно с шиной питания и общей шиной, которая соединена с истоком второго П -канального транзистора и стоком второго р-канального транзистора, исток третьего р -канального транзистора соединен с шиной питания, подложки р-канальных транзисторов соединены с шиной питания, подложки п -канальных транзисторов соединены с общей шиной, а третьего h -канального тра .зистора - с его истоком 21 ,

Недостатком известного устройства согласования уровней напряжения на ШП транзисторах является низкое быстродействие.

Цель изобретения - повьииение бысродействия устройства.

112565г

Поставленная цель достигается тем, что в устройстве согласования уровней напряжения, содержащем первый р -канальный и первый П -каналь5 ный транзисторы, затворы которых соединены с входной шиной и затвором второго и -кансшьного транзистора, истоки - соответственно с шиной питания и общей шиной, а стоки - с 10 истоком второго р -канального транзистора и затвором третьего И -канального транзистора, сток которого соединен с шиной питания, а исток с затвором второго р -канального транJ5 зистора, со стоками третьего р -канального и второго П -канального транзисторов и с затворами четвертых р--ка}1ального и П -канального транзисторов, СТОКИ которых соединены

20 с выходной шиной и затвором третьего р-канального транзистора, а истоки соответственно с шиной питания и общей 1ШНОЙ, которая соединена с истоком второго И -канального тракзис25 тора и стоком второго р -канального транзистора, подложки р -канальных транзисторов соединены с шиной питания, подложки П -канальных транзисторов соединены с общей

30 шиной, а третьего И -канального

транзистора - с его истоком, исток третьего р -канального транзистора соединен с зат.вором третьего И -канального транзистора.

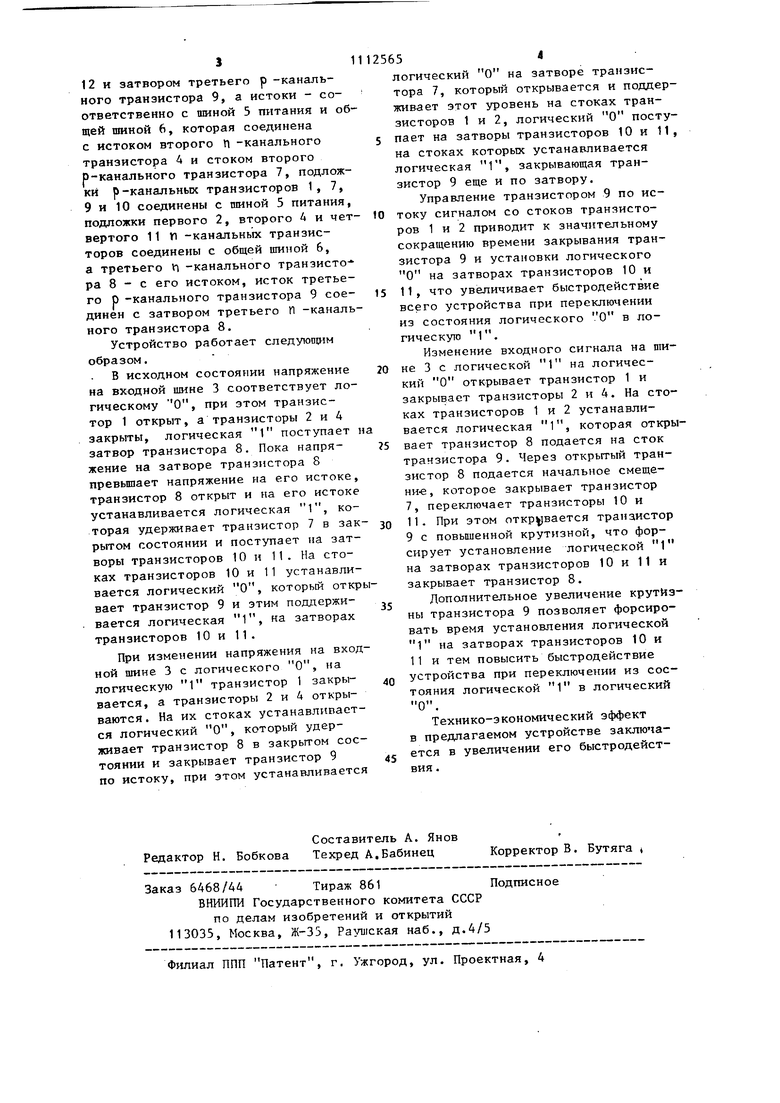

На чертеже представлена электрическая принципиальная схема устройства согласования уровней напряжения на МДП транзисторах.

Устройство согласования уровней

О напряжения, содержит первый р -канальный 1 и первый И -канальный 2 транзисторы, затворы которых соединены с входной шиной 3 и затвором второго П -канального транзис5 тора 4, истоки - соответственно с шиной 5 питания и общей шиной 6, а стоки - с истоком второго р -канального транзистора 7 и затвором третьего -канального транзистора

0 8, сток которого соединен с шиной 5 питания, а исток - с затвором второго р -канального транзистора 7, со стоками третьего р -канального и второго П -канального тран5 зисторов 9 и 4, с затворами четвертьгх р -канального и п -канального транзисторов 10 и 11, стоки которых соединены с выходис й мни;on

| название | год | авторы | номер документа |

|---|---|---|---|

| Кварцевый генератор | 1990 |

|

SU1809936A3 |

| Интегральное устройство для управления вторичным источником питания | 1986 |

|

SU1376186A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| Формирователь импульсов | 1988 |

|

SU1674361A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1985 |

|

SU1345165A1 |

| Преобразователь уровней | 1988 |

|

SU1539991A1 |

| Преобразователь уровней напряжения | 1986 |

|

SU1358088A1 |

| Интегральный компаратор на КМОП-транзисторах | 1988 |

|

SU1552366A1 |

УСТРОЙСТВО СОГЛАСОВАНИЯ УРОВНЕЙ НАПРЯЖЕНИЯ, содержащее первый р -канальный и первый п-канальный транзисторы, затворы которых соединены с входной шиной и затвором второго 11 -канального транзистора, истоки - соответственно с шиной питания и общей шиной, а. стоки - с истоком второго р -канального транзистора и затвором третьего h -канального транзистора, сток которого соединен с шиной питания, а. исток - с затвором второго р -канального транзистора, со стоками третьего р -канального и второго П -канального транзисторов и с затворами четвертых р -канального и И -канального транзисторов, стоки которых соединены с выходной шиной и затвором третьего р -канального тг1нзистора, а истоки соответств. то с шиной питания и общей шино которая соединена с истоком BTi. рого И -канального транзистора и стоком второго р-канального транзистора, подложки р -канальных транзисторов соединены с шиной питания, подложки Ц -канальных транзисторов соединены с общей (/) шиной, а третьего П -канального транзистора - с его истоком, о тличающееся тем, что, с целью повьпаения быстродействия устройства, исток третьего р -канального транзистора соединен с затвором третьего tl -канального транзистора.

| Быстродействующий преобразователь уровней напряжения на дополняющих мдп транзисторах | 1979 |

|

SU790330A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4258272, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-07—Публикация

1983-05-18—Подача