та ИЛИ, а выход первого запоминающего элемента соединен с информационым входом динаьшческого запоминающего элемента, выход которого соединен с первь входом второго триггера и с первым входом первого элемента И, второй вход которого соединен с прямым выходом второго триггера, а выход - с первым входом второго элемента И, с первым информацнонньм входом фазового дискриминатора и с первыми входами элементов И первой и второй групп, вторые входы элементов И обеих групп подключены к выходам задания временных интервалов генератора треугольных развертывающих функций, а их выходы - к соответствующим информационным входам блока .цифровой обработки выходы элементов И первой группы соединены с блокирующими входами соответствукнщх элементов И второй группы, группа информационных выходов блока цифровой обработки соединена с группой соот ветствующих входов блока контроля итераций, первый выход оценки итерации которого соединен с первым разрешающим входом блока цифровой обработки, второй выход оценки итерации соединен с вторым разрешающим входом блока цифровой обработки и с первым входом третьего триггера, третий выход оценки итерации блока контроля итераций соединен с вторьм входом третьего триггера, выход которого соединен с вторьм входом второго элемента И и с входсм управления преобразованием фазы в напряжение фазового Дискриминатора, выход вто.рого элемента И соединен с вторым входом второго триггера, с входом расщирителя импульсов и с входом счетчика ит,ераций, выход которого соединен с входом окончания вычислений блока цифровой обработки, выход расширителя импульсов соединен с управляющим входом второго за поминающего элемента, информационный вход которого соединен с выходом .фазового дискриминатора, а вы ход - с вторым информационным входом фазового дискриминатора, задаюЩИЙ вход которого подключен к СООТ

ветствующему выходу генератора треугольных развертывающих функций, вход задания режима функционального преобразования преобразователя.

3818

соединен с управляющими входами масштабирующего генератора ступенчатого напряжения и генератора ступенчатого напряжения, а вход запуска преобразователя соединен с третьим входом компаратора.

2.Преобразователь по п. 1, -о тличающийся тем, что, с целью повьшения точности за счет компенсации нелинейных искажений входного сигнала, он содержит линеаризующий генератор, управляющий вход которого соединен с входом задания режима функционального преобразования преобразователя. Синхронизирующий вход - с выходом генератора импульсов, первый- выход с выходом масштабирующего генератора ступенчатого напряжения, второй выход - с выходом генератора ступенчатого напряжения.

3.Преобразователь по п. 1, отличающийся тем, что блок цифровой обработки содержит сумматор, реверсивный сумматор, элемент И, две группы элементов ИЛИ,р триг герое и две группы элементов И, при первые и вторые входы И элементов ИЛИ первой группы являются информационньво входами блока, первые входы п элементов ШШ первой группы соединены с соответствующими входами сумматора, первьй и второй выходы которого,соединены со знаковыми входами реверсивного сумматора, выходы элементов ИЛИ первой группы соединены с первыми входами соответствующих триггеров, прямые выходы которых образуют группы информационных выходов блока и соединены с первыми входами соответствующих элементов И первой и второй групп, (Вторые входы элементов И первой группы соединены с шинами задания констант блока, а выходы соединены с первой группой информационных входов реверсивного сумматора, вход окончания вычислений блока соединен с управляющим входом элемента И, с вторым входом tt -го триггера и является одним из выходов группы информационных . выходов блока, второй

вход каждого -го триггера ( ) соединен с первым входом (i - 1)-го элемента ИЛИ второй rpynnbif второй вход которого соединен с выходом соответствующего элемента И второй группы, а выходы

элементов ИЛИ второй группы соединены с вторыми входами соответствующих триггеров, вторые входы элементов И второй группы подключены к первому разрешающему входу бло ка, управляющий вход реверсивного сумматора соединен с вторым разрешаюпщм входом блока, синхронизирующий вход реверсибного сумматора является синхронизирующим входом блока, управляющий вход реверсивного сумматора является управляющим входом блока, выход реверсивного сумматора через элемент И соединен с выходом блока.

4, Преобразователь по п. 1, отличающийся тем, что блок .контроля итераций содержит группу элементов И, элемент И, элемент НЕ, два элемента ИЛИ, группу элементов ИЛИ и П триггеров, при этом первые входы элементов И группы и соединенные между собой первые входы п

113818

триггеров образуют группу входов блока, выходы п триггеров соединены с вторыми входами соответствую щих элементов И группы, выходы которых соединены с соответствующими входами первого элемента ИЛИ, выход которого является вторым оценочным выходом блока и через элемент НЕ соединен с первым входом элемента И, первые входы элементов И группы соединены с соответствующими входами второго элемента ИЛИ, выход которого, являющийся первым оценочным выходом блока, соединен с вторьм входом элемента И, выход которогб (Является третьим оценочным выходом Яблока, выход каждого (-го элемента И группы ( Г7п ) соединен с соответствующими входами элементов ИЛИ группы с первого по -и, выходы которых соединены с вторыми входами соответствующих п триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ И ПОДАВЛЕНИЯ ФИЗИЧЕСКИХ ПРОЦЕССОВ (ПОЛЕЙ) ОКРУЖАЮЩЕЙ СРЕДЫ САМОНАСТРАИВАЮЩИМСЯ ОПОРНЫМ ПРОЦЕССОМ (ПОЛЕМ) | 2008 |

|

RU2391678C2 |

| Устройство для решения инверсных задач нестационарной теплопроводности | 1983 |

|

SU1179388A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| Цифровой анализатор спектра | 1980 |

|

SU900210A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1520659A1 |

| Устройство для сжатия данных | 1981 |

|

SU1012313A1 |

| Масштабирующий преобразователь | 1982 |

|

SU1038880A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| Программируемый преобразователь напряжения произвольной формы в напряжение требуемой формы | 1990 |

|

SU1711303A1 |

| Цифровой интегратор | 1978 |

|

SU739567A1 |

1. АНАЛОГО-ЦИФРОВОН ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий компаратор, первый вход которого является входом преобразователя, блок цифровой обработки, выход которого соединен с вторым входом компаратора, генератор импульсов и блок управления, первый выход которого соединен с управляющим входом блока цифровой обработки, отличающийся тем, 4ТО, с целью повышения быстродействия, точности и помехозащищенности, преобразователь содержит два запоминаю цих элемента, динамический запоминающий элемент, фазовый дискриминатор, двухполярный аналоговый ключ, две группы из п элементов И, два элемента И, блок контроля итераций, масштабирующий генератор ступенчатого напряжения, генератор ступенчатого напряже1 ия, генератор треугольных развертывающих функций, а блок управления содержит три триггера, элемент ИЛИ, счетчик итераций и расширитель импульсов, при этом входы синхронизации масштабирующего генератора ступенчатого напряжения, генератора ступенчатого напряжения, блока цифровой обработки и генератора треугольных развертывающих функций подключены к выходу генератора импульсов и к тактирующим входам динамического запоминающего элемента и фазового дискриминатора, вход задания развертывающего напряжения которого соединен с выходом генератора ступенчатого напряжения и с первым входом пвухполярного аналогового ключа, выход масштабирующего генератора ступенчатого напряжения соединен с вторым входим двухполярного аналогового ключа, первый и второй управляющее входы которого соединены соответственно с прямым выходом первого триггера, яв00 ЛЯЮ1ЦИМСЯ первым выходом блока управления, и с инверсным выходом первого триггера, а выход двухполярноСХ) го аналогового ключа - с первым и вторым входами задания развертывающего напряжения динамического запоминающего элемента, первый выход компаратора соединен с первыми входами первого триггера и элемента ИЛИ, второй выход компаратора соединен с вторыми входами первого триггера и элемента ИЛИ, И 1формащ1онный вход первого запоминающего элемента соединен с входом преобразователя, управляющий вход - с выходом элемен

Изобретение относится к аналогоцифровому функциональному преобразованию электрических величин и может быть использовано в информационно-измерительной и вычислительной технике.

Известны устройства аналого-цифрового преобразования с повышенным быстродействием, использующие итерационные преобразования ll.

Недостаток известных устройств сравнительно медленная сходимость итерационного процесса.

Наиболее близким техническим решением к предлагаемому является устройство аналого-цифрового преобразования, содержащее схему сравнения (компаратор), соединенную входами с входом устройства и с выходом компенсационной схемы, а выходом - с входом измерительного усилителя, выход которого соединен с первыми входами группы сумматоров и с входом блока ввода поправок выход которого соединен с первым

входом компенсационной схемы и с информационным входом блока цифровой обработки, блок управления, соответствующие выходы которого соединены с управляющим входом блока ЦИФРОВОЙ обработки, с синхронизирующим входом блока запоминающих регистров и с управляющим входом ключа, два резистивных делителя, соединенных через ключ и непосред ственно с шиной опорного напряжения, причем выходы первого делителя соединены с вторыми входами группы сумматоров, а выходы второго делителя - с первыми входами группы пороговых элементов, вторые входы которых соединены с выходами соответствующих сумматоров, а выходы - с входами блока запоминающих регистров, выходы которого соединены с цифровым входом блока цифровой обработки и с вторьгм входом компенсационной схемы 2.

Указанное устройство реализует нониусный итерационный способ аналогцифрового преобразования напряже3

ния в код, применение которого значительно увеличивает время преобразования и усложняет аппаратурное решение.

Цель изобретения - повьшение быстродействия, точности и помехозащищенности, а также дополнительное повышение точности за счет компенсации нелинейных искажений входного сигнала.

Цель достигается тем, что аналого-цифровой функциональный преобразователь, содержа11а1й компаратор, первый вход которого является входом преобразователя, блок цифроврй обработки,.выход которого соединен с вторым, входом компаратора, генератсч) импульсов и блок управления, перв выход которого соединен с управляющим входом блока цифровой обработки, содержит два запоминающих элемента, динамический запоминаюв(ий элемент, фазовый дискриминатор, двухполярный ад1алоговый ключ, две группы из п элементов И, два элемента И, блок контроля итерагщй, масштабирующий генератор ступенчатого напряжения, генератор ступенчатого напряжения, генератор треугольных развертывающих функций, а блок зшравления содержит три триггера, элемент ИЛИ, счетчик итераций и расширитель импульсов, при этом входы синхронизации масштабирующего генератора ступенчатого напряжения, генератора ступенчатого напряжения, блока цифровбй обработки и генератора треугольных развертываннцнх функций подключены к выхо ду генератора импульсов и к тактирующим входам динамического запоми.нающего элемента и фазового дискриNoiHaTopa, вход задания развертывающего напряжения которого соедине с выходом генератора ступенчатого напряжения и с первым входом двухполярного аналогового ключа, выход масштабирующего генератора ступенчатого напряжения соединен с вторым входом двухполярного аналогового ключа, первый и второй управляющие входы которого соединены соответствейно с прямым выходом первого триггера, являющимся первьм выходом блока управления, и с инверсным выходом первого триггера, а выход двухполярного аналогового ключа - с пер184

вым и вторым входами задания развертьтающего напряжения динамического запоминающего элемента, первый выход компаратора соединен с первыми входами первого триггера и элемента ИЛИ, второй вьпсод компаратора соединен с вторыми входами первого триггера и элемента ИЖ, информаЩ1ОННЫЙ вход первого запоминающего

элемента соединен с входом преобразователя, управляюпщй вход - с выходом элемента ИЛИ, а выход первого запоминающего элемента соединен с информационным входом динамического запоминающего элемента, выход которого соединен с первым входом второго триггера и с первым ёходом первого элемента И, второй вход которого соединен с прямым выходом

второго триггера, а выход - с первым входом второго элемента И, с первым информационным входом фазового дискриминатора и с первыми входами элементов И первой и второй

групп, вторые входы элементов И обеих групп подключены к выходам задания временных интервалов генератора тре;угольных развертывающих функций, а их выходы - к соответствующим ин|форма1ронным входам блока цифровой обработки, выходы элементов И первой группы соединены с блокирующими входами соответствующих элементов И второй группы, группа информационных выходов блока цифровой обработки соединена с г руппой соответст- . вующих входов блока контроля итера- . ций, первьлй выход оценки итерации которого соединен с первым разрешающкм входом блока цифровой обработ ки, второй выход оценки итерации соединен с вторым разрешающим входом блока цифровой обработки и с первым входом третьего триггера,

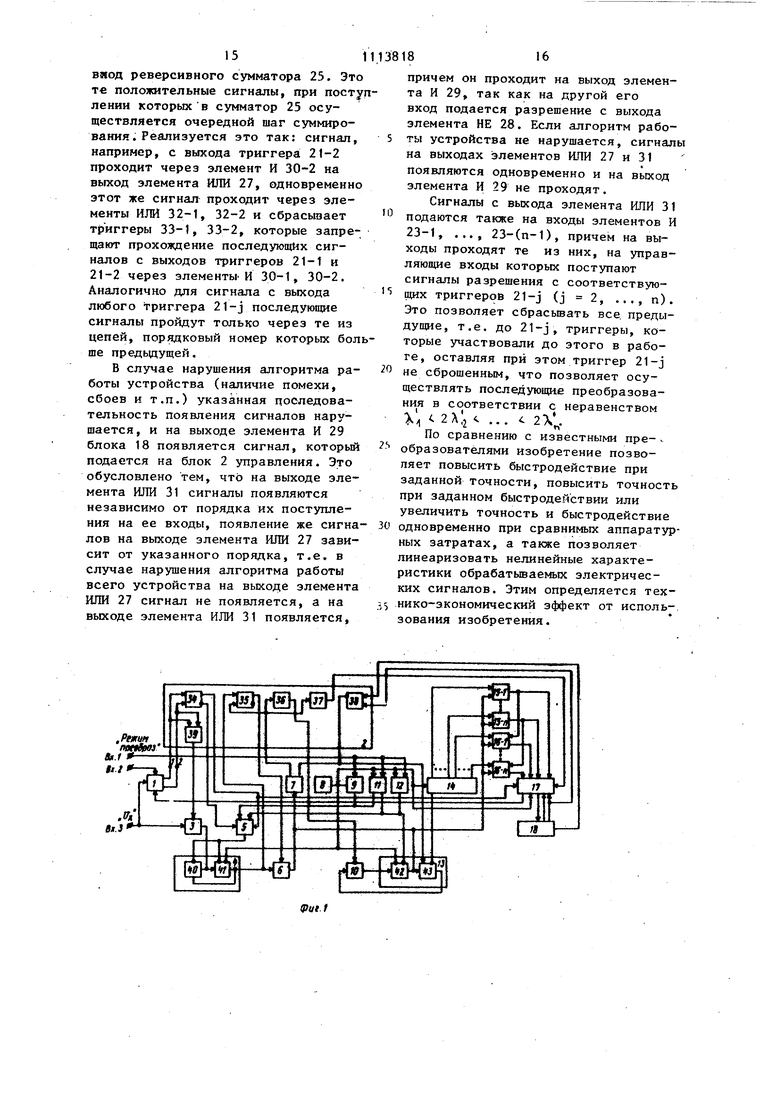

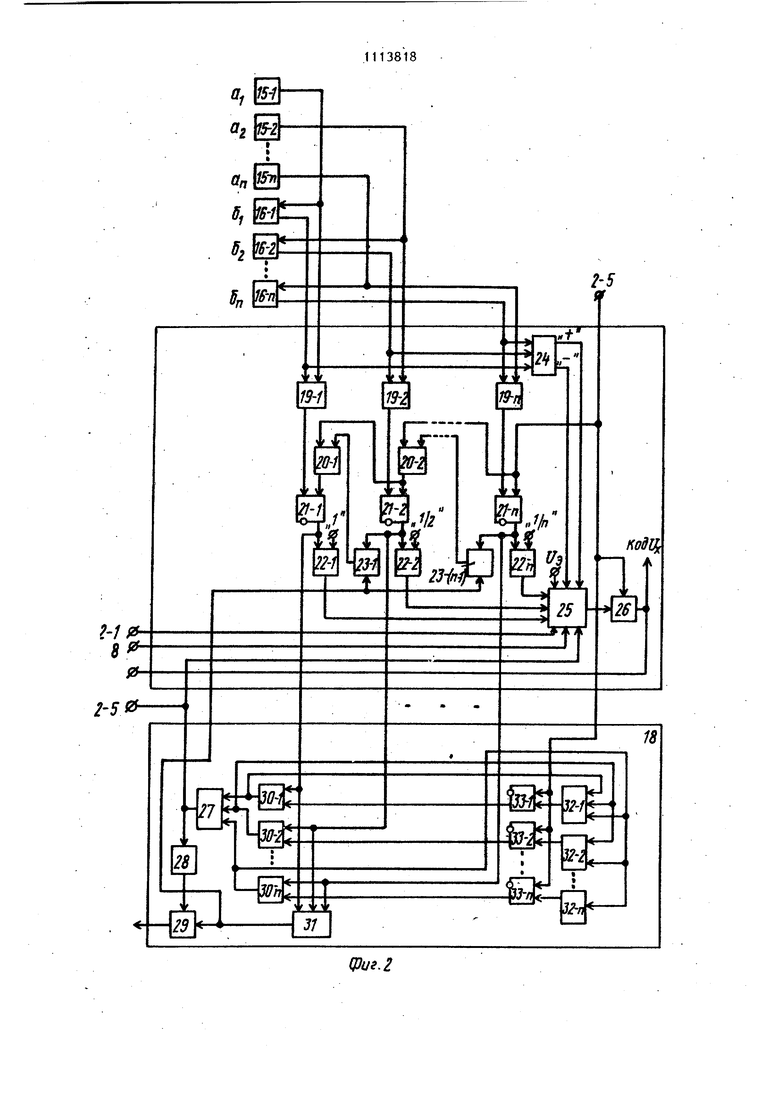

тpetий выход оценки итерации блока контроля итераций соединен с вторым входом третьего триггера, выход которого соединен с вторым входом второго элемента И и с входом управления преобразованием фазы в напряжение фазового дискриминатора, выход второго элемента И соединен с вторым входом второго триггера, с входом расширителя импульсов и с входом счетчика итераций,выход которого соединен с входом окончания вычислений блока цифровой обработки, выход расширителя импульсов соединен с управляющим входом второго запоминающего элемента, информационный вход которого соединен с выходом фазового дискриминатора, а выход - с вторым информационным входом фазового диск риминатора, задающий вход которого подключен к соответствующему выходу генератора треугольньк развертывающих функций, вход задания режима функционального преобразования преобразователя соединен с управляющими входами масштабирующего генера тора ступенчатого напряжения и гене ратора ступенчатого напряжения, а вход запуска преобразователя соединен с третьим входом компаратора. Кроме того, преобразователь содержит линеаризующий генератор, управляющий вход которого соединен с входом задания режима функциональ ного преобразования, синхронизируихций вход - с выходом генератора .импульсов, первый выход - с выходом масштабирующего генератора ступенчатого напряжения, второй выход с выходом генератора ступенчатого напряжения. Блок цифровой обработки содержит су Ф«атор, реверсивный сумматор, эле мент И, две группы элементов ИЛИ, п триггеров и две группы элементов И, при этом первые и вторые входы п элементов ИШ первой группы являются информационными входами блока, первые входы П элементов ИЛИ первой группы соединены с соответствуюгцими входами сумматора, первый и второй выходы которого соединены со знаковыми входами реверсивного сумматора, выходы элементов ИЛИ первой группы соединены с первьп и входами соответствующих триггеров, прямые выходы которых образуют группы информационных выходов блока и соеди нены с первыми входами соответствующих элементов И первой и второй групп, вторые входы элементов И первой группы соединены с шинами задания констант блока, а выходы соединены с первой группой информационных входов реверсивного сумматора, вход окончания вычислений блока соединен с управляющим входом элемента И, с вторым входом п -го триггера и является одним из выходов группы информационных выходов блока, второй вход каждого i-ro 18 триггера ( I 2,ii ) соединен с первьм входом ( - 1)-го элемента ИЛИ второй группы, второй вход которого соединен с выходом соответствующего элемента И второй группы, а выходы элементов ИЖ второй группы соединены с вторыми входами соответствующих триггеров, вторые входы элементов И второй группы подключены к первому разрешакицему входу блока. Управляющий вход реверсивного сумматора соединен с вторым разрешающим входом блока, синхронизирующий вход реверсивного сумматора является синхронизирующим входом блока, управляющий вход реверсивного сумматора является управляющим входом блока, выход реверсивного сумматора через элемент И соединен с исходом блока. Блок контроля итераций содержит группу элементов И, элемент И, элемент НЕ, два элемента ИЖ, группу элементов ИЛИ и п триггеров, при этом первые входы элементов И группы и соединенные между собой первые входы п триггеров образуют группу входов блока, выходы П триггеров соединены с вторыми входами соответствую1дах элементов И группы, выходы которых соединены с соответствунлцими входами первого элемента ИЛИ, выход которого является вторым оценочным выходом блока и через элемент НЕ соединен с первым входом элемента И, первые входы элементов И группы соединены с соответствующими входами второго элемента ИЛИ, выход которого, являющийся первым оценочным выходом блока, соединен с вторым входом элемента И, выход которого является третьим оценочньм выходом блока, выход каадого i-ro элемента И группы ( i 1,п ) соединен с соответствующими входами элементов ИЛИ группы с первого по i -и, выходы которых соединены с вторыми входами соответствующих п тригге- : ров. Предлагаемое устройство реализует алгоритм, изложенный в З. На фиг. 1 приведена схема аналогоцифрового многофункционального преобразователя; на фиг. 2 - пример реализации блоков контроля итераций и цифровой обработкиj на фиг. 3 временные диаграммы. Преобразователь содержит кокшара тор 1, блок 2 управления, запоминаю щий элемент 3,- динамический sanoteiнающий элемент 4, двухполяршлй анал говый ключ 5, элементы И 6 и 7, генератор импульсов 8, масштабирующий генератор ступенчатого напряжения (МГСН) 9, запоминающий элемент 10, линеаризующий генератор 11, генератор ступенчатого напряжения (ГСН) 1 дискриминатор 13, генератор 14 треугольных развертывающих напря жений, элементы И 15 и 16, блок 17 цифровой обработки и блок 18 контро ля итераций. В варианте выполнения (фиг. 2) блок 17 1Р1ФРОВОЙ обработки содержит элементы ИЛИ 19 и 20, триггеры 21, элементы И 22 и 23, сумматор 24, реверсивный сумматор 25, элемент И 26, а блок 18 контроля итерадай элементы ШШ 27, НЕ 28, И 29 и 30, ШМ 31, 32, триггеры 33. Елок 2 управления содержит триггеры 34 и 35, распйиритель 36 импул1{Сов, счетчик 37 итераций, триггер 38, элемент ИЖ 39. Элемент 4 содержит преобразователь 40 фазы в напряжение и преобразователь 41 напряжения в фазу, а фазовьй дискриминатор 13 масштабный преобразователь 42 напря жения в фазу и масштабный преобразо ватель 43 фаза-напряжение. Фазовый дискриминатор 13 вшюлнен на базе многозначного потенциал ного элемента, описанного в L4. Преобразователь работает следующим образом. Величина измеряемого напряжения представляется в нем в виде . н; u г,,: . : пссЧ -г,)Г а Ч;яг 1А,..д Развертывающие базисные напряжения с вшсодов генераторов 9. 12 и 14, соответственно SDJy, SD, .SD представляют собой дискретно изменяющиеся во времени и по уровню функции временного аргумента с периодом Т, синхронизируемые импульсами генератора 8. Максимальное базисное напряжение с выхода ген 12 равно эталонной величине U и выражается зависимостью Т KjjU, максимальное базисное напряжение с выхода МГСН 9 равно lUg, где - масштабный Kqэффициент, и выражается зависимостьюП 1У УП Развертывающее базисное напряжение с выхода генератора 14 записывается на интервале (О, Т„) в виде (фиг. 3) )(« « I (ч i-illliadL /l-W (L l иг -от- тг где о, 1 , 2, t - текущее время при условии, . Работа устройства осуществляется в два этапа на примере преобразования мгновенного значения напряжения некоторого электрического сигнала Ujt в код (фиг. 3). Во время первого этапа по сигнаг лу Пуск (Вх. 2) текущее значение и компаратором 1 сравнивается с Uj, на основании результатов сравнения блок 2 управления (сигнал на выходе элемента ШШ 39) вь5)абатывает команду запоминания в динамическом запоьшнакэдем элементе 4 соответствующего значения напряжения и одновременно, в засивимости от знака разности У и Ua , т.е. J идИли и и, команду на двухполярпь1й ключ 5, который коммутиру- ет соответственно базисное напряжение с МГСН 9 или ГСН 12 на вход элемента 41. Элемент 3 обеспечивает хранение информации на время не больше Т (фиг. 3), необходимое для ее запоминания в динамическом запоминающем элементе 4. Процесс запоминания осуществляется в таком порядке. Выбранное напряжение (и,) с выхода элемента 3 в момент его равенства величине развертывающего базисного напряжения, поступающего с МГСН 9 или ген 12, преобразуется в преобразователе 41 в дискретный сигнал соответствующей фазой D;j(De) (в дальнейшем просто фазу), определяемой базисом D с генератоа ГИ 8. Фаза D(D) в соответствующий ей момент времени по цепи обратной связи осуществляет в преобразователе 40 выборку из базисного напряжения соответствующего уровня сигнала, Точность запоминания значения UH ( ) определяется числом состояний (значностью) элемента 4, которое определяется отношением частот генератора ГИ 8, МГСН 9 и ген 12.

; (з)

; « ft л

IklM IV4 f

Фаза D(Dj) запомненного напряжения и (U)ti) с выхода преобразователя 41 поступает на триггер 35, который разрешает ее прохождение через элемент И 6 на вход преобразователя 43. Кроме -этого, указанная

фаза с выхода элемента И 6 через элемент И 7 сбрасывает триггер 35

в исходное состояние. Фазы D , D, напряжений , соответствуют

выражениям

Т)л к,иг , Ъг 1 Uxi .

Для простоты фазы D и D на фиг. 3 изображены одинаковыми.

Последующие действия осуществляются в устройстве для обоих случаев одинаково. Фаза D(D) преобразуется в преобразователе 43 в соответствующий уровень напряжения и , задаваемый развертывающим базисным напряжением с генератора 14 (фиг. 3), причем величина этого уровня соответствует первому меньшему остатку, который получился бы при укладывании величины напряжения и в эталонную меру U, с избытком или недостатком, т.е. функция, реализуемая базисным напряжением 55,, обеспечивает итерационное преобразование по алгоритму

и. F(D),

(3)

где D - фаза, соответствующая D

или D..

Одновременно с развертывающим напряжением генератор 14 вырабатывает также временные интервалы, соответствующие значениям аргумента при оценке с избытком или недостатком (на фиг. 3 это интервалы соответственно а и 5 (у 1, 2, ... которые подаются на входы элементов И 16-1, Т.. 16-п (интервалы

«Г,) , 15-1, ..., 15-п (интерэалы а, ..., а), где п - количество интервалов, соответствующее количеству схем совпадения) .

На другие входы элементов И 15 и 16 Подается фаза D(D«) преобразованного значения аргумента U(U), причем, если фаза прошла через эле.мент 15-i, то элемент 16-i на время ею блокируется, т.е. осуществляется помехозащита от неинформативного сигнала на границе двух интервалов d и rf , поскольку фаза имеет определенную длительность и может перекрывать два соседних временных интервала. На этом первый этап итерационного преобразования закаН чивается.

Во время второго этапа итерационные преобразования осуществляются уже не с входным напряжением (Uj4 ), а с последовательно получаемыми в виде напряжений остатками (начиная с U ). Остаток V с выхода преобразователя 43 по сигналу с выхода элемента И 6 через элемент И 7 и расширитель 36 подает-ся на запоминающий элемент 10 и далее на вход преобразователя 42, где в соответствии с развертывающим базисным напрзотением с ГСН 12 преобразуется в фазу Dj

)i

Расширитель 36 слуткит для обеспечения надежной работы элемента 10, назначение которого аналогично

элементу 3, т.е. хранения поступающей информащ1И в течение времени, необходимого для обработки ее преобразователем 42.

Фаза D,j, в свою очередь, преобразуется преобразователем 43 в уровень напряжения U , соответствующий второму меньшему остатку, и так далее до величины остатка, удовлетворяющей требуемой точности преоб разования Vf. (Uxi )

UK, F(,LF(D:)J.

На фиг. 3 преобразуемые остатки и , uj объединенные стрелками,

изображены на графике для второго

случая (U.i })) ,

Последовательно полученные фазы D;, , DJ, DJ, ... проходят, как было описано, на выходы тех эле55 ментов И 15-i, 16-i, где произошло их совпадение с соответствующими временными интервалами, задаваемыми с выходов генератора 14. и На основании сигналов с выходов элементов И, соответствующих значе ;ентов и, соответствующих значе Ь 2. ...)/при. ниям ВИИ, что г о с + (1 -6о) и условии значениям эталонной величины Ц, в блб1се 17 цифровой обработки по команде счетчика 37 после определен ного количества итераций, задаваемо го в соответствии с требуемой точностью преобразования, и положитель .ного сигнала с выхода блока контроля итераций 18, предназначенного для контроля реализуемого алгоритма после каждого шага итерационного пр образования, вычисляется цифровой зквивалент величины входного сигнал причем для случая U вычисление осуществляется в соответствии с выражением (1), а для случая и, полученное значение умножают еще на коэффициент J4. Положительньй сигнал вырабатывается врезультате последовательного сравнения полученных в процессе итерационного преобразования величинХ ( t, 2. ..,), связянных зависимостями Х 2%L ,.. i2X В противном случае соответствующий шаг итерационного преобразования повторяется, т.е. предыдущий остаток (напряжение) опять преобразуется в соответствующую фазу. Осуществ ляется это так. Указанный положительный сигнал с блока 18 контроля не вырабатьюается и не подтверждается сброс триггера 38, с другого же выхода блока 18 контроля вырабатывается сигнал, поступающий на дру гой вход триггера 38, который, в свою очередь, запрещает работу прег образователя 43 и прохождение через элемент И 7 соответствующей фазы с выхода преобразователя. В результате упомянутая фаза не засчитывается в счетчике 37 и не проходит на запоминающий элемент 10, т.е. в нем информация не обновляется и осуществляется повторное преобразование предыдущего полученного остат ка в фазу. Для реализации в предлагаемом устройстве, в частности в дискрими наторе 13, описанных взаимообратных преобразований абсолютные максимальные величины Т и Uj (Т| KijUj) должны бьггь эквивалентны и приравнены условно к единице. В этом случае значения функции по t8 оси ординат будут задавать величины остатков в виде напряжений U,t. ( 1 2, ...), а временные значения аргумента по оси абсцисс - величины 1/Л-.( и значения равные О ипи 1 в зависимости от попадания соответственно вовреьШт..о« 427Г1Т менные интервалы (S) 1, 2, ...) ил„(т,.;1., Возможные величины 1/л.л при Т 1 и 1, 2, ... могут быть занесены в блок 17 в виде ряда констант 1, 1/2, 1/3, 1/4, ..., которые соответствуют точкам пересечения оси абсцисс прямыми реализуемой функции (фиг, 3). Работа блока 17 синхронизируется импульсами с га 8. Принятое итерационное преобразование позволяет за небольшое количество итераций получить достаточно высокую точность преобразуемой в код величины 11,; (U) . Кроме этого, предлагаемое устройство итерационногб преобразования позволяет оценить исследуемую величину с точностью большей, чем дискретность эталонной величины. Все итерационные преобразования, за исключением первого, осуществляются с последовательно получаемыми остатками и эталонной величиной, что позволяет хранить информацию о каждом остатке, начиная с ), в течение одного шага итерационно го преобразования и, следовательно, измерять мгновенные значения исследуемой величины U)(. Предлагаемое устройство позволяет также контролировать итерационный процесс, т.е. обеспечивает помехозащиту за счет сравнения получаемых целых чисел Л ( 1, 2, ...) со значениями, связанньми зависимостями X i2Xlj ... 2Х„или V -2 (V 1, 2, ...). Преобразования, реализуемые описанным устройством, всецело определяются функциями развертывающихбазисных напряжений, т.е. изменение этих функций позволяет изменить и ре шизуемые устройством алгоритмы (режим преобразования). Так, сли на элемент 4 и фазовьй дискриминатор 13 в соответствующих случаях по

13

сигналу с Вх. 1 (режим преобразования) вместо базисных напряжений и SD, подать с вспомогательного ЛГ 11 развертывающие базисные напряжения SD| t F() и t| F««(-) (фиг. 3); позволяющие, например, линеаризовать характеристику некоторого первичного преобразователя электрических и неэлектричедких величин (например температуры), то с помощью предложенного, устройства можно обрабатывать выходные- сигналы с подобных нелинейных преобразователей.

В конце преобразования, т.е. после вычисления цифрового эквивалента, с блока 17 на. компаратор 1 поступает сигнал, разрешающий пов торный запуск преобразователя. При соответствующей расстановке сигналой Пуск указанным устройством могут также успешно обрабатываться энергетические параметры переменных электрических сигналов - действующее значение, мощность.

Работа блоков 17 и 18 осуществляется следующим образом.

Сигналы с выходов элементов И 15-1, ..., 15-п и 16-1, ..., 16-п (фиг. 2), соответствуют1 значениям -1 Выбирают эти значения в блоке 17 из ряда постоянно заданных (например, в виде числа импульсов) констант 1, 1/2, ..., 1/п.

Указанные сигналы через элементы ИЛИ 19-J (J 1, 2, .... п) подаются на установочные входы соответствующих триггеров 21-J, которые разрешают прохождение через элементы И 22-J (J 1, 2, ...) соответствующих констант. Последние подаются на реверсивный сумматор 25, где (после получения положительного сигнала с блока контроля 18) в соответствии с присвоенным им знаком , суммируются. Знаки слагаемых определяются с помощью сумматора 24, который подсчитывает сигналы с выходов схем совпадения 16-j (фиг. 1 и 2 Г), так как попадание в соответствующую зону С отвечает оценке с недостатком и

Сумматор 24 каждьп раз вьздает сигналы признака четности (+) или нечетности (-) полученной суммы. Сигналы с выходов сумматора 24 осуществляют переключение сумматора 25 на сложение или вычитание

последовательности констант 1 /А. поступающих на его входы.

После заданного количества итераций по команде со счетчика 37, 5 поступающей на управлягаций вход элемента И 26, на его выходе получают вычислительный цифровой эквивалент (код и ) величины входного сигнала. По этой же команде осу10 ществляется сброс в исходное состояние триггеров 21 и 33, первые из них сбрасываются через элементы ИЛИ 20, при этом запрещается прохождение констант на выходы элементов

5 и 22, вторые, наоборот, разрешают прохождение очередных сигналов с выходов триггеров на выходы элементов И 30. Получение цифрового эквивалента на выходе элемента И, в

20 свою очередь, служит командой разрешения начала следующего измерения.

Функционирование блока контроля итераций 18.

25 Как следует из приведенного описания, положительные сигналы вьфабатываются блоком 18 в результате pro функционирования в соответствии с приведенным неравенством

30 2X,t...i2 Х„ , которое технически может быть реализовано кос-, венно, исходя из позиционных признаков появления сигналов на выходе соответствующих элементов и 15-j,

35 t6-j,. В результате последовательно гл сравнения остатков с разверткой ФГ (DS) и получения соответствующих им фаз последние, если не происходит сбоев в работе всего

40 устройства, постепенно сдвигаются к началу указанной развертки (DSi).

В соответствии с получаемыми фа- зами сигналы на выходах элементов И 15-1, ..., 15-п, 16-1, .... 16-п сдвигаются в таком же порядке, т.е. в порядке возрастания их нумерации.

Сигналы с выходов триггеров 21-j поступают на соответствующие входы элемента ИЛИ 31 и входы элементов И 30, на управляющие входы которых подаются сигналы разрешения с выходов триггеров 33. Если сигналы на выходах триггеров 21-1, 21-2, .... 21-п появляются в порядке возрастания нумерации, то они проходят через упомянутые элементы И на выход элемента ИЛИ 27 и далее на 15 виод реверсивного сумматора 25. Это те положительные сигналы, при посту лении которыхв сумматор 25 осуществляется очередной шаг суммирования . Реализуется это так: сигнал, например, с выхода триггера 21-2 проходит через элемент И 30-2 на выход элемента ИЛИ 27, одновременно этот же сигнал проходит через элементы ИЛИ 32-1, 32-2 и сбрасывает триггеры 33-1, 33-2, которые запрещают прохождение последующих сигналов с выходов триггеров 21-1 и 21-2 через элементыИ 30-1, 30-2. Аналогично для сигнала с выхода любого триггера 21-j последующие сигналы пройдут только через те из цепей, порядковый номер которых бол ше предьщущей. В случае нарушения алгоритма работы устройства (наличие помехи, сбоев и т.п.) указанная последовательность появления сигналов нарушается , и на выходе элемента И 29 блока 18 появляется сигнал, который подается на блок 2 управления. Это обусловлено тем, что на выходе элемента ИЛИ 31 сигналы появляются независимо от порядка их поступления на ее входы, появление же сигна лов на выходе элемента ИЛИ 27 зависит от указанного порядка, т.е. в случае нарушения алгоритма работы всего устройства на выходе элемента ШШ 27 сигнал не появляется, а на вьсходе элемента ИЛИ 31 появляется. 8 причем он проходит на выход элемента И 29, так как на другой его вход подается разрешение с выхода элемента НЕ 28. Если алгоритм работы устройства не нарушается, сигналы на выходах элементов ИЛИ 27 и 31 появляются одновременно и на вькод элемента И 29 не проходят. Сигналы с выхода элемента ИЛИ 31 подаются также на входы элементов И 23-1, ..., 23-(п-1), причем на выходы проходят те из них, на управляющие входы которых поступают сигналы разрешения с соответствующих триггеров 21-j (j 2, ..., n). Это позволяет сбрасьюать все предыдущие, т.е. до 21-j, триггеры, которые участвовали до этого в работе, оставляя при этом триггер 21-j не сброшенным, что позволяет осуществлять последующие преобразования в соответствии с неравенством :) 2Х;2 ... i 2Х. По сравнению с известными преобразователями изобретение позволяет повысить быстродействие при заданной точности, повысить точность при заданном быстродействии или увеличить точность и быстродействие одновременно при сравнимых аппаратурных затратах, а также позволяет линеаризовать нелинейные характеристики обрабатьшаемых электрических сигналов. Этим определяется технико-экономический эффект от исполь-. зования изобретения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь средней частоты в код | 1977 |

|

SU660245A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| и др | |||

| Универсальный многозначный элемент | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Физико-механический институт АН СССР | |||

| Киев, Наукова думка, 1975. | |||

Авторы

Даты

1984-09-15—Публикация

1982-10-28—Подача