Изобретение относится к вычислительной технике, в частности к устройствам тестового контроля логических схем: типовых элементов замены ЭВМ, схем цифровых приборов, больших интегральных схем и т. д.

Известны устройства для тестового контроля, содержащие блок входных сигналов, блок эталонных выходных сигналов, схему сравнения, блок ввода данных, блок коммутации, схему индикации неисправностей, блок управления.

Цель изобретения - улучшение качества контроля на максимальной рабочей частоте.

Это достигается тем, что в устройство дополнительно введены блок контролируемых выходов, выполненный в виде магазинного запоминаюшего устройства переменного объема, и блоки контрольных регистров. Выход блока контролируемых выходов подключен к второму входу схемы сравнения, один вход - к выходу блока ввода, другой - к выходу блока управления. Вход одного блока контрольных регистров подсоединен к выходу блока входных и эталонных выходных сигналов, а вход другого - к выходу блока контролируемых выходов. Одни выходы блоков контрольных регистров подключены к соответствующим входам блока индикации, другие - к входам блока управления, управляющие входы - к выходам блока управления, а входы сравнения - к соответствующим выходам блока ввода.

Предлагаемое устройство позволяет проводить контроль работоспособности логической схемы при проверке элементов схемы на переключение из состояния «о в состояние «1 и наоборот.

Для осуществления проверки схемы на переключение вводят оператор переключения. Если при изменении входных сигналов на входах элемента элемент изменяет сигнал на выходе с «1 на «О, выходу приписывается прямое переключение, а при обратном изменении сигналов - обратное переключение.

Тест для неисправности рассматривают как последовательность тестовых наборов, при подаче которой переключение сигналов, по крайней мере, одного контролируемого выхода исправной схемы отличается от переключения сигналов контролируемого выхода схемы с неисправностью.

При построении теста используют формализованный метод построения тестов, основанный на нахождении чувствительного пути.

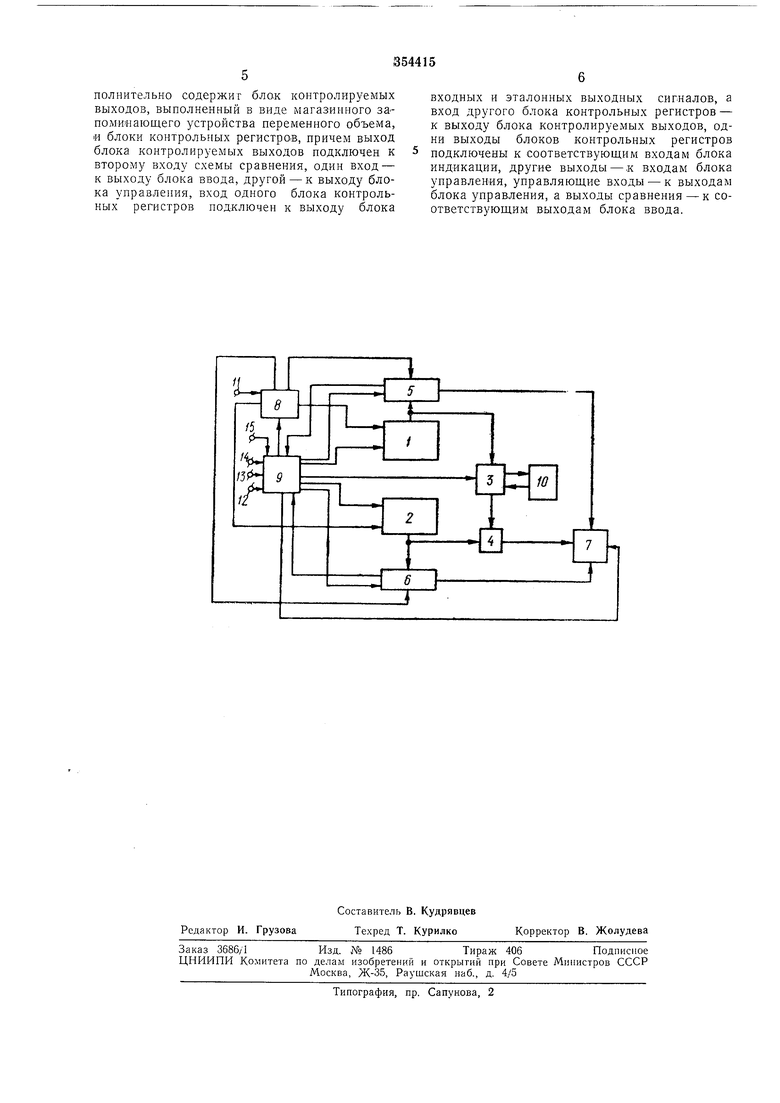

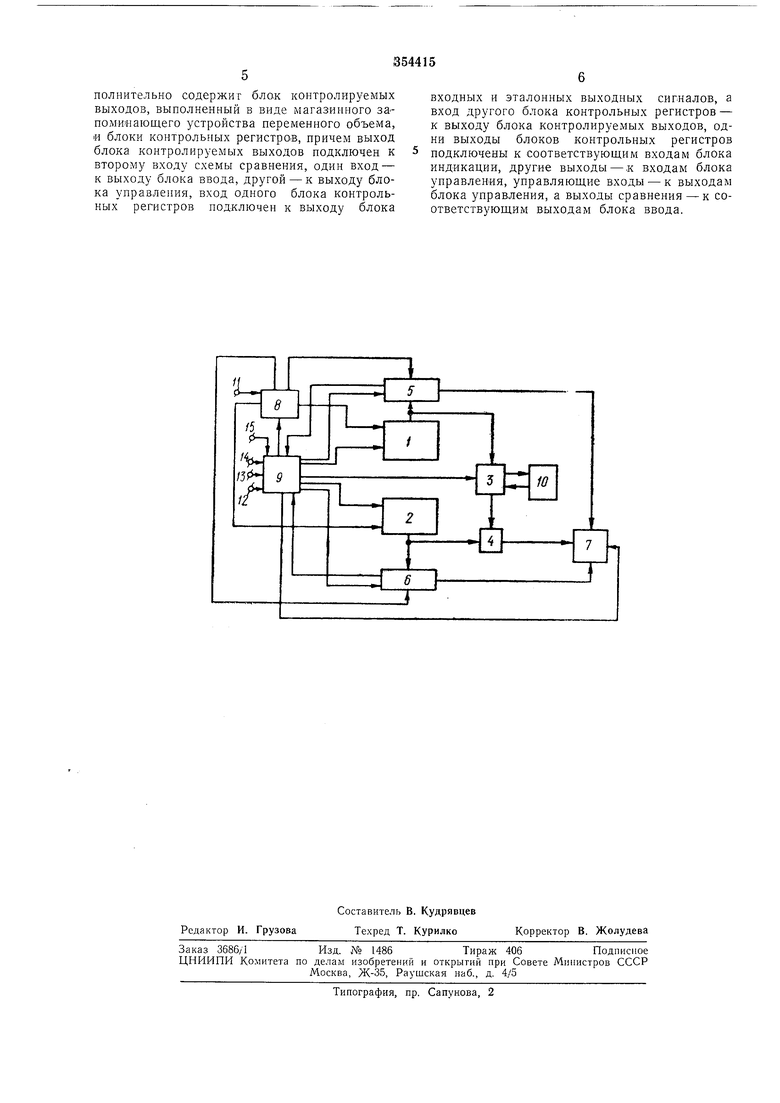

На чертеже показана блок-схема устройства для проверки функционирования логических схем.

пения; блоки 5 и 6 контрольных регистров; блок 7 индикации; блок 8 ввода даииых; блок i управления.

(Блок 1 входных и эталонных выходных сигналов, реализованный на магазинной памяти переменного объема, обеспечивает хранение « выдачу последовательности входных и эталонных выходных сигналов теста..

Блок 2 контролируемых выходов, реализованный на магазинной памяти переменного объема, хранит и выдает последовательность контролируемых выходов на каждом временном такте работы проверяемого устройства.

Коммутатор 3 подсоединяет: входы проверяемого устройства к триггерам выходного регистра магазинной памяти блока /, которые содержат сигналы входных полюсов проверяемого устройства; эталонные выходные сигналы с выходного регистра магазинной памяти блока 1 на блок сравнения; выходы проверяемого устройства на блок 4 сравнения.

Блок 4 сравнивает сигналы контролируемых выходов проверяемого устройства и эталонных выходных сигналов на каждом временном такте работы проверяемого устройства.

Блоки 5 Е 6 контрольных регистров со схемам,и сравнения на нуль обеспечивают поразрядный контроль работы магазинных памятей по модулю два после подачи последовательности входных и эталонных выходных сигналов теста и последовательности контролируемых выходов.

Блок 7 индикации неисправности проверяемого устройства фиксирует неисправность в случае несравнения эталонных выходных сигналов и сигналов контролируемых выходов проверяемого устройства, фиксируемого блоком сравнения, и равенства нулю контролируемых регистров после подачи теста.

Блок 8 ввода осуществляет последовательный ввод данных в бло.к коммутации - данных о внешних входах проверяемого устройства, в контрольные регистры - дополнения по модулю два, последовательности входных и эталонных выходных сигналов теста в блок входных и эталонных выходных сигналов, последовательности контролируемых выходов в блок контролируемых выходов. .

Блок 9 управления обеспечивает; начальную установку устройства; осуществление режимов проверки., однократного, циклического; управление объемом и сдвигом магазинных памятей блоков / и 2; управление вводом данных; анализ состояния схем, сравнения контрольных регистров на нуль; управление работой- блока индикации неиснравности.

Проверяемая логическая схема 10 должна иметь не более я внешних логических полюсов, где п - число разрядов выходных регистров магазинных памятей блоков } к 2.

Для проверки схемы, последовательность входных и эталонных выходов сигналов теста для неисправности схемы не должна превышать /Пмакс ( - макс.имальное число регистров магазинной памяти блока 1).

Перед началом, работы устройства на вход }} блока ввода данных поступает входная информация в двоичном позиционном коде по га входным каналам. Блок 8 ввода данных последовательно передает информацию о внешних входах проверяемой логической схемы на блок 3, на блок / - последовательность входных и эталонных выходных сигналов теста, на блок 2 - последовательность контролируемых

выходов, на контрольные регистры поступают соответствующие дополнения по модулю два.

На входе 12 задается объем магазинных запоминающих устройств, на входе 13-рабочая частота проведения испытаний, на входе 14

устанавливается один из возможных режимов испытания: однократный -илй циклический.

При проведении однократных испытаний на входы проверяемой схемы дается тестовая последовательность с частотой проведепия испытаний, блок 4 определяет реакцию контролируемых выходов на .каждом такте работы устройства. В случае несравнения сигналов хотя бы на одном контролируемом выходе результат несравнения передается на блок 7 индикации.

При подаче всего теста для неисправности проверяется состояние схемы сравнения контрольных регистров на нуль, в блоках 5, 6 при равенстве нулю на блок 7 выдается разрешение на индикацию неисправиости. При неравенстве нулю контрольных регистров в блок 9 управления выдается сигнал о неисправности в работе магазинных запоминающих устройств блоков / и 2.

Во время проведения циклических испытаний проводится неоднократная подача тестовой последовательности, которая обеспечивается циклическим сдвигом тестовой информации в магазинных памятях переменного объема. В циклическом режим.е проверка контрольных регистров в блоках 5 и 5 на нуль осуществляется на каждом нечетном цикле проверки на данном тесте.

После проверки схемы «а одном тесте подается следующий тест и процесс повторяется до тех пор, по,ка схема не будет проверена на всех тестах, в этом случае на блок управления поступает сигнал останова по входу 15.

Предмет изобретения

Устройство для проверки функционирования логических схем, содержащее блок ввода данных, соединенный с входом блока входных и

эталонных выходных сигналов, выполненного в виде магазинного запоминающего устройства, выход которого подключен через коммутатор сигналов к контролируемой логической схеме и через блок сравнения к блоку индика

ции, блок управления, подключенный своими выходами к блоку ввода данных, блоку входных и эталонных выхо.дных сигналов, коммутатору и к блоку индикации, отличающееся тем, что, с целью улучшения качества контрополнительно содержит бло.к контролируемых выходов, выполненный в внде матазинного запоминающего устройства переменного объема, « блоки контрольных регистров, причем выход блока контролируемых выходов подключен к второму входу схемы сравнения, один вход - к выходу блока ввода, другой - к выходу блока управления, вход одного блока контрольных регистров подключен к выходу блока

входных и эталонных выходных сигналов, а вход другого блока контрольных регистров - к выходу блока контролируемых выходов, одни выходы блоков контрольных регистров подключены к соответствующим входам блока индикации, другие выходы - .к входам блока управления, управляющие входы - к выходам блока управления, а выходы сравнения - к соответствующим выходам блока ввода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля логических блоков | 1978 |

|

SU734694A1 |

| Устройство для контроля мажоритарных схем | 1977 |

|

SU705451A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля узлов электронных вычислительных машин | 1976 |

|

SU667969A1 |

Даты

1972-01-01—Публикация