вторую группу информационных.входов мультиплексора, вторые входы элементов И первой группы подключены к первому управляющему входу мультиплексора, вторые входы элементов И второй

группы подключены к второму управляю- типлексора.

щему входу мультиплексора, выходы каждого i-го элемента И первой и второй групп соединены с входами i-ro элемента ИЛИ, вьгходы группы элементов ИЛИ образуют группу выходов муль

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| Устройство для сложения чисел с переменным основанием системы счисления | 1990 |

|

SU1714590A1 |

| Устройство для распознавания на линейность булевых функций | 1990 |

|

SU1756879A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Сумматор-вычитатель частотно-импульсных сигналов | 1991 |

|

SU1807483A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для встроенного тестового контроля | 1984 |

|

SU1196877A1 |

I. ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО, содержащее регистр, счетчик, вход которого соединен с шиной тактовых импульсов устройства, коммутатор, первая группа выходов которого соединена с первой группой раз- рядных входов первого накапливающего сумматора, триггер и первый элемент задержки, отличающеес я тем, что, с целью уменьшения запаздывания при дифференцировании дискретной последовательности, устройство содержит мультиплексор, второй накапливающий сумматор и второй элемент задержки, при этом группа информационных входов устройства соединена с группой разрядных входов регистра и с первой группой информационных входов мультиплексора, выходы разрядов регистра соединены с второй группой информационных входов мультиплексора, группа выходов которого соединена с группой разрядных входов второго накапливающего сумматора. группа разрядных выходов которого соединена с группой информационных входов коммутатора, вторая групщ выходов которого соединена с второй группой разрядных входов первого накапливаияцего сумматора, шина тактовых импульсов устройства соединена с входом триггера, с первым управляющим входом мультиплексора и через второй элемент задержки - с вторым управляющим входом коммутатора, выход триггера соединен с входом управления записью регистра, выходы счетчика и первого накапливающего сумматора являются выходами устройства. 2.Устройство по П.1, отлиS чающееся тем, что коммутатор содержит две группы элементов И, первый вход каждого i-го элемента И первой группы соединен с первым л-го элемента второй группы и с i-M входом группы информационных входов коммутатора, вторые входы элементов И первой группы подключены к второму управляющему входу коммутаVl тора, вторые входы элементов И второй о группы подключены к первсжу управляиидему входу коммутатора, выходы элеО1 ментов И первой группы образуют вую группу выходов коммутатора, выходы элементов И второй группы обрйзуют вторую группу выходов коммутатора. 3.Устройство по п.1, о т л и чающееся тем, что мультиплек сор содержит две группы элементов И и группу элементов ИЛИ, причем первые входы элементов И первой группы образуют первую группу информационных входов мультиплексора, первые входы элементов И второй группы образуют

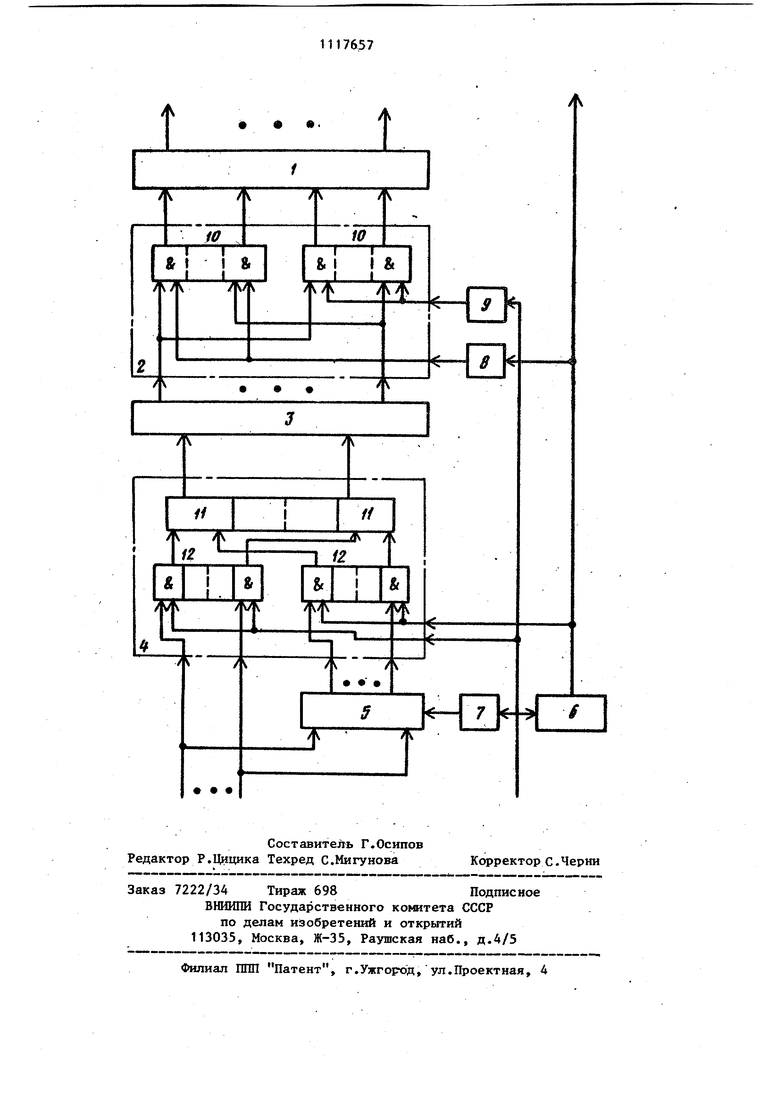

Изобретение относится к автоматике и вычислительной технике и может быть использовано для определения скорости изменения входного сигнала, представленного в виде цифрового кода. Известно устройство, содержащее реверсивный счетчик, регистр, преобразователь код-аналог, генератор, триггер, формирователь и линию задержки, позволяющее определять скорость изменения входного сигнала } Недостатком этого устройства явля ется низкая точность, связанная с тем, что скорость определяется на основе только двух измерений и тем самым в :значительной степени зависит от ошибок отдельных измерений. Известно тдкже устройство, содержащее первый и второй регистры, формирователь, счетчик, элемент задержки, элементы И и ИЛИ 2. Недостатком устройства является низкая точность, вызванная небольшим количеством измерений (четыре), учас твукнцих в определении средней скорости. Наиболее близким по технической сущности к предлагаемому является дйфференцирукнцее устройство, содержащее коммутатор, через который вход устройства соединен с входом накапли вающего Сумматора, выход которого со I единен с информационным входом регис тра, счетчик, соединенный входом с щиной тактовых импульсов, разрядными выходами - с управлякицими зкоцамя коммутатора, а выходом переполнения с триггером, выходы которого соедине ны с входами записи накапливающего сумматора, с управляющим входом регистра и через элемент задержки - с входом считывания накапливакяцего сум матора 3 . Недостаток известного устройства заключается в низком 6ыстро ействии, связанном с тем, что их входной сигнал может быть только последователь-. ностью импульсов, максимальная частота которых ограничена временем выполнения операции сложения в сумматоре. Цель изобретения - уменьшение запаздывания при дифференцировании дис-кретной последовательности. Цель достигается тем, что дифференцирующее устройство, содержащее регистр, счетчик, вход которого соединен с шиной тактовых импульсов устройства, коммутатор, первая группа выходов которого соединена с первой группой разрядных входов первого накапливанкцего сумматора, триггер и первый элемент задержки, содержит мультиплексор, второй накапливающий сумматор и второй элемент задержки, при этом группа информационных входов устройства соединена с группой разрядньгх входов регистра и с первой группой информационных входов мультиплексора, выходы разрядов регистра соединены с второй группой информационных входов мультиплексора, группа выходов которого соединена с группой разрядных входов второго накапливающего сумматора, разрядных выходов которого соединена с группой информационных входов коммутатора вторая группа вькодов которого соединена с второй группой разрядных входов первого накапливающего сумматора, шина тактовых импульсов устройства соединена, с входом триггера, с первым управлякмдим входом мультиплексора и через второй элемент задержки - с вторым управляющим входом ком1 1утатора, выход триггера .соединен с входом управления записью регистра, выходы счетчика и первого накапливающего сумматора являются выходами устройст ва. Коммутатор содержит две группы элементов И, первый вход каждого и-г элемента И первой группы соединен с первым входом -го элемента второй группы и с j-M входом группы информа ционных входов коммутатора, вторые входы элементов И первой группы подключены к второму управлянщему входу коммутатора, вторые входы элементов И второи группы подключены к первому (Управляющему входу коммутатора, выходы элементов И первой группы образуют первую группу вьпсодов коммутато .ра, выходы элементов И второй группы образуют вторую -группу выходов коммутатора. Мультиплексор содержит две группы элементов И и группу элементов ИЛИ, причем первые входы элементов И первой группы образуют первую группу информационных входов мультиплексора первые входы элементов И второй груп пы образуют вторую группу информационньк входов мультипледссора, вторые входы элементов И первой группы подключены к первому управлякщему входу мультиплексора, вторые входы элементов И второй труппы подключены к вто рому управляющему входу мультиплексо ра, выходы каждого i-го элемента И первой и второй групп соединены с входами i-го элемента ШШ выходы группы элементов ИЛИ образуют группу выходов мультиплексора. В основу положены следующие математические зависимости. Средняя скорость изменения может быть определена следующим образом Г4 Л 6(х+(1,) Этот алгоритм может быть приведен к виду, удобному для быстрого дифференцирования, если воспользоваться и двойньвш S сумоднокр атными мами входного сигнала, П (cLT) , Ы«о и об f (jTJ . ,1 7 Окончательное выражение алгоритма дифференцирования (,..,(s; к.°-1 ь где Ь - шаг . положительные числа, последний алгоритм .наиболее прос реализуется, поскольку требует запоминания только одного старого значения сумм (0) и вычисления однократной и двойной суммы в один и тот же момент времени. Кроме того, если ( V + t)2, m 1,2,..., то вычисление выражения в квадратных . скобках (3) потребует вьлопнения операции умножения. На чертеже представлена структур-. зя схема устройства, Устройство содержит накапливаюпщй сумматор 1, коммутатор 2, накапливаияций сумматор 3, мультиплексор 4, регистр 5, счетчик 6, триггер 7,элементы 8 и 9 задержки. Кроме того, коммутатор 2 содержит группу элементов И 10, а мультиплексор 4 - группу элементов ИЛИ 11 и элементов 12. Функщсонапьное назначение узлов следующее. Сумматоры 1 и 3 предназначены для вычисления однократной и двойной сумм входного сигнала и вычисления результата дифференцирования.Сунматор 1 имеет два входа: первый - вычитающий, подключен к входу сумматора, начиная с младшего разряда, такой вход может быть получен поразрядным инвертированием значащих разрядов входного кода, в-торой вход - суммирующий, подключенньй к входу суммато-. ра, начиная с т-го разряда для выполнения сложения с коэффициентом, соответствующим формуле (2), а именно . Коммутатор 2 состоит из2-х групп элементов И и предназначен для передачи кода с выхода сумматора 3 на вычитающий вход сумматора 1 при наличии сигнала на шине тактовых им-, пульсов, либо на суммирующий вход при наличии сигнала с выхода счетчика.; ЬЬ льтиплексор 4 состоит иэ 2-ос групп -элементов И, объединенных поразрядно элементами ИЛИ и преднаэначенньпс для подачи на вход сумматора 3 либо кода с входа устройства при наличии сигнала на шине тактовых сигналов, либо с выхода регистра по сигналу с выхода счетчика.

Регистр 5 предназначен для запоминания на период вычислений значения входного сигнала в начальный момент времени f(0). Регистр 5 имеет синхронизирукиций вход, связанный с выкодом триггера 7. Регистр 5 и триггер 7 образуют регистр-защелку, информация в которьй заносится однократно после сброса триггера 7. Счетчик 6 предназначен длЛ подсчета количества значений входного сигнала, поступивших на вход устройства, вьфаботки сигнала окончания суммирования и управления формированием результата по достижении счетчиком значения 2 .

Элементы задержки суммирования в первом сумматоре используются на время окончания операции в сумматоре 3.

Устройство работает следунщим об- разом. .

В исходном состоянии сумматоры 1 и

3и счетчик обнулены, а триггер 7 находится в состоянии, обеспечивающем прием значения f(0) на регистр 5. На вход устройства поступает входной сигнал в обратном коде, сопровождаемьй импульсом на тактовой шине, которьй обеспечивает занесение значения f(0)

в регистр 5, открывает мультиплексор

4для прибавления этоГо значения к содержимому сумматора 3, а после окончания суммирования в нем открывает коммутатор 2 для вычитания содержимого сумматора 3 из содержимого сумматора 1. Следунлдее значение входного сигнала, также сопровождаемое тактовым сигналом, не изменяет содержимого регистра 5, так как триггер 7 заперт. В остальном процесс вычисления повторяется.

В результате в сумматоре 3 оказывается значение (о)+ 1т) , а в сумматоре 1 - значение (2(ОИ(,Т)) .

Каждьй сигнал на тактовой шине, кроме того, выполняет прибавление 1 к счетчику 6. Когда на вход устройства придет 1 + 1-и тактовьй импульс, на сумматорах 3 и 1 формируются однократная и двойная суммы входных сигналов, если k-i-1 2, то сигнал переноса со счетчика 6 поступает на управляющий вход мультиплексора 4 и обеспечивает прибавление содержимого регистра 5 к содержимому сумматора 3. После окончания суммирования этот сигнал поступает на второй управляющий вход коммутатора 2 через элемент 8 задержки и полученное значение будет прибавлено к содержимому сумматора 1. Поскольку второй выход коммутатора подключен к входу сумматора 1, начиная с т-го разряда, сложение выполняется с коэффициентом Я-fl. Таким образом, после окончания операции в сумматоре 1 будет получено значение f(.xl s вычисленное по формуле (2) с точностью до постоянного масштабногЬ множителя(цепи сброса с целью упрощения . не показаны).

Таким образом, предлагаемое устройство позволяет определять производную входного сигнала, представленного в виде .цифрового кода, обеспечивая тем cavuOM повьш1ение быстродействия,

Технико-экономический эффект изобретения заключается в обеспечении возможности дифференцирования быстродёйствунндих входных сигналов, представленных в цифровом коде. Например, если времй выполнения сложения в сумматоре равно tc , разрядность входного кода - п, то максимальное количество импульсов, соответствуклдее этому коду, равно 2 и для приема одного значений входного сигнала устройству 3 потребуется время i.if.2 , а предлароемому -, 2-t . Таким образом, предлагаемое устройство способно принимать и обрабатьшать сигналы с частотой в раза чаще.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дифференцирующее устройство | 1977 |

|

SU711586A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Практические методы прикладного анализа | |||

| М., Физматгиз | |||

| Судно | 1925 |

|

SU1961A1 |

Авторы

Даты

1984-10-07—Публикация

1983-04-05—Подача