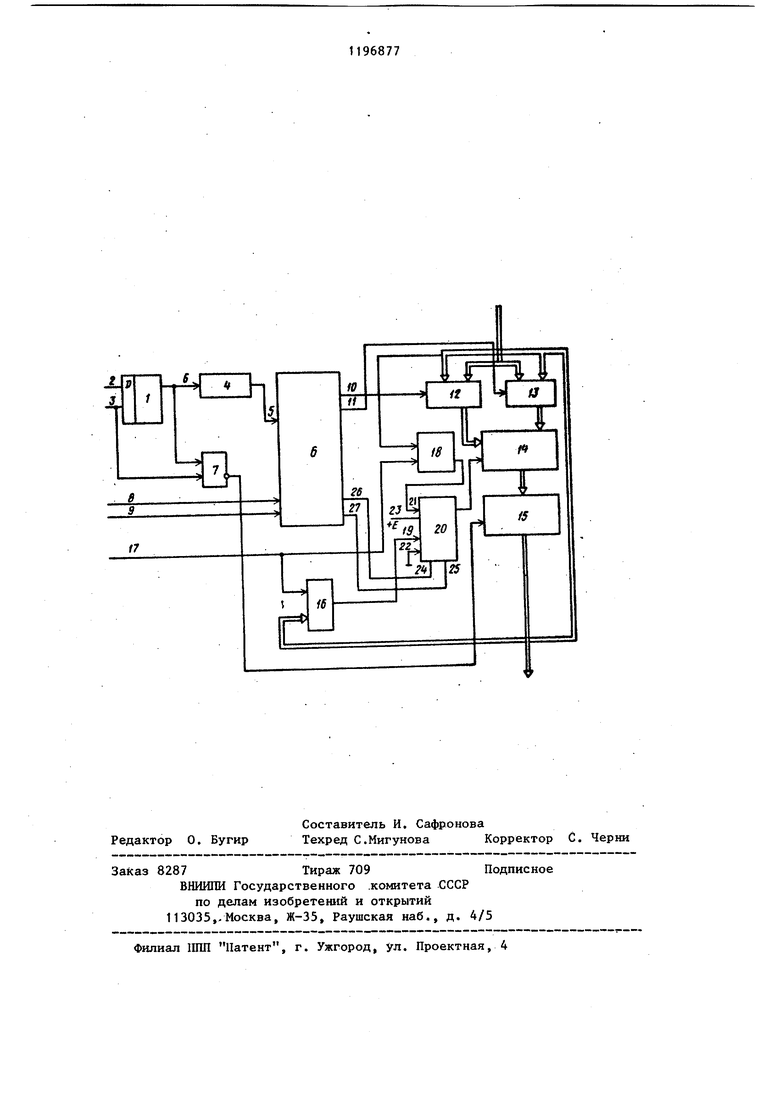

, Изобретение относится к области встроенного автоматизированного кон роля и может быть использовано для контроля различньк цифровых блоков. Целью изобретения является расши рение области применения устройства за счет обеспечения возможности работы в режимах генератора псевдослучайной последовательности, счетчика сигнатурного анализатора и счетчика числа переходов. На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит триггер 1, информационный вход которого является входом 2 устройства, тактовый вход 3 устройства соединен с входом синхронизации триггера 1, единнчньй выход которого соединен через элемент 4 задержки с первым входом 5 блока 6 управления. Кроме того, единичньй выход триггера 1 соединен с первым входом элемента И 7. Первьш 8 и второй 9 входы задания режима соединены с вторым и третьим входами блока 6. Первый 10 и второй 11 управляющие выходы блока 6 соединены с управляющими входами соответственно первого 12 и второго 13 коммутаторов, выходы которых соединены соответственно с входами первого и второго операндов сумматора 14. Выход результата сумматора 14 соединен с информационным входом регистра 15 информационный выход которого соединен с первыми информационными входами коммутаторов 12 и 13, первого сум матора 16 по модулю два и является группой информационных выходов устройства. Информационный вход 17 соед нен с входом первого сумматора 16 и первым входом второго сумматора 18 по модулю два. Выход младшего разряда регистра 15 соединен с вторым входом первого сумматора 16. Выход первого сумматора 16 соединен с первым информационным входом 19 мультип лексора 20. Выход второго сумматора 18 соединен с вторым информационным входом 21 мультиплексора 20, а его третий 22 и четвертьш 23 информационные входы соединены соответственно с шиной нулевого иединичного потенциала. Выход мультиплексора 20 .с.оединен с входом переноса сумматора 14. Управляющие входы 24 и 25 мульти лексора 20 соединены с управляющими выходами 26 и 27 блока 6, которьй 77 является комбинационным блоком и обеспечивает реализацию логических уравнений Блок 6 может быть реализован на элементах И, ИЖ согласно приведенным уравнениям (1) - (4) или на ШШ, или на блоке ПЗУ. Управляющие входы 24 и 25 мультиплексора 20 обеспечивают коммутацию входных сигналов 19,21,22,23 на выход мультиплексора 20 в соответствии с логичес1 И1-ш уравнениями 19 - 20 . 21; (5) 21-н. 20 24 25, (6) 22- 20 24 (7) 23- 20 24 25. (8) Запись 19 - 20, 21 - 20, 22 - 20, 23 обозначает, что на вькод мультиплексора 20 скоммутированы входы 19,21,22 и 23 соответственно. Коммутатор 12(13) обеспечивает коммутацию на выход первой группы информационных входов коммутаторов 12(13) при нулевом значении управляющего выхода 10(11) блока 6 и на вторую группу информационных входов при единичном значении управляющего выхода 10(11). Устройство работает следующим образом. При отсутствии сигнала Пуск на входе 2 устройства входным тактовым сигналом на входе 3 происходит установка в нулевое состояние триггера 1, которое блокирует прохождение так товых импульсов на выходе элемента И 7. Нулевое значение на входе 5 блока 6 согласно уравнениям (1) и (2) приводит к тому, что на выходе 10 и 11 блока 6 появляется единичный сигнал, которьй коммутирует информационньй вход устройства на входы первого и второго операнда сумматора 14 (во всех режимах, которые рассмотрены в предлагаемом устройстве, этот вход соединен с шинами нулевого потенциала). Следовательно, на входы первого и второго операндов сумматора подаются нулевые значениния. Далее, в зависимости от значения сигналов, на входах 8 и 9 задания режима на выходах 26 и 27 блока 6 появляются следующие управляющие воздействия в соответствии с уравнениями 26 - const - 1, при , При всех остальных значениях сигналов на входах 8 и 9 на выходе 27 блока 6 присутствует единичный сигнал. Следовательно, при отсутствии сигнала Пуск на входе устройства управляющие сигналы на входах 24 и 25 мультиплексора 20 принимают значения - код 11 во всех режимах, кроме работы в режиме генератора псевдослучайной последовательности. В этом режиме на входах 8 и 9 установлен код 10 и на выходе - код 10.

Предлагаемое устройство может работать в четырех режимах, которые устанавливаются кодами на входах 8 и 9. Установка режимов может обеспечиваться либо тумблерами, пибо распайкой, либо программно путем подачи на входы 8 и 9 соответствуюицЕс кодов. Если на входах 8 и 9 задан код 00, то предлагаемое устройство должно функционировать в режиме счетчика числа переходов, если код 10 - в режиме генератора псевдоiслучайной последовательности,.если 1код 01 - в режиме счетчика последо(вательностных состояний и если код 11, - в режиме сигнатурного анализатора.

Во время начальной установки на входе блока 6 присутствует нулевой сигнал согласно уравнениям (1) - (4) на выходе 10 - единичньй сигнал, на входе 8 - единичньй сигнал, на выходе 26 - единичный сигнал, а на выходе 27 - единичный сигнал, кроме режима, когда на входах 8 и 9 установлен код 10, которьй соответствует режиму генерации псевдослучайной последовательности. Таким образом, во всех режимах на входах сумматора 14 присутствуют нулевые операнды, а на входе переноса, согласно уравнениям (5) - (8) - также нулевое значение, кроме режима генерации псевдослучайной последовательности. В этом режиме на входе сумматора 14 - единичное значение переноса (уравнение 7). Первьй тактовьй импульс с входа 3 устройства устанавливает в единичное состояние триггер 1, при условии что до него на вход 2 подан сигнал Пуск. Единичное значение триггера 1 разрешает прохождение тактовых импульсов на управляющий вход записи регистра 15. По сигналу записи в

регистр 15 записывается информация с выхода сумматора 18, которая во всех режимах, кроме режима генерации псевдослучайной последовательности, нулю, а в режиме генерации псевдослучайной последовательности равна единице. На этом подготовка устройства к работе заканчивается.

В предлагаемом устройстве все перечисленные режимы реализуются следующим образом.

Режим счетчика числа переходов. На входах 8 и .9 код 00. В этом режиме предлагаемое устройство должно обеспечить подсчет изменения состоя- ,

5 НИИ на информационном входе -17 устройства. Устройство должно обеспечить прибавление единицы при изменении состояния на входе 17 либо от единицы к нулю, либо от.нуля к единице.

0 Подсчет числа переходов происходит следующим образом. Сигнал на входе 5 равен единице, согласно уравнениям (1) - (4) на выходе -10 - нулевое значение, на выходе 11 - еди5

ничное значение, на выходах 26 и 27 - нулевые значения. Нулевое значерше на выходе 10 блока 6 обеспечивает передачу на вход первого операнда сумматора 14 содержимого

0 регистра 15. Е диничное значение выхода 11 блока 6 обеспечивает передачу на вход второго операнда сумматора 14 информации со второй группы информационных входов устройства,

5 которые соединены с шиной нулевого потенциала. На входах 24 и 25 мультиплексора 20 установлены нулевые значения. Согласно уравнению (6) мультиплексор 20 обеспечивает пода0чу на вход переноса сигнала с выхода второго сумматора 18 по модулю два. Сумматор 18 по модулю два осуществляет сравнение текущего состояния на входе 17 с мпадшим разрядом

5 регистра 15, которьй несет двойную функциональную нагрузку - является мпадшим разрядом регистра 15 и помнит предьщущее состояние входа 17. Если состояние младшего разряда регистра 15 не совпадает со значением

0 сигнала на входе 17, то на выходе второго сумматора 18 по модулю 2 появляется единичньй сигнал, который через мультиплексор 20 поступает на

5 вход переноса сумматора 14, в котором осуществляется суммирование содержимого регистра 15 (выход коммутатора 12 - первьй операнд, выход коммутатора 13 - второй операнд с выходом переноса сумматора 18 по модулю 2. Таким образом, каждое изменение сигнала на входе 17 устройства увеличивает содержимое регистра 15 на единицу. Причем запись результата суммирования осуществляется по тактовому сигналу с выхода элемента И 7.

В режиме счетчика последовательных состояний на входах 8 и 9 устройства установлен код 01. В этом режиме предлагаемое устройство выполняет функцию счетчика, содержимое которого увеличивается по каждому тактовому сигналу на выходе элемента И 7. Работа в этом режиме .осуществляется следующим образом. Согласно логическим уравнениям (О - (4) сигналы на выходах 10 и 11 блока 6 изменяются. На выходе 26 - единичное значение сигнала, на выходе 27 - нулевое значение. При (ЭТОМ мультиплексор 20, согласно ура нению (7), обеспечивает подачу на вход переноса сумматора 14 единичного значения с входа 23 мультиплексора 20. Таким образом, в каждом такте (по каждому импульсу синхронизации) в регистр 15 осуществля ется запись результата суммирования предьщущего значения регистра 15 с единичным значением сигнала переноса, т.е. регистр 15 является счетчикбм тактовых импульсов.

Режим генератора псевдослучайной последовательности. В этом режиме находится устройство при коде 100 на входах 8,9 и 17 устройства соответственно, при этом предлагаемое устройство обеспечивает генерацию кодов псевдослучайной последовательности. Работа устройства в этом реяиме осуществляется следующим образом. На регистре 15 установлен 000....01 (см. описание работы устройства в режиме начальной установк Согласно уравнениям (1) - (4) на выходы 10 и 11 блока 6 устанавливаются нулевые потенциалы. Тем самым

на входы первого и второго операндов сумматора 14 коммутаторы 12 и 13 передают содержимое регистра 15. На эыходах 26 и 27 блока 6 установлен код 01. Мультигшексор 20 согласно уравнению (5) пропускает на вход переноса сумматора 14 результат сумгмирования по модулю два всех разрядов регистра 15, которые охваченыобратными связями. На выходе сумматора 14 получается сумма, равная удвоенному значению содержимого регистра 15 и сигнала переноса, равного результату суммирования по модулю два тех разрядов регистра 15, которые охвачены обратной связью Удвоение результата эквивалентно сдвигу влево на один разряд. Регистр 15 превращаетсятаким образом в циклический регистр сдвига, младший разряд которого меняется в соответст ВИИ с изменением суммы по модулю два полученной на сумматоре 16.

Согласно известному определению такое устройство является генератором псевдослучайной последовательности. Таким образом, по каждому тактовому сигналу на выходе элемента И 7 на регистре 15 появляется код псевдослучайной последовательности, вьфабатываемой устройством.

Режим сигнатурного анализатора. В этом режиме устройстззо должно .обеспечить получение сигнатуры входа 17 и запоминания ее в регистре 15. На входах 8 и 9 устройства установлен код 11. Работа устройства отличается от работы устройства в режиме генерации псевдослучайной последовательности только тем, что вход 17 устройства подключен не к шине нуле вого потенциала, как в предыдущем режиме, а к точке, сигнатуру которой необходимо получить. При этом сумматор 16 По модулю два осуществляет суммирование не только тех разрядов счетчика, которые охвачены обратной связью, но и сигнала на входе 17.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для встроенного тестового контроля | 1986 |

|

SU1324029A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Устройство для формирования тестовой последовательности | 1986 |

|

SU1529293A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

УСТРОЙСТВО ДЛЯ ВСТРОЕННОГО ТЕСТОВОГО КОНТРОЛЯ, содержащее триггер, блок управления и элемент задержки, отличающееся тем, что, с целью расширения области применения устройства а счет обеспечения возможности работы в режимах генератора псевдослучайной последовательности, счетчика, сигнатурного анализатора и счетчика числа переходов, в него введены регистр,элемент И, первьй и второй сумматоры по модулю два, мультиплексор, первьш и второй ., коммутаторы и сумматор,причем вход Пуск и тактовый вход устройства соединены соответственно с информационным и входом синхронизации триггера, прямой выход которого соединен с первым входом элемента И и через элемент задержки с первым входом блока управления, первьй и второй входы задания режима работы устройства соединены соответственно с вторым и третьим входами блока управления, информацчонньй вход устройства соединен с первыми входами первого и второго сумматоров по модулю два, выходы которых связаны соответственно с первым и вторым информационными входами мультиплексора, третий и четвертьй информационные входы которого соединены соответственно с шинами единичного и нулевого потенциала, первьй и второй выходы блока управления соединены с управляющими входами первого и второго коммутаторов соответственно, третий и четвертьй выходь блока упг. равления соединены с первым и втос S рым входами мультиплексора соответственно, группа информационных вхо(Л дов устройства соединена с первыми группами информационных входов перс вого и второго коммутаторов, выходы которых соединены соответственно с входами первого и второго операндов сумматора, выход результата которого соединен с информационным входом регистра, тактовьй вход устройства со соединен с вторым входом элемента И, CD 00 выход которого связан с входом разрешения записи регистра, группа вы ходов которого соединена с .вторыми ч группами информационных входов первого и второго коммутаторов, выход младшего разряда регистра соединен с вторым входом второго Сумматора по модулю два, выходы разрядов регистра соединены с соответствующими входами группы входов первого сумматора по модулюдва, выход мультиплексора подключен к входу переноса сумматора.

| Устройство для тестового диагностирования | 1978 |

|

SU792258A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения и диагностики неисправностей логических блоков | 1976 |

|

SU615492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1985-12-07—Публикация

1984-05-25—Подача