Изобретение относится к вычислительной технике и может быть применено в устройствах обработки информации. Известно устройство управления обращением к памяти, применяемое в цифровых вычислительных машинах, в котором цикл оперативной памяти зна чительно больше цикла процессора, содержащее блок управления, распред литель и генератор С13. Недостатком данного устройства является фиксированный цикл памяти и невозможность подключения оперативной памяти с другим циклом обращения . Известно устройство управления обращением к памяти, содержащее блок управления, распределитель,генератор, ,узел индикации свободной зоны памяти и узел задержки i2. Недостатком известного устройства являются затраты на оборудование из-за необходимости управления выработкой тактовых импульсов,приче затраты возрастают пропорционально количеству вырабатываем1.Х тактовых импульсов. Кроме того, время остано ва кратно циклу синхронизации,что приводит к значительным потерям быстродействия, когда цикл обращени к памяти не кратен циклу синхрониза ции., Наиболее близким к изобретению является устройство управления обращением к памяти, содержащее элемент пусков памяти И, первый вход которого соединен с первым выходом линии задержки, второй выход которо соединен с вторым выходом устройств вход линии задержки соединен с выходом элемента пусков памяти И З. Недостатком данного устройства является то, что при наличии буфера оперативной памяти данное устройств не обеспечивает управление, так как оно лишь определяет когда можно вьщать запрос к памяти после послед . него запроса, т.е. устройство по запросу памяти организует необходимую паузу, в течение которой оперативное запоминающее устройство (ОЗУ выполняет операцию, а при наличии буфера, если затребованные данные Находятся в нём, пауза не нужна, так. как обращения к ОЗУ. нет. Кроме того, применение буферной памяти требует дополнительного устройства управления, взаимодействующего с даннь устройством, т.е. требует дополнительных аппаратурных затрат. Цель изобретения - сокращение оборудования. Поставленная цель достигается тем, что в устройство управления памятью, содержащее триггер индикации запросов, первый элемент И и первую линию задержки, первый выход которой соединен с входом сброса триггера индикации запросов, единичный выход которого соединен с первым входом первого элемента И, выход которого соединен с входом первой линии задержки, второй выход которой подключен к первому выходу устройства, тактовый вход устройства соединен с вторым входом первого элемента И, запросньпЧ вход устройства подключен к единичному входу триггера индикации запросов, введены второй элемент И,триггер управления паузой и вторую линию задержки, причем первый угфавляющий вход устройства соединен с входом второй линии задержки, первый выход которого соединен с вторым выходом устройства, второй выход второй линии задержки соединен с входом сброса триггера управления паузой, единичный вход которого соединен с выходом второго элемента И, первый вход которого подключен к третьему выходу первой линии задержки, второй вход второго элемента И соединен с вторым управляющим входом устройства, единичный выход триггера управления паузой подключен к третьему выходу устройства. На фиг.1 приведена общая схема устройства; на фиг.2 - временная диаграмма, поясняющая работу устройства. Устройство управления памятью (фиг.1) содержит триггер 1 индикации запросов к памяти, первый элемент И 2, первую линию 3 задержки, второй элемент И 4, триггер 5 управления паузой и вторую линию 6 задержки, тактовый вход 7, запросный вход 8, первьй управляющий вход 9, второй управляющий вход 10, первый выход 11, второй выход 12 и третий выход 13. Триггер 1 индикации запросов к памяти предназначен для запоминания запроса к оперативной памяти (СП), сгенерированного устрой31

ством обработки информации и поступившего на запросный вход 8 устройства.

Первая линия 3 задержки предназначена для формирования временной . диаграммы, необходимой для обработки запроса к ОП.

Триггер 5 управления паузой предназначен для организации паузы, в течении которой оперативное запоминающее устройство вьтолняет заданную ему операцию.

Вторая-линия.6 задержки предназначена для формирования временной диаграммы, необходимой для приема данных из ОЗУ и завершения обработки запроса к ОП.

Устройство работает следующим образом.

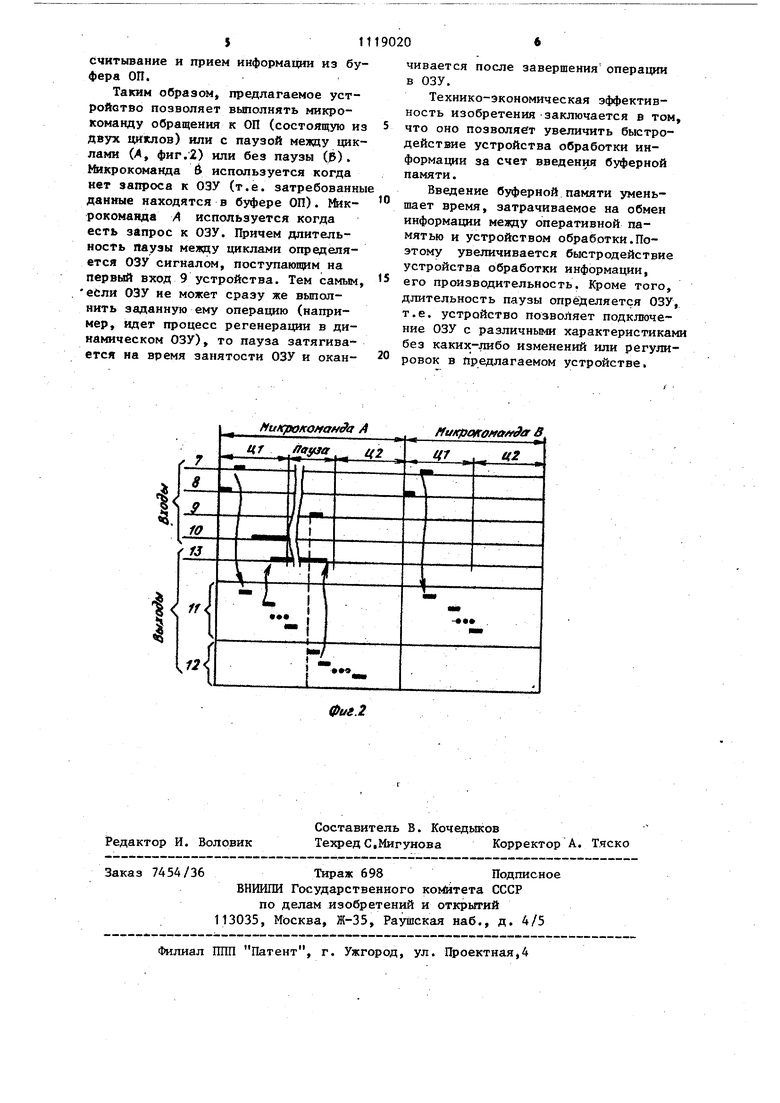

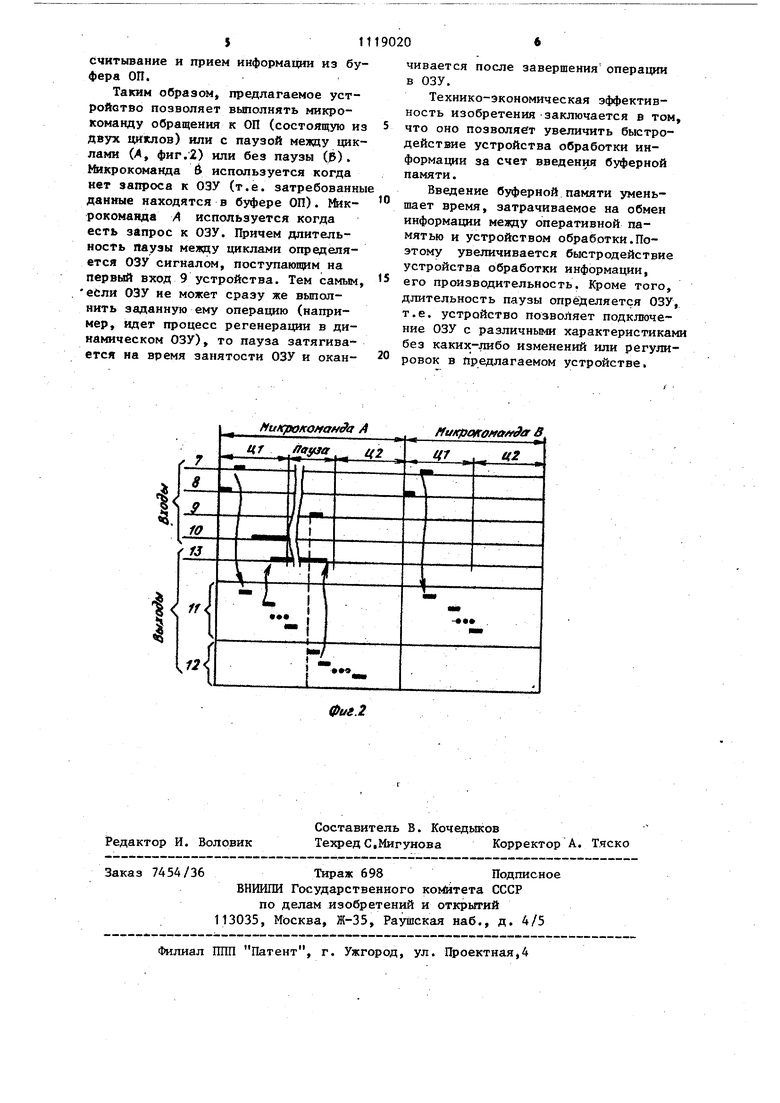

Устройство обработки информации, с которым соединено предлагаемое устройство, управляется микрпрограммно. Микрокоманда обращения к ОП и выполняется за два цикла: Ц1 и Ц2 (фиг.2). Рассмотрим микрокоманду А (микрокоманда обращения к ОП), по которой в начале Ц1 на запросный вход 8 устройства поступает сигнал, указывающий, что сгенерирован запрос к ОП, который устанавливает триггер 1 индикации запросов к памяти (фиг.1). В этом случае тактовьй импульс (ТИ), поступивший с тактового входа 7 устройства, пройдя через первый элемент И 2, поступает на вход первой линии 3 задержки. Первая линия 3 зддержки формирует серию импульсов (фиг. 2), поступающих на первый выход 11 устройства. Данная серия.импульсов поступает в устройство обработки информации и определяет временную диаграмму, необходимую для обработки запроса к ОП (управление буфером ОП, запуск операции для ОЗУ).

Пусть устройство обработки (имеющее в своём составе буфер ОП) определило, что запрашиваемых данных в буфере нет, т.е. необходим запрос к ОЗУ. В этом случае на второй вход 10 устройства поступает сигнал который разрешает лрохолдение импульса с третьего выхода первой линии 3 задержки через второй элемент И 4 на установочный вход триггера 5 управления паузой, устанавливая его в единичное состояние. Выход триггера 5 управления паузой поступает на третий выход 13

90204

устройства и далее в устройство обработки, переводя его в состояние Останов после цикла Ц1. Таким образом, организуется пауза меяду циклами Ц1 и Ц2.

По запущенной развертке (первый выход 11) устройство обработки информации вьдает необходимую для запуска операции в ОЗУ информацию и управление. ОЗУ выполняет операцию и после ее завершения вьщает сигнал (импульс), поступающий на первый вход 9 устройства, соединенного с входом второй линии 6 задержки, на которой формируются серия импульсов, поступающих на второй выход 12 устройства, а также вьграбатьшается сигнал, поступаюш гй на триггер 5 управления паузой и сбрасывающий его. Таким образом, устройство обработки информации вьшодится из состояния„Останов, пауза завершается и обрабатывается Ц2 икpoкoмaнды Л. По запущенной развертке (второй выход 12) ,устройство обработки осуществляет прием из ОЗУ информации, ее б еризацию в буфере ОП. В цикле Ц2 осуществляется передача информа;ции в регистры устройства обработки, считывание следующей микрокоманды. Первый выход первой линии 3 задержки соединен с входом сброса триггера 1 и адикации запросов к памяти - эта цепь служит для установки в начальное состояние триггера 1.

5 Рассмотрим случай, когда микрокоманда обращения к ОП не требует запроса к ОЗУ, т.е. запрошенные данные имеются в буфере ОП (микрокоманда В фиг.2).

- Аналогично (как в микрокоманде А) происходит, формирование серии импульсов первой линии 3 задержки поступающих на первьй выход 11 устройства. Однако, так как микрокоман да В не требует запроса к ОЗУ, на втором входе 10 устройства отсутствует сигнал и поэтому блокируется прохождение импульса с третьего выхода первой линии 3 задержки через второй

0 элемент И 4. Поэтому триггер 5 управления паузой не устанавливается в единичное состояние, следовательно устройство обработки информации после завершения цикла Ц1 сразу же

5 начинает цикл Ц2, т.е, отсутствует пауза между циклами.

По запущенной развертке (первый выход устройства. 11) осуществляется

считывание и прием информации из буфера ОП.

Таким образом, предлагаемое устройство позволяет вьшолнять микрокоманду обращения к ОП (состоящую из двух щнслов) или с паузой между циклами (А, фиг.2) или без паузы (Э). ЬЬ1крокоманда И используется когда нет запроса к ОЗУ (т.е. затребованны данные находятся в буфере ОП). Шкрокомаяда А используется когда есть запрос к ОЗУ. Причем длительность йаузы межцу циклами определяется ОЗУ сигналом, поступающим на первый вход 9 устройства. Тем самым если ОЗУ не может сразу же выполнить заданную ему операцию (например, идет процесс регенерации в динамическом ОЗУ), то пауза затягивается на время занятости ОЗУ и оканчивается после завершения операции в ОЗУ.

Технико-экономическая эффективность изобретения заключается в том, что оно позволя€Гт увеличить быстродействие устройства обработки информации за счет введения буферной памяти.

Введение буферной памяти уменьшает время, затрачиваемое на обмен информации межцу оперативной памятью и устройством обработки.Поэтому увеличивается быстродействие устройства обработки информации, его производительность. Кроме того, длительность паузы определяется ОЗУ, т.е. устройство позволяет подключение ОЗУ с различными характеристикам без каких-либо изменений или регулировок в предлагаемом устройстве.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство управления памятью | 1981 |

|

SU1001100A1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

| Устройство для сопряжения процессора с памятью | 1980 |

|

SU898437A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ, содержащее триггер индикации запросов, первьй элемент И и первую линию задержки, первый выход которой соединен с входом сброса триггера индикации запросов, единичный выход которого соединен с первым входом первого элемента И, выход которого соединен с входом первой линии задержки, второй выход которой подключен к первому выходу устройства, тактовьй вход устройства соединен с вторым входом первого элемента И, запросный вход устройства подключен к единичному входу триггера индикации запросов, отличающееся тем, что, с целью сокращения оборудования, оно содержит второй элемент И, триггер управления паузой и вторую линию задержки, причем первьй управляющий вход устройства соединен с входом второй линии задержки, первый выход которой соединен с вторым выходом устройства, второй выход второй линии задержки соединен с i входом сброса триггера управления паузой, единичный вход которого сое(Л динен с выходом второго элемента И, первьй вход которого подключен к третьему выходу первой линии задержки, второй вход второго элемента И соединен с вторым управляющим входом устройства, единичньй выход триггера управления паузой подключен к третьему выходу устройства. ;О N)

HuKpoKOffOff a А

ffuKfjOfcOftet/f ff В

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Флорес А | |||

| Организация вычислительных машин, М., Мир, 1972, гл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-15—Публикация

1983-04-25—Подача