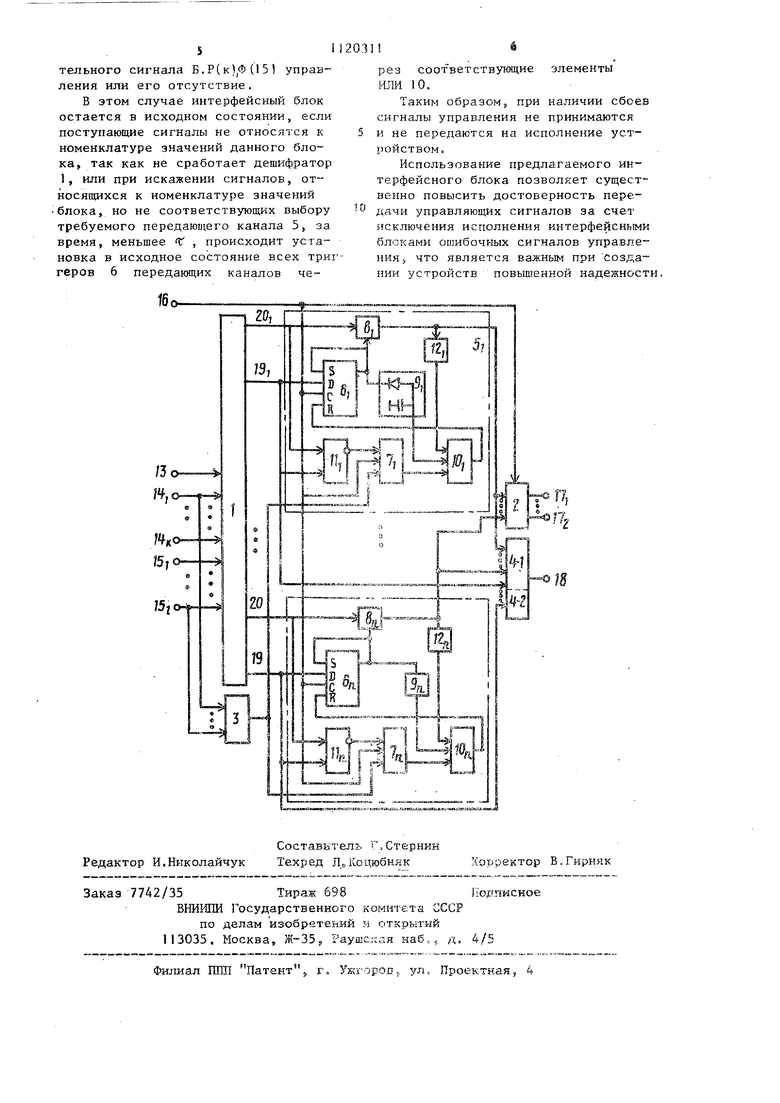

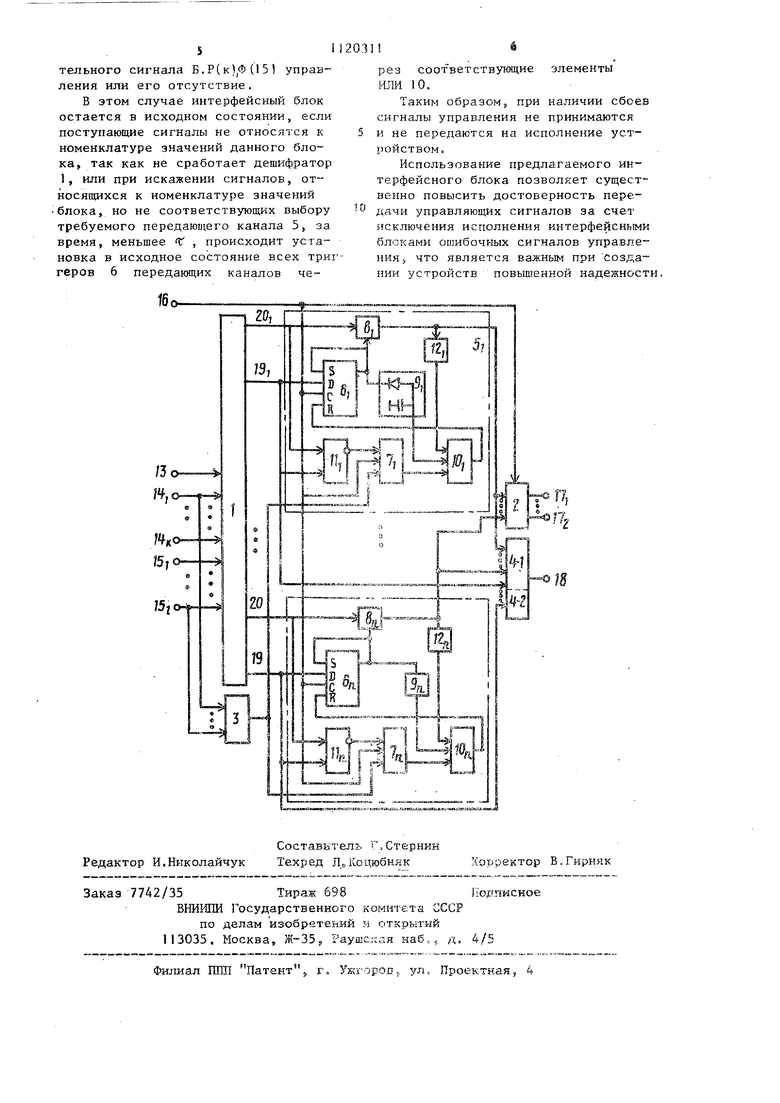

1i Изобретение относится к техничес кой физике и может быть использовано в составе многоканальных управляющих систем для управления различ ными устройствами, например электро ными управляющими модулями исследовательских критических сборок. В этом случае управляющая система находится под воздействием помех создаваемых силовым оборудованием, вследствие чего в ней происходят различного рода программные и аппаратные сбои. В то же время при упра лении интерфейсными блоками, обслуКивающими органы регулирования крит сборки, особое значение приобретает надежность управления. Известно устройство, содержащее дешифратор, один из выходов которог соединен с исполнительной шиной, а другой - через ключ, управляемый внешним исполнительным устройством, с шиной состояния интерфейсного блока. Устройство получает сигналы управ ления по шинам адреса и синхронизации, которые дешифруются дешифратором и с соответствующих выходов пос леднего поступают на исполнительную П1ину и шину состояния. Сигнал с шины с рстояния поступает во внешнее устройство для подтверждения получения сигнала управления ij. Наиболее близким к предлагаемому по технической сущности является устройство, содержащее дешифратора выходы которого соединены с входами элемента ИЛИ, выход которого соединен с шиной состояния интерфейсного блока, а каждая из п исполнительных шин интерфейсного блока соединена с вьпсодом блока ключей, вход управления которого соединен с шиной синхронизации интерфейсного блока, шины управления и функции соединены с входами дешифратора, а каждый из входов блока ключей - с одним из входов элементов ИЛИ. Устройство, являющееся выводным интерфейсным блоком, предназначено для эксплуата ции в нормализованном каркасе. Оно получает сигналы управления по шинам субадреса Р, функции Фр и упр ления Б, которые дешифрируются дешифратором и с соответствующих выходов последнего поступают на входы блока ключей, а также через элементы ИЛИ на шину состояния. Сигнал с шины состояния поступает во внешнее 2 устройство для подтверждения получения сигнала управления данным интерфейсным блоком и анализируется им в момент прихода импульса синхрокизации С23, Е едостатком известных устройств является низкая достоверность информации так как они одинаково воспринимают как действительные, так и ошибочные сигналы управления, Цель изобретения - повьпиение достоверности принимаемой информации. Поставленная цель достигается тем, что в интерфейсный блок, содержащий дешифратор, группу выходных элементов ИЛИ и коммутатор, причем входы стробирования, адреса и информации блока соединены с входами дешифратора, вход синхронизации блока соединен с управляющим входом коммутатора, выходы которого являются информационной группой выходов интерфейсного блока, выходы выходных элементов ИЛИ группы образуют выход подтверждения блока, введены группа передающих каналов, входной элемент ИЛИ и вторая группа выходных элементов ИЛИ, а каждый передающий канал содержит триггерj элементы И, ИЛИ. ИЛИ-КЕ, коммутирующий элемент, формирователь импульсов и элемент задержки, причем в каждом передающем канале выход триггера соединен с первым управляющим входом триггера и входами элемента задержки и управления коммутирующего элемента, выход которого соединен с входом формирователя импульсов, выход которого соединен с первьгм входом элемента ИЛИ, второй и третий входы которого соединены соответственно с выходом элемента задержки и с выходом элемента И, выход элемента ИЛИ соединен со вторьш уппаклякщим входом триггера, выход элемента ИПИ-НЕ - с первым входом эле мента И,, при этом первая группа выходов детаифратора соединена с информационными входами триггеров передающих каналов группы, вторая группа вьосодов с вкодами коммутируюЕ их элементов и с первыми входами эле{.;ентов ИЛИ-НЕ соответствующих передакщих каналов группы вход синхронизации блока соединен с входом стробирования триггера и в:торым входом элемента И каждого передающего канала группы, ВХОДЫ адр.еса и информации блока соединен з1 с соответствующим 31нходамн рходиого элемента ИЛИ, выход KOTOjioio соединен С третьим входом элемента И каждого передающе го какала группы, выход коммутирующ го элемента каждого передающего-канала соединен с соответствующим информационным входом коммутатора и с входами выходных элементов ИЛИ второй группы, выходы которых соеди нены с выходом подтверждения блока. На чертеже приведена функциональ ная схема предлагаемого устройства. Интерфейсный блок содержит дешиф ратор , коммутатор 2, входной элемент UHi 3 и первую 4-1 и вторую группы выходных элементов ИЛИ, группу из п передаюших каналов 5, каждый из которых содержит триггер элемент И 7, коммутирующий элемент 8, элемент 9 задержки, имеющий выдержку времени С, элемент ИЛИ Ю, элемент 1ШИ-НЕ II, формирователь . 12 импульсов. При этом интерфейсный блок имеет входы 13-16 стробирования, адреса, информации и синхронизации соответственно и-выходы 17 и 18 соответственно информации и подтверждения. Дешифратор 1 имеет первую группу выходов I9 и вторую груп пу выходов 20. . Устройство работает следзтощим образом. Из всего многообразия функций вы делим две, одна из которых, например Ф (25), является основной, а другая, например Ф (15), вспомогательной. Отметим также значение суб адреса Р С 1 ). Допустим, в некоторый момент вре мени на входные шины со второй по четвертую подается вспомогательный сигнал управления Б.Р(1), Ф(15К При этом на выходе 19 дешифратора 1 появляется сигнал I, а на выходах элементов ШТИ-КЕ 11 и ИЛИ 4 устанав ливаются соответственно О и 1. Ка остальных выходах дешифратора 1 сохраняются логические О, поэто му на выходах элементов ИЛИ-НЕ 1 U1 1J, присутствуют единичные сигналы, поступающие на входы соответствующих элементов 7j-7 , на других входах которых присутствуют I По импульсу с входа 16 синхронизации устанавливается в единичное состояние триггер и на вход коммутирующего элемента 8 поступает управляющий сигнал. Кроме того, импульс синхронизации проходит через 4 элементы И 72-/f и УЛИ . и устанавливает или подтверждает нулевое состояние триггеров , поддерживающих коммутирующие элементы , в закрытом состоянии. В момент поступления импульса синхронизации на вход 16 внешнему устройству вьщается сигнал с выхода 18 подтверждения, сигнализирующий о приеме вспомогательного сигнала управления данным интерфейсным блоком. Через время, меньшее f , подается на входы 13-15 интерфейсного блока основной сигнал управления Б.Р(1 ), Ф(25). При этом на выходе 20 дешифратора 1 появляется сигнал, вызывающий появление О на выходе элемента llJIH-HE 1 Ц и сигнала подтверждения на выходе 18, получаемого через элементы 8 и 4. ИмпулЬсы с входа 16 синхронизации поступают через элементы И на входы элементов ИЛИ lOg-lO, и далее на В- . входы триггеров , подтверждая тем самым их нулевое состояние. В момент поступления импульса синхронизации внешнему устройству выдается сигнал подтверждения о приеме основного сигнала управления интерфейсным блоком. Одновременно через управляющий вход .коммутатора 2 на выход поступает управляющий импульс. По оконча НИИ сигналов Б, PiП, Ф(25) запускается формирователь 12 импульсов, переводящий через элемент ИЛИ 10 триггер 6 в нулевое .положение. Устройство возвращается в исходное состояние . Таким образом, при поступлении вспомогательного сигнала управления с детерминированным опережением основного сигнала управления, что соответствует отсутствию каких-либо сбоев в управлении,-интерфейсный блок вырабатывает соответствующие сигналы подтверждения и требуемый исполнительный сигнал. Рассмотрим работу устройства при наличии программных или аппаратных сбоев значений входных сигналов блока. К таким сбоям можно, например, отнести искажение основного сигнала Б.Р1к)Ф() управления при его возникновении за время, меньшее f после наличия вспомогательного сигнала, задержку в поступлении основного сигнала Б,Р(к)Ф(е/ на время, большее Т ,.и искажение всромога

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для ввода информации | 1982 |

|

SU1056175A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для ввода информации | 1987 |

|

SU1509914A1 |

| Каскадный коммутатор | 1989 |

|

SU1608792A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

ИНТЕРФЕЙСНЫЙ БЛОК, содержащий дешифратор, первую группу выходных элементов ИЛИ и коммутатор, причем входы стробирования, адреса и информации блока соединены с входами дешифратора, вход синхронизации блока соединен с управляющим входом коммутатора, выходы которого являются .информационной группой выходов интерфейсного блока, выходы выходньк элементов ИЛИ группы образуют выход подтверждения блока, отличающийся тем, что, с целью повышения достоверности, в него введены группа передающих каналов, входной элемент ИЛИ и вторая группа выходных элементов ИЛИ, а каждый передающий канал содержит триггер, элементы И, ИЛИ, ШШ-НЕ, коммутирующий элемент, формирователь импульсов и элемент задержки, причем в каждом передающем канале выход триггера соединен с первым управляющим входом триггера и входами элемента задержки и управления коммутирующего элемента, выход которого соединен с входом формирователя импульсов, выход которого соединен с первым входом элемента I-LTIH, второй и третий ходы которого соединены соответственно с выходом элемента задержки и с выходом элемента И, выход элемента ИЛИ соединен с вторым управляющим входом триггера, выход элемента ИЛИ-НЕ - с первым входом элемента И, при этом первая группа выходов дешифратора соединена с информационными входами триггеров передающих каналов группы, вторая (Л группа,выходов - с входами коммутирующих элементов и с первыми входами элементов ИЛИ-НЕ соответствующих передающих каналов группы, вход синхронизации блока соединен с входом стробирования триггера и вторым входом элемента И каждого передающего канала группы, входы адреГС са и информации блока соединены с о оэ соответствующими входами входного элемента ИЛИ, выход которого соеди; нен с третьим входом элемента И каждого передающего канала группы, выход коммутирующего элемента каждого передающего кйнала соединен с соответствующим информационным входом коммутатора и с входами выходных элементов ИЛИ второй группы, выходы которых соединены с выходом подтверждения блока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Куценко А.Б | |||

| и др | |||

| Мини-ЭВМ | |||

| в экспериментальной физике | |||

| М., Атомиздат, 1975, с.95-101 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Титов Л.Г | |||

| и др | |||

| Типовой интерфейс функционального блока с каналом передачи данных.-Сб | |||

| Вопросы атомной науки и техники, сер | |||

| Ядерное приборостроение, вып | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| И., Атомиздат, 1974, с | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

Авторы

Даты

1984-10-23—Публикация

1983-05-30—Подача