Изобретение .относится к вычислительной технике и может быть использовано при решении задач матеметичес- кой физики.

Цель изобретения - повышение быстродействия устройства путем устранег нения операций умножения и деления.

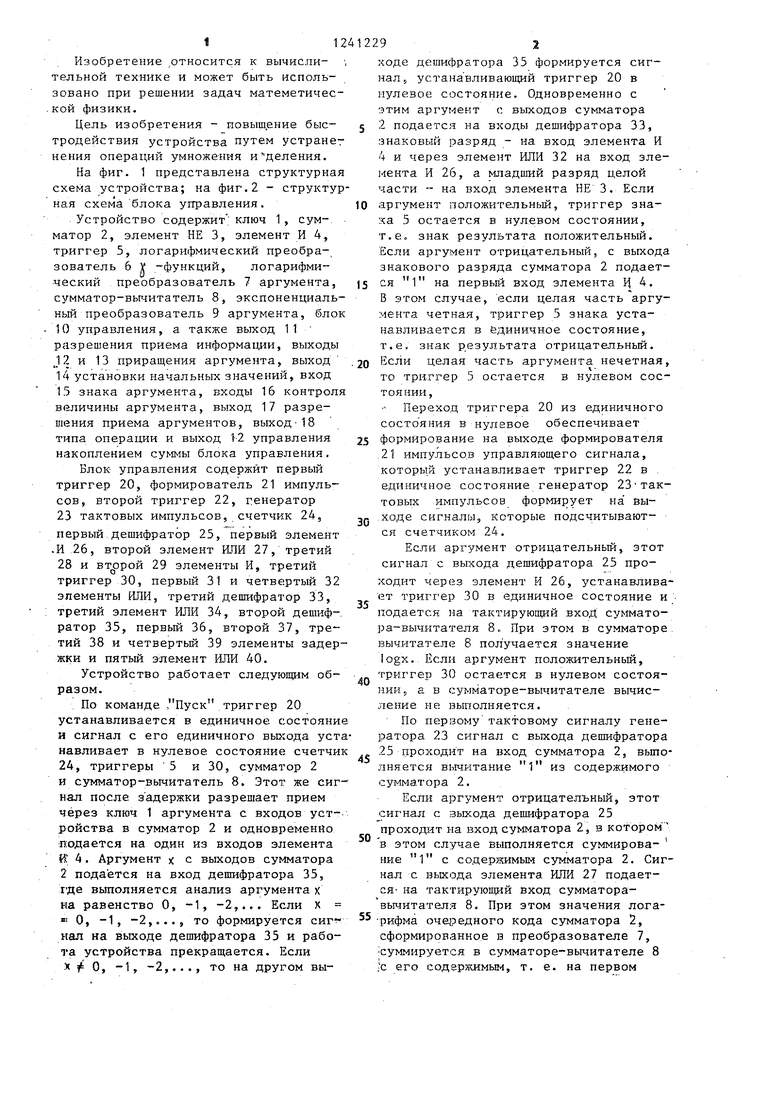

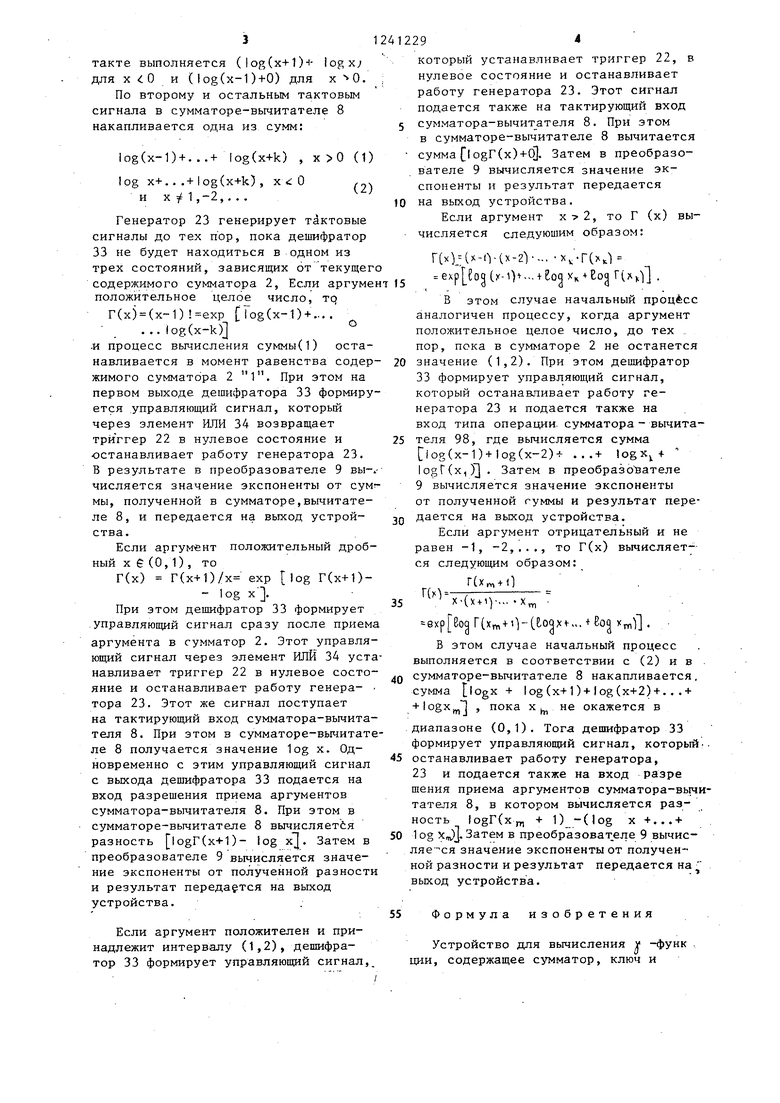

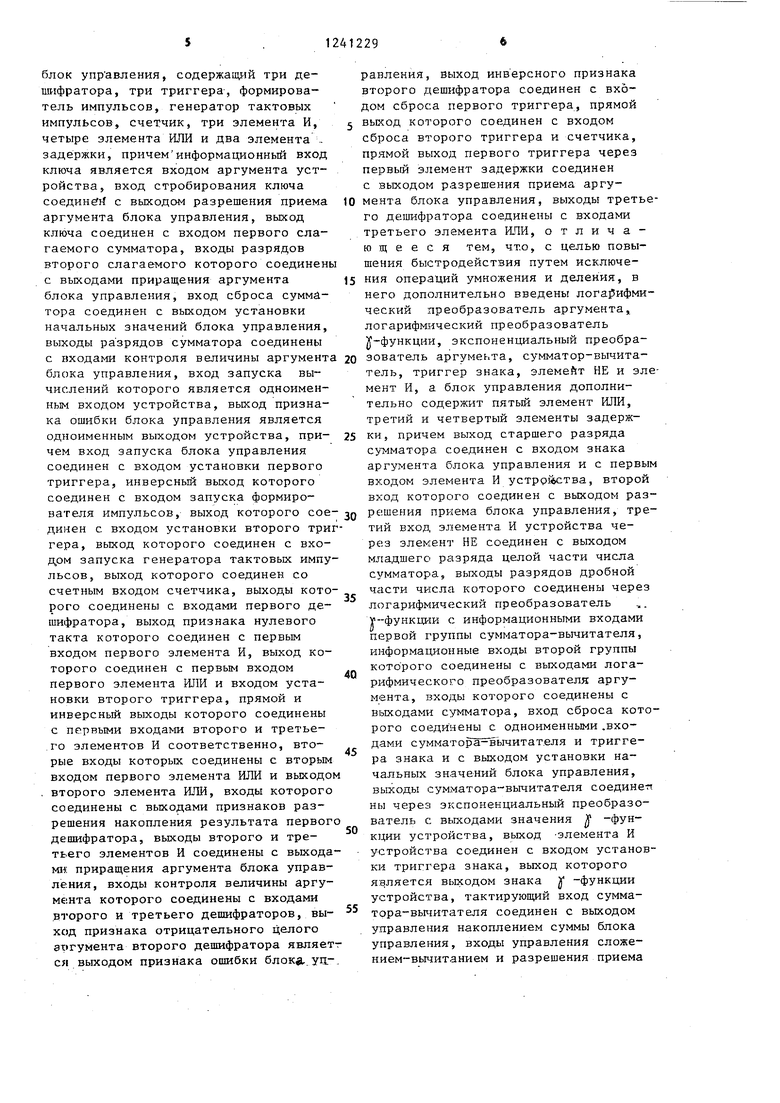

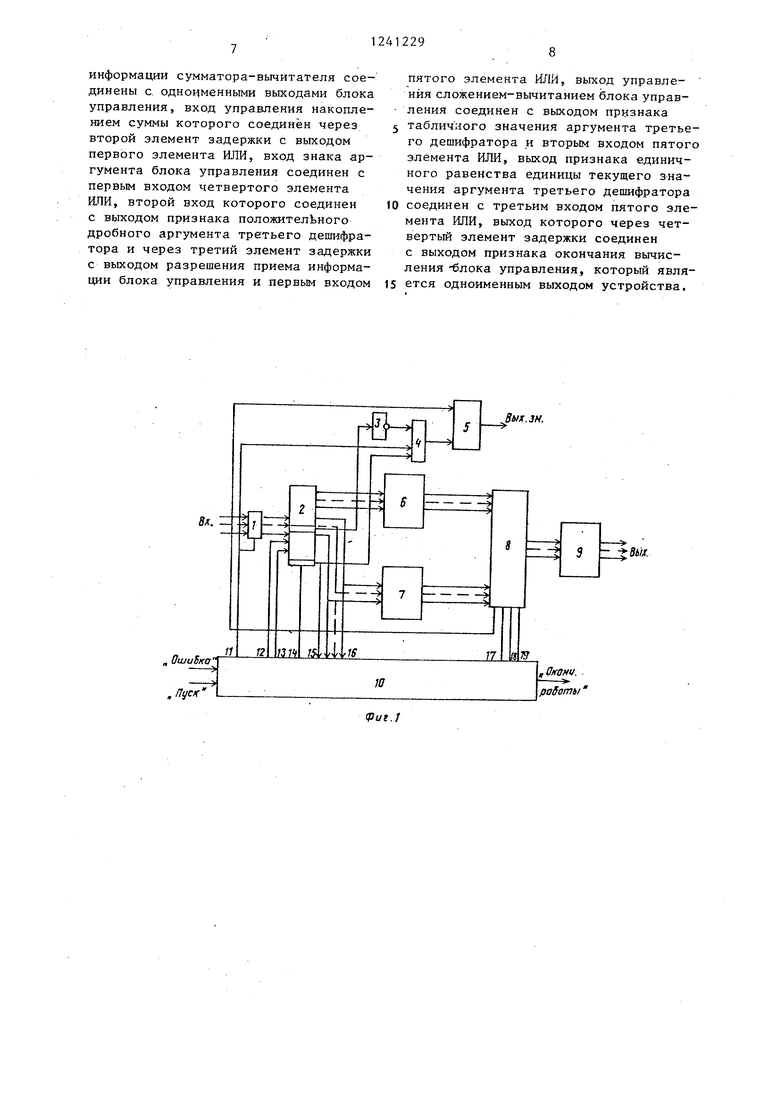

На фиг. 1 представлена структурная схема устройства; на фиг.2 - структурная схема блока управления.

Устройство содержит ключ 1 , сум-, матор 2, элемент НЕ 3, элемент И 4, триггер 5, логарифмический преобразователь 6 Y -функций, логарифмический преобразователь 7 аргумента, сумматор-вычитатель 8, экспоненциальный преобразователь 9 аргумента, блок 10 управления, а также выход 11 разрешения приема информащ и, выходы J2 и 13 приращения аргумента, выход

14установки начальных значений, вход

15знака аргумента, входы 16 контроля величины аргумента, выход 17 разрешения приема аргументов, выход-18 типа операции и выход 1-2 управления накоплением суммы блока управления.

Блок- управления содержит первый триггер 20, формирователь 21 импульсов, второй триггер 22, генератор 23 тактовых импульсов,,счетчик 24,

первый.дешифратор 25, первый элемент .И .26, второй элемент ИЛИ 27, третий 28 и второй 29 элементы И, третий триггер 30, первый 31 и четвертый 32 элементы ИЛИ, третий дешифратор 33, третий элемент ИЛИ 34, второй деишф-. ратор 35, первый 36, второй 37, третий 38 и четвертьш 39 элементы задержки и пятый элемент ИЛИ 40.

Устройство работает следующим образом.

По команде Пуск триггер 20 устанавливается в единичное состояние и сигнал с его единичного вьссода устанавливает в нулевое состояние счетчик 24, триггеры 5 и 30, сумматор 2 и сумматор-вычитатель 8. Этот же сигнал после задержки разрешает прием через ключ 1 аргумента с входов устройства в сумматор 2 и одновременно подается на один из входов элемента К 4. Аргумент х с выходов сумматора 2 подается на вход дешифратора 35, где выполняется анализ аргумента х на равенство О, -1, -2,... Если X О, -1, -2,..., то формируется сиг нал на выходе дешифратора 35 и работа устройства прекращается. Если О, -1, -2,..., то на другом вы

5

0

5

0

5

0

5

0

5

ходе дешифратора 35 формируется сигнал s устанавливающими триггер 20 в нулевое состояние. Одновременно с этим аргумент с выходов сумматора 2 подается на входы дешифратора 33, знаковый разряд - на вход элемента И 4 и через элемент ИЛИ 32 на вход элемента И 26, а младший разряд целой части - на вход элемента НЕ 3. Если аргумент положительный, триггер зна- :ха 5 остается в нулевом состоянии, т.бо знак результата положительный. Если аргумент отрицательный, с выхода знакового разряда сумматора 2 подается 1 на первьп вход элемента Н 4. В этом случае, если целая часть аргумента четная, триггер 5 знака устанавливается в единичное состояние, т.е. знак результата отрицатепьньй. Если целая часть аргумента нечетная, то триоггер 5 остается в нулевом состоянии.

Переход триггера 20 из единичного состояния в нулевое обеспечивает формирование на выходе формирователя .21 импульсов управляющего сигнала, который устанавливает триггер 22 в . единичное состояние генератор 23 тактовых импульсов формирует на вы- .ходе сигналы, которые подсчитываются счетчиком 24.

Если аргумент отрицательньй, этот сигнал с выхода дешифратора 25 проходит через элемент И 26, устанавлива- ет триггер 30 в единичное состояние и подается на тактируюш 1й вход суммато- ра-вычитателя В„ При этом в сумматоре, вычитателе 8 получается значение iogx. Если аргумент положительный, триггер 30 остается в нулевом состоянии s а в сумматоре-вычитателе вычисление не выполняется.

По первому тактовому сигналу генератора 23 сигнал с выхода дешифратора 25 цроходит на вход сумматора 2, вьшо- лняется вычитание 1 из содержимого сумматора 2.

Если аргумент отрицательный, этот сигнал с выхода дешифратора 25 проходит на вход сумматора 2, в котором в этом выполняется суммирова- ние нал

ся- на тактиру1ош 1й вход сумматора- вычитателя 8. При этом значения лога- рифма оче редного кода сумматора 2, сформированное в преобразователе 7, суммируется в сумматоре-вычитателе 8 : с его содержимым, т. е. на первом

1 с содержимым сумматора 2. Сиг- с выхода элемента ИЛИ 27 подаеттакте выполняется (log(x+1)- iogx; для X 0 и (log(x-1)+0) для X 0. По второму и остальным тактовым сигнала в сумматоре-вычитателе 8 накапливается одна из сумм:

log(x-1)+,..+ log(x+k)

log х+.. .+log(x+k) , X ; О и к 7 1 ,-2,...

, X

Генератор 23 генерирует тактовые сигналы до тех пор, пока дешифратор 33 не будет находиться в одном из трех состояний, зависящих от текущего содержимого сумматора 2, Если аргумен положительное целое число, Tq

Г(х) (х-1) ехр rog(x-1) + .... ...log(x-k)

-и процесс вьиисления суммы(1) останавливается в момент равенства содержимого сумматора 2 1. При этом на первом выходе дешифратора 33 формируется управляющий сигнал, который через элемент ИЛИ 34 возвращает трй ггер 22 в нулевое состояние и останавливает работу генератора 23. В результате в преобразователе 9 числяется значение экспоненты от сум

мы, полученной в сумматоре,вычитате- ле 8, и передается на выход устройства.

Если аргумент положительный дробный X в (0,1), то

Г(х) Г{хч-1)/х ехр log Г(х+1)- - log х .

При этом дешифратор 33 формирует управляющий сигнал сразу после приема аргумента в сумматор 2. Этот управляющий сигнал через элемент ИЛИ 34 устанавливает триггер 22 в нулевое состояние и останавливает работу генера- тора 23. Этот же сигнал поступает на тактирующий вход сумматора-вычитателя 8. При этом в сумматоре-вычитателе 8 получается значение log х. Одновременно с этим управляющий сигнал с выхода дешифратора 33 подается на вход разрешения приема аргументов сумматора-вычитателя 8. При этом в сумматоре-вычитателе 8 вычисляется разность logr(x+1)- log хJ. Затем в преобразователе 9 вычи сляется значение экспоненты от полученной разности и результат передается на выход устройства.

Если аргумент положителен и принадлежит интервалу (1,2), дешифратор 33 формирует управляющий сигнал,.

о нт 15

1241229

который устанавливает триггер 22, в нулевое состояние и останавливает работу генератора 23. Этот сигнал подается также на тактирующий вход 5 сумматора-вычитателя 8. При этом в сумматоре-вычитателе 8 вычитается

сумма ogr(x)+o. Затем в преобразователе 9 вычисляется значение экспоненты и результат передается

10 на выход устройства.

Если аргумент , то Г (х) вычисляется следующим образом:

r(x)(x-iV(x-zV... х,.Г(

(x-i)i.,,

XK +

.

В этом случае начальный процесс аналогичен процессу, когда аргумент положительное целое число, до тех пор, пока в сумматоре 2 не останется значение (1,2). При этом дешифратор 33 формирует управляющий сигнал, который останавливает работу генератора 23 и подается также на вход типа операции, сумматора - вьиитателя 98, где вычисляется сумма

iog(x-1)+1og(x-2)-b ...+ logr(x,)J . Затем в преобразо вателе 9 вычисляется значение экспоненты от полученной гуммы и результат передается на выход устройства.

Если аргумент отрицательный и не равен -1, -2,..., то Г(х) вычисляется следующим образом: Г(х + (1

г(М

ех

(х + 1)-... -х .

riKm+O-l O - Og l

в этом случае начальный процесс выполняется в соответствии с (2) и в сумматоре-вычитателе 8 накапливается, сумма logx + log(х+1)+log(x+2)+...+ + , пока X не окажется в

диапазоне (0,1). Тога дешифратор 33

формирует управляющий сигнал, который-.

45 останавливает работу генератора, 23 и подается также на вход разре шения приема аргументов сумматора-вь1чи- тателя 8, в котором вычисляется разность logr(x + 1)-(log X -Н...+

50 log xjj.Затем в преобразоват еле 9 вычис- значение экспоненты от полученной разности и результат передается на выход устройства.

55 Формула изобретения

Устройство для вычисления у -функ ции, содержащее сумматор, ключ и

блок упр авления, содержзЕДЯй три дешифратора, три триггера, формирователь импульсов, генератор тактовых импульсов, счетчик, три элемента И, четыре элемента ИЛИ и два элемента .. задержки, причем информационный вход ключа является входом аргумента устройства, вход стробирования ключа соединяй с выходом разрешения приема аргумента блока управления, выход ключа соединен с входом первого слагаемого сумматора, входы разрядов второго слагаемого которого соединен с выходами приращения аргумента блока управления, вход сброса суммй- тора соединен с выходом установки начальных значений блока управления, выходы разрядов сумматора соединены с входами контроля величины аргумент блока управления, вход запуска вычислений которого является одноименным входом устройства, выход признака ошибки блока управления является одноименным выходом устройства, причем вход запуска блока управления соединен с входом установки первого триггера, инверсньш выход которого соединен с входом запуска формирователя импульсов, выход которого соединен с входом установки второго тригера, выход которого соединен с входом запуска генератора тактовых импульсов, выход которого соединен со счетным входом счетчика, выходы которого соединены с входами первого дешифратора, выход признака нулевого такта которого соединен с первьм входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ и входом установки второго триггера, прямой и инверсный выходы которого соединены с первыми входами второго и третьего элементов И соответственно, вторые входы которых соединены с вторым входом первого элемента ИЛИ и выходо . второго элемента ИЛИ, входы которого соединены с выходами признаков разрешения накопления результата первог дешифратора, выходы второго и третьего элементов И соединены с выхода Mif приращения аргумента блока управления, входы контроля величины аргу- ме .нта которого соединены с входами второго и третьего дешифраторов, выход признака отрицательного целого аргумента второго дешифратора являет ся выходом признака ошибки блока,, уц0

5

0

5

0

5

0

5

равления, выход инв ерсного признака второго дешифратора соединен с входом сброса первого триггера, прямой выход которого соединен с входом сброса второго триггера и счетчика, прямой выход первого триггера через первый элемент задержки соединен с выходом разрешения приема аргумента блока управления, выходы третьего дешифратора соединены с входами третьего элемента ИЛИ, отличающееся тем, чт.о, с целью повышения быстродействия путем исключения операций умножения и деления, в него дополнительно введены логарифмический преобразователь аргумента логарифмический преобразователь -функции, экспоненциальный преобразователь аргумента, сумматор-вычита- тель, триггер знака, элемеАт НЕ и элемент И, а блок управления дополнительно содержит пятый элемент ИЛИ, третий и четвертый элементы задержки, причем выход старшего разряда сумматора соединен с входом знака аргумента блока управления и с первым входом элемента И устройства, второй вход которого соединен с выходом разрешения приема блока управления, третий вход элемента И устройства через элемент НЕ соединен с выходом младшего разряда целой части числа сумматора, выходы разрядов дробной части числа которого соединены через логарифмический преобразователь -функции с информационными входами первой группы сумматора-вычитателя, информационные входы второй группы кото рого соединены с выходами логарифмического преобразователя аргумента, входы которого соединены с выходами сумматора, вход сброса которого соединены с одноименными .входами сумматора ычитат.еля и триггера знака и с выходом установки начальных значений блока управления, выходы сумматора-вычитателя соединегт ны чере;1 экспоненциальный преобразователь с выходами значения -фун- кц;ии устройства, выход -элемента И устройства соединен с входом установки триггера знака, выход которого является выходом знака у -функции устройства, тактируюш й вход сумматора-вьиита т ел я соединен с выходом управления накоплением суммы блока управления, входы управления сложе- нием-вьиитанием и разрешения приема

информации сумматора-вычитателя соединены с одноименными выходами блока управления, вход управления накоплением суммы которого соединён через второй элемент задержки с выходом первого элемента ИЛИ, вход знака аргумента блока управления соединен с первым входом четвертого элемента RflH, второй вход которого соединен с выходом признака положительного дробного аргумента третьего дешифратора и через третий элемент задержки с выходом разрешения приема информации блока управления и первым входом

пятого элемента ИЛИ, выход управления сложением-вычитанием блока управ- ления соединен с выходом признака 5 табличного значения аргумента третьего дешифратора и вторым входом пятого элемента ИЛИ, выход признака единичного равенства единицы текущего значения аргумента третьего дешифратора

Ш соединен с третьим входом пятого элемента ИЛИ, выход которого через чет- вертьм элемент задержки соединен с выходом признака окончания вычисления -блока управления, который явля15 ется одноименным выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2513683C1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU926666A2 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU744590A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

Изобретение относится к области вычислительной техники и позволяет сократить время вычислений у -функций путем устранения операций умножения и деления. Устройство содержит ключ, сумматор, элемент КЕ. элемент И, триггер, логарифмический преобразователь -функций, логарифмический преобразователь аргумента,сумматор- вычитатель, экспоненциальный преобразователь аргумента и блок управления. Б зависимости от величины аргумента X блок управления задает соответствующую последовательность вычислений у-функции Г(Х). ЕслиХ О, -1, -2,..., то формируется сигнал ошибки и работа устройства прекращается. 2 ил. с to 4; 1C ю QD

Вых.зн.

- 54ЛГ.

раВогпы

11 fZ 3 fif 5 №

Ouiufn

Пуск

Редактор A.Orap

Составитель С.Куликов

Техред Н.Ванкало Корректор В.Бутяга

Заказ 3489/43Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

n }9 13

A n

I

OifOHff.

j

Sow

-r-

25

| Устройство для вычисления Г-функций | 1979 |

|

SU922759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления @ -функций | 1983 |

|

SU1124321A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-30—Публикация

1984-10-02—Подача