1206767

Изобретение относится к области вычислительной техники и может быть использовано для ускоренного вычисения функций F(х, у) от двух аргуентов в специализированных ЭВМ. 5

Цель изобретения - расширение функциональных возможностей за счет ычисления функций двух переменных.

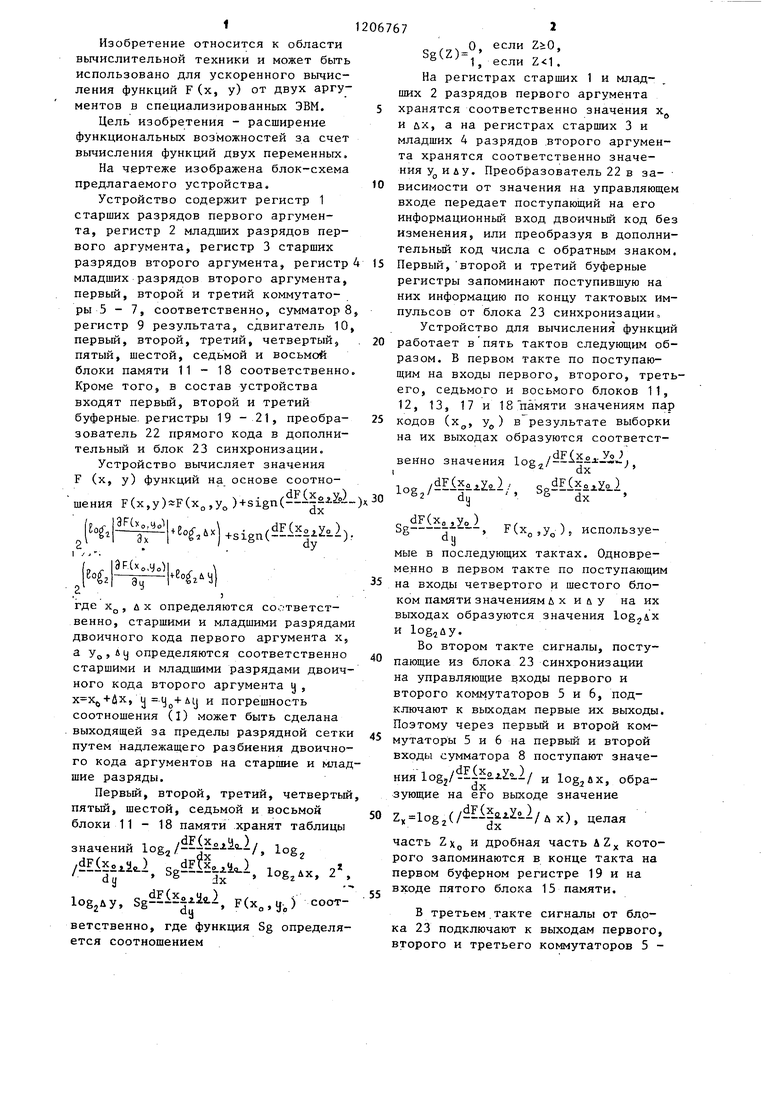

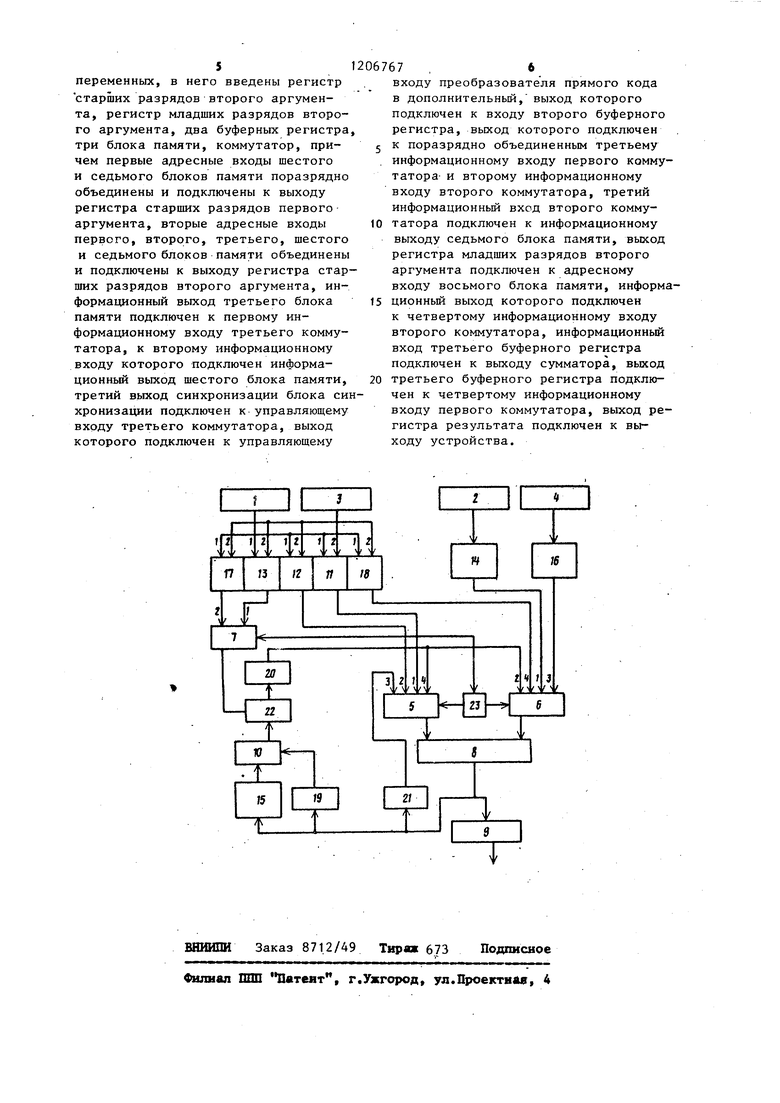

На чертеже изображена блок-схема предлагаемого устройства.10

Устройство содержит регистр 1 тарших разрядов первого аргумена, регистр 2 младших разрядов перого аргумента, регистр 3 старших азрядов второго аргумента, регистр 4 15 ладших разрядов второго аргумента, ервый, второй и третий коммутаторы 5 - 7, соответственно, сумматор 8, егистр 9 результата, сдвигатель 10, первый, второй, третий, четвертый, . 20 пятый, шестой, седьмой и восьмой блоки памяти 11 - 18 соответственно. Кроме того, в состав устройства входят первый, второй и третий буферные, регистры 19 - 21, преобра- 25 зователь 22 прямого кода в дополнительный и блок 23 синхронизации.

Устройство вычисляет значения F (х, у) функций на основе соотношения F(x,y):F(x,y

NlFbo,i)o1 . 37- 4.|+signC - -- y

),3ign()x30

dx

.,, . ,dF(xo,y « M+SlgnC;т,

40

45

|ч, Ч.

.

где Xjj, U X определяются соответственно, старшими и младшими разрядами двоичного кода первого аргумента х, а УО,А у определяются соответственно старшими и младшими разрядами двоичного кода второго аргумента у, , ij . и погрешность соотношения (I) может быть сделана выходящей за пределы разрядной сетки путем надлежащего разбиения двоичного кода аргументов на старшие и младие разряды.

Первый, второй, третий, четвертый, ятый, шестой, седьмой и восьмой блоки 11 - 18 памяти хранят таблицы

„ , ,dF(xo,y.,)/ 1 значении г ) S ,,) г dy dx

lOgjAy, Sg i2iii«.), р(х„,1,„) COOTетственно, где функция Sg определятся соотношением

ши хр и мл та н ви вх ин из те Пе ре ни пу

ра ра щи ег ко на ве

io

Sg

50

55

мы ме на к вы и

па на вт кл По му вх

ни зу

Z,

ча ро пе вх

ка вт

5 0 5

0

0

5

с (z)-0. 1, если .

На регистрах старших 1 и младших 2 разрядов первого аргумента хранятся соответственно значения х и UX, а на регистрах старших 3 и младших 4 разрядов второго аргумента хранятся соответственно значения у илу. Преобразователь 22 в зависимости от значения на управляющем входе передает поступающий на его информационный вход двоичный код без изменения, или преобразуя в дополнительный код числа с обратным знаком. Первый, второй и третий буферные регистры запоминают поступившую на них информацию по концу тактовых импульсов от блока 23 синхронизации.

Устройство для вычисления функций работает в пять тактов следующим образом. В первом такте по поступающим на входы первого, второго, третьего, седьмого и восьмого блоков 11, 12, 13, 17 и 18 памяти значениям пар кодов (х, Ур) в результате выборки на их выходах образуются соответственно значения log /-iSij;-.

iog,, .

Sg

d dF(x« ,y,

)

)

dx

F(x ,УО)( используе0

5

мые в последующих тактах. Одновременно в первом такте по поступающим на входы четвертого и шестого блоком памяти значениям д х и л у на их выходах образуются значения и log,juy.

Во втором такте сигналы, поступающие из блока 23 синхронизации на управляющие входы первого и второго коммутаторов 5 и 6, подключают к выходам первые их выходы. Поэтому через первый и второй коммутаторы 5 и 6 на первый и второй входы сумматора 8 поступают значе

нияlog / oAZU/ и , образующие на его выходе значение

Z,log,()), целая

часть ZX(, и дробная часть kZ которого запоминаются в конце такта на первом буферном регистре 19 и на входе пятого блока 15 памяти.

В третьем такте сигналы от блока 23 подключают к выходам первого, второго и третьего коммутаторов 5 7 соответственно второй, третий и первый их входы. ПятьВГ блок 15 памяти путем выборки из хранящейся в нем таблицы значений 2 осуществляет преобразование , резуль тат которого поступает на информационный вход сдвигателя 10, а на управляющий его вход с выхода первого буферного регистра 19 подается значение . Сдвигатель 10 сдвигает

А

значение 2 на ZXQ двоичных разрядов, образуя результат 2 2 :

. 2

, который передается через

преобразователь 22 кода, учитывающий знак значения так как

на его управляющий вход через третий коммутатор 7 поступает значение . Результат

F -I.. их запоминается в конце X dx такта на втором буферном регистре 20. Одновременно, на первьй и второй входы сумматора 8 через первый и второй коммутаторы 5 и 6

поступают значения log,

2 dy

и log А и, образующие на его выходе значение Z log2 ( ),

целая часть Z и дробная часть которого запоминаются по концу такта соответственно на первом буферном регистре 19 и входе пятого бло- |Ка 15 памяти.

В четвертом такте сигналы от блока 23 подключают к выходам первого, второго и третьего коммутаторов 5 - 7 соответственно четвертый, четвер- тьй и второй их входы. Поэтому на первьй и второй входы сумматора 8 пступают значения F ,и Г(Кд,Уо), результат сложения которых (Хд,Уд запоминается в конце такта на третьем буферном регистре 21. Одновременно пятьй блок 15 памяти выполняет преобразование uZy- 2 , сдвига- тель 10 путем сдвига 2 на Z двоичных разрядов формирует значение 2 Ч, передаваемое через преобразователь 22, на управляющий вход которого через третий коммутатор 7

dF(xoiXL) da

dF(xo,4o ) разованием значения

запоминаемого на втором буферном регистре 20.

поступает значение Sgс обЛУ

яльоет

к

е

-

о, - - по) ьн

бУ.

1206767

В пятом такте сигналы от блока 23 подключают к выходам первого и второго коммутаторов 5 и 6 третий и второй их входы соответственно. Поэтому

5 3 сумматоре 8 происходит сложение значения F(Xg, у )+Fx из третьего буферного регистра 21 и значения FU с второго буферного регистра 20. Результат, равный в соответствии 10 с (1) значению функции F(x, у), запоминается на регистре 9 результата.

Формула изобретения

5 Устройство для вычисления функций, содержащее блок синхронизации, сумматор, регистр результата, регистр старших разрядов первого аргумента, регистр младших разрядов первого ар2Q гумента, сдвигатель, преобразователь прямого кода в дополнительньй, два коммутатора, первьй буферньй регистр, пять блоков памяти, причем выход регистра старших разрядов первого аргу25 мента подключен к поразрядно объединенным первым адресным входам первого, второго и третьего блоков памяти, информационные выходы первого и второго блоков памяти подключены соот - ветственно к первому и второму информационным входам первого коммутатора, выход которого подключен к первому информационному входу сумматора, выход регистра младших разрядов перво го аргумента подключен к адресному входу четвертого блока памяти, выход которого йодключен к первому информационному входу второго коммутатора, выход которого подключен к второму информационному входу сумматора, выход которого подключен к поразрядно объединенным входам регистра результата, первого буферного регистра и адресному входу пятого блока памяти, информационньй выход которо 5 го подключен к информационному входу сдвигателя, управляющий вход которого подключен к выходу первого буферного регистра, выход сдвигателя подключен к информационному входу

50 преобразователя прямого кода в дополнительньй, первьй и второй выходы синхронизации блока синхронизации подключены соответственно к управляющим входам первого и вто55 рого коммутаторов, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычислений функций двух

35

40

переменных, в него введены регистр старших разрядов второго аргумента, регистр младших разрядов второго аргумента, два буферных регистра три блока памяти, коммутатор, причем первые адресные входы шестого и седьмого блоков памяти поразрядно объединены и подключены к выходу регистра старших разрядов первого аргумента, вторые адресные входы первого, второго, третьего, шестого и седьмого блоков памяти объединены и подключены к выходу регистра стар- пшх разрядов второго аргумента, информационный выход третьего блока памяти подключен к первому информационному входу третьего коммутатора, к второму информационному входу которого подключен информационный выход шестого блока памяти, третий выход синхронизации блока синхронизации подключен к управляющему входу третьего коммутатора, выход которого подключен к управляющему

входу преобразователя прямого кода в дополнительный, выход которого подключен к входу второго буферного регистра, выход которого подключен к поразрядно объединенным третьему информационному входу первого коммутатора- и второму информационному входу второго коммутатора, третий информационньш вход второго коммутатора подключен к информационному выходу седьмого блока памяти, выход регистра младших разрядов второго аргумента подключен к адресному входу восьмого блока памяти, информационньй выход которого подключен к четвертому информационному входу второго коммутатора, информационный вход третьего буферного регистра подключен к выходу сумматора, выход

третьего буферного регистра подключен к четвертому информационному входу первого коммутатора, выход регистра результата подключен к выходу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1236465A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Цифровой генератор функций | 1978 |

|

SU750467A1 |

Изобретение относится к области вычислительной техники и может быть использовано для ускоренного вычисления функций F (х,у) от двух аргументов в специальных ЭВМ. Цель изобретения - расширение функциональных возможностей устройства за счет вы- числения функций двух переменных. Устройство содержит регистр старших разрядов первого аргуме.нта, регистр младших разрядов первого аргумента, регистр старших разрядов второго аргумента, регистр младших разрядов второго аргумента, первьш, второй и третий коммутаторы, сумматор, регистр результата, сдвигатель, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой блоки памяти, первый, второй и третий буферные регистры, преобразователь прямого кода в дополнительный и блок синхронизации. Вычисление функций двух переменных обеспечивается введением регистров старших и младших разрядов второго аргумента, двух буферных регистров, трех блоков памяти и коммутатора. 1 ил. (П

| Устройство для сбора и удаления мусора | 1987 |

|

SU1413045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-01-23—Публикация

1984-07-04—Подача