один разряд в сторону младших разрядов третьего сумматора, йторая группа входов которого подключена к выходам второго блока памяти, выход первого разряда восьмого регистра соединён с управляющим входом коммутатора, первая группа информационных входов которого соединена с выхо дом третьего сумматора, выходы которого соединены с информационными входами второй группы со сдвигом на один разряд в сторону младших разрядов коммутатора, выход которого соединен с информационным входом выходного регистра мантиссы, выход которого подключен к выходу мантиссы устройства, выход второго сумматора соединен с информационным входом выходного регистр{а порядка, выход кото рого соединен с выходом порядка устройства, первый вход блока синхронизации подключен к входу пуска устройства, второй вход блока синхро .низации соединен с входом сброса уст ройства, первый выход режима блока синхронизации подключен к выходу считывания устройства, первый выход синхроимпульсов блока синхронизации соединеи с синхровходами входных регистров порядка и мантиссы, второй выход синхроимпульсов блока синхронизации подключен к синхровходам первого и второго,регистров, третий выход синхроимпульсов блока синхронизации соединен с синхровходами третьего, четвертого и пятого регистров, четвертый выход синхроимпульсов блока синхронизации подключен к синхровходам шестого, седьмого и восьмого регистров , пятый выход синхроимпульсов блока синхронизации соединен с синхровходами выходных регистров порядка и мантиссы, второй выход синхроимпульсов блока синхронизации подключен к синхровходам. первого и второго регистров, третий выход, синхроимпульсов блока синхронизации соединен с синхровходами третьего, четвертого и пятого регистров, четвертый выход синхроимпульсов блока синхронизации подключен к синхровходам шестого, седьмого и восьмого регистров, пятый выход синхроимпульсов блока синхронизации соединен с синхровходами выходных регистров порядка и мантиссы, второй выход режима блока синхронизации подключен к выходу записи устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления функции синуса | 1987 |

|

SU1474642A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БЫСТРЫХ ГЕОМЕТРИЧЕСКИХ ПРЕОБРАЗОВАНИЙ | 1991 |

|

RU2020557C1 |

| Вычислительное устройство | 1986 |

|

SU1325468A1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для потенцирования массивов двоичных чисел | 1982 |

|

SU1043646A1 |

КОНВЕЙЕРНОЕ УСТРОЙСТВО ДЛЯ ПОТЕНЦИРОВАНИЯ МАССИВОВ ДВОИЧНЫХ ЧИСЕЛ, содержащее входной регистр порядка, входной регистр мантиссы, выходной регистр порядка, выходной регистр мантиссы, два сумматора, первый блок памяти, причем вход мантиссы устройства соединен с информационным входом входного регистра мантиссы, отличаю- щ е е с я тем, что, с целью повышения быстродействия, в него введены восемь регистров, блок сдвига, второй блок памяти, третий сумматор, квадратор, коммутатор, блок синхронизации и элемент НЕ, причем вход порядка устройства соединен с информационным входом входного регистра порядка, выход которого подключен к управляющему входу блока сдвига, информационные входы которого соединены с выходами (п-1) младших разрядов входного регистра мантиссы (где п - число разрядов входного регистра мантиссы) ,- выход первого разряда которого соединен с информационными входами первых разрядов первого и второго регистров, информационные выходы блока сдвига подключены к информационным входам (п-1) млацших разрядов втррого регистра, выходы К разрядов которого соединены с адресными входами первого блока памяти (где К - число старших разрядов второго регистра), выход первого блока памяти подключен к первому входу первого- сумматора, второй вход которого соединен с выходом второго регистра, вькоды (f-l) младших разрядов блока сдвига подключены к информационным входам (-1) младших разрядов первого реi гистра (где - число старших разрядов блока сдвига), выход первого (Л регистра соединен с информационным входом третьего регистра, выход первого . сумматора подключен к информационному входу четвертого регистра, выходы К разрядов второго регистра соединены с информационными входами пятого регистра, выход третьего со регистра подключен к информационному входу шестого регистра, выход четвер) того регистра соединен с входом квадО ратора, выход которого соединен с информационным входом седьмого регисо стра, выход пятого регистра соеди- нен с информационным входом восьмого регистра, выход которого подключен к адресному входу второго блока памяти, выход шестого регистра соединен с первым входом второго сумматора, младший разряд второго входа которого через элемент НЕ подключен к выходу первого разряда восьмого регистра, выход седьмого регистра соединен с входом первой группы со сдвигом на

1

Изобретение относится к вычислительной технике и предназначено для использоваШ1я в универсальных и спе циализлрованных вычислительных устройствах при обработке больших массивов данных, в формате с плавающей запятой.

Цель изобретения - повьш1ение бысродействия.

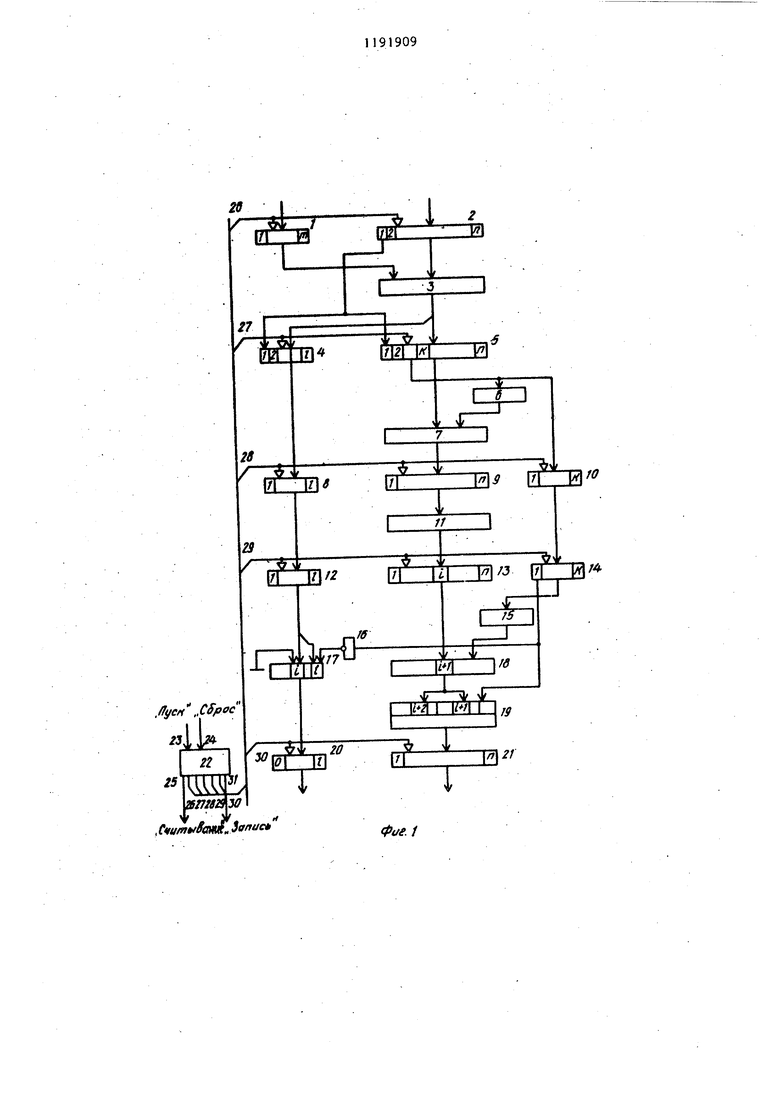

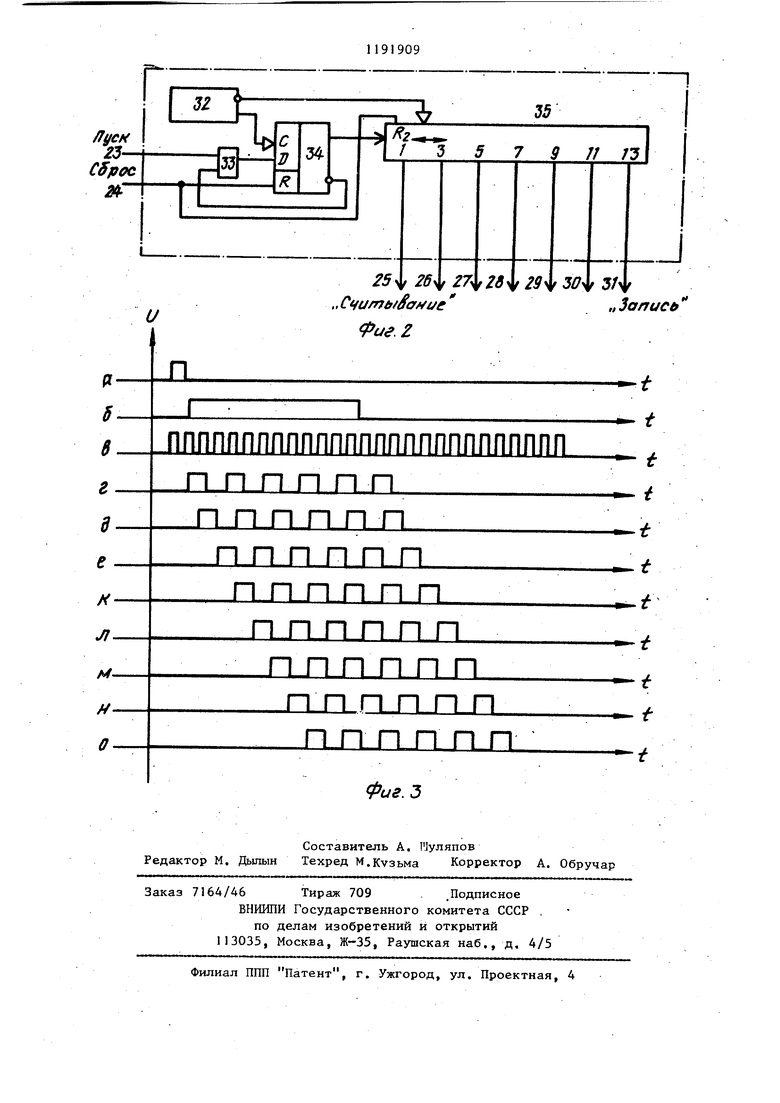

На фиг. 1 представлена функциональная схема устройства для потенцирования массивов двоичных чисел; на фиг. 2 - блок синхронизации; на фиг. 3 - временные диаграммы работы устройства.

; Устройство для потенцирования массивов двоичных чисел содержит входной регистр порядка 1, входной регистр мантиссы 2, блок сдвига.3, первый и второй регистры 4 и 5, первый блок памяти 6, первый сумматор

7, третий, четвертый и пятый реги.стры 8, 9 и 10, квадратор 11, шес той, седьмой и восьмой регистры 12, 13 и 14, второй блок памяти 15, зле5 мент НЕ 16, второй и третий сумматоры 17 и 18, коммутатор 19, выходной регистр порядка 20, выходной регистр мантиссы 21, блок синхрони. зации 22 с входами 23 и 24 и выхода-

10 ми 25-31. Блок синхронизации 22

(фиг. 2 ) содержит генератор импульсов 32, элемент И 33, триггер 34 и сдвиговьй регистр 35, причем прямой выход генератора импульсов 32 соеди-

15 нен со стробирующим входом триггера 34, а инверсный выход - со стробирующим входом сдвигового регистра 35. Вход Сброс 24 соединен с входами сброса триггера 34 и сдвигового

20 регистра 35. Вход Пуск 23 соединен с первым входом элемента И 33, второй вход которого соединен с ин- версным выходом триггера 34, Выход элемента И 33 соединен с информационным входом триггера 34, прямой выход которого соединен с информационным входом сдвигового регистра 35. Выход первого разряда сдвигового регистра 35 соединен с выходом 25 Считывание блока синхронизации 22, выход третьего разряда - с выходом 26,выход пятого разряда с выходом 27,выход седьмого разряда - с выходом 28, выход девятого разряда - с выходом 29, выход одиннадцатого разряда - с выходом 30, выход тринадцатого разряда - с выходом 31 Запись блока синхронизации 22, первый выход 26 блока синхронизации 22 соединен с сиихровходами выходньпс регистров порядка и мантиссы I и 2, второй выход 27 - с синхровходами первого .и второго регистров 4 и 5, третий и четвертый выход 28 - с синхровходами третьего, четвертого и пятого регист ров 8, 9 и 10, четвертый выход 29 с сихровходами шестого, седьмого и восьмого регистров 12, 13 и 14, пяты ВЫХОД 30 - с синхровходами выходных регистров порядка и мантиссы 20 и 21 Выходы входного .регистра порядка 1 соединены с управлякхцими входами блока сдвига 3, информационные входы которого соединены с выходами всех разрядов входного регистра мантиссы 2, исключая первый (знаковый). Выход

первого разряда входного регистра мантиссы 2 соединен с входами первых разрядов первого и второго регистров 4 и 5, входы остальных разрядов которых соединены с выходами блока до сдвига 3. Выходы второго регистра 5 соединены с первыми входами первого сумматора 7, вторые входы которого соединены выходами первого блока памяти 6. Кроме того, выходы К старших45 разрядов второго регистра 5 соединены с адресными входами первого блока, .памяти 6 и входами пятого регистра, 10. Выходы первого сумматора 7 соединены с входами четвертого регистра 50 9. Выходы, четвертого регистра 9 соединены с входами квадратора 11, выходы которого соединены с входами седьмого регистра 13. Вьпсоды пятого регистра 10 соединены с входами вось- 55 мого регистра 14. Выходы восьмого регистра 14 соединены с адресными .. Ьходами второго блока памяти 15.

татов промежуточных вычислений и для обеспечения конвейерного способа обработки. Регистры 5, 9 и 13 имеют разрядность п, регистры 4, 8 и 12 разрядность I, а регистры 10 и 14 разрядность К, при этом , а К определяется из условий приближения.

Вычисление функции у « 2 от аргумента X (|х1 2.)производится следующим образом.

В форме с плавающей запятой аргумент X представляется в виде

2

X 2;

где z - мантисса аргумента (0,5 i

z,kl);

Zj - порядок аргумента ( ). Денормализуем аргумент, т.е. представим его в виде целой и дробной части

, Кроме зтого, выход первого разряда восьмого регистра 14 соединен с входом элемента НЕ 16 и управляющим вхо дом коммутатора 19. Выходы второго блока памяти 15 соединены с вторыми входами третьего сумматора 18, первые входы которого соединены с выходами седьмого регистра 13 со сдвигом на один разряд влево. Выходы третьего сумматора 18 соединены с первыми входами коммутатора 19 со сдвигом на один разряд вправо. Вторые входы коммутатора 19 соединены с выходами третьего сумматора 8 без сдвига. Выходы коммутатора соединены с. входами выходного регистра мантиссы 21. Выход элемента НЕ 16 соединен с вторым входом младшего разряда второго сумматора 17. На вторые входы остальньк разрядов второго сумматора 17 подан потенциал О. Первые входы второго сумматора 17 соединены через шестой и третий регистры 12 и 8 с выходами первого ре1 истра 4, Выходы второго сумматора 17 соединены с входами выходного регистра порядка 20. Коммутатор может быть выбран любым, обладающим достаточным быстродействием. Блок сдвига легко построить при помощи селекторов-мультиплексоров. Принцип построения быстродействующего сдвигателя известен. Первый-восьмой регистры 4, 5, 8, 9, 10, 12,13 и 14 предназначены для кратковременного запоминания резуль- где z, - целая часть аргумента (Uj|c2); 84 дробная часть аргумента (. Заметим, что знак Zj и z определяется знаком мантиссы аргумента. Вычисление функции у 2 произведем следующим образом: При положительном аргументе х величина z также положительна и имеет место выражение При отрицательном аргументе х 0,5i (z О) . Поэтому при 2отрицательном аргументе величина 2 представляет собой мантиссу выходного числа, а величин z - порядок. При положительном аргу менте величину можно нормализовать путем сдвига на один разряд вправо. В этом случае мантисса выходного чи ла равна 0,52 а порядок - Zj + Денормализация аргумента производится : блоке сдвига 3. 2( Вычисление функции у производится на основе метода сегмен ной аппроксимации выражением у, А 0,5 (х + В) , где константы А и В выбираются из условия минимизации абсолютной погрешности. Диапазон изменения аргумента (-1 -Z i i) разбивается на интервалы количество которых определяется требуемой точностью, причем границы интервалов выражаются К старшими ра рядами аргумента. На разных интервалах константы А и В имеют различные значения. Кон станты В хранятся в первом блоке памяти 6, а коистанты А - во втором блоке памяти 15. Адресация к каждом блоку памяти ос.уществляется по К старшим разрядам аргумента, которые определяют в каком интер-вале находится аргумент. Устройство работает следующим образом. Перед началом работы устройства по сигналу Сброс 24 (фиг. За) триггер 34 и сдвиговый регистр 35 блока синхронизации 22 приводятся в исходное состояние. По сигналу Пуск 23 (фиг. 36) элемент И 33 пропускает си.нал с инверсного выхода триггера 34 на информационный вход этого же триггера. Триггер 34 работает в режиме деления частоты генератора импульсов 32 (фиг. 3 в ) на два (фиг. 3 г). По заднему фронту сигнала генератора импульсов 32 информация с выхода триггера 34 заносится в сдвиговый регистр 35. В результате работы устройства на выходах 25-31 блока синхронизации 22 вырабатывается, лесенка импульсов управления внутренних регистров устройства и внеш- . них схем памяти. При этом выход 25 Считывание(фиг. 3 д )используется для управления считывания очередного слова данных из внешней памяти, выход 26 (фиг. 3 е) - для управления заносом чисел в регистры 1 и 2, выход 27 (фиг. 3 к) - в регистры 4 и 5, выход 28 (фиг. 3 л) - в регистры 8-10, выход 29 (фиг. 3 м) - в регистры 12-14, выход 30 (фиг. 3 н) в регистры 20 и 21, выход 31 (фиг. 3 о) - для управления записью результата во внешнюю память. После снятия сигнала Пуск 23 блок синхронизации 22 прекращает вырабатывать сигналы управления, начиная с верхних ступеней конвейера. Таким образом обеспечивается корректное завершение обработки операндов, находящихся во внутренних регистрах устройства во время снятия сигнала Пуск 23. В первом такте работы устройства в регистр 1 поступает порядок аргумента к , а в регистр 2 - мантисса. С выхода регистра 1 значение порядка аргумента поступает на управляю- щие входы блока сдвига 3. При этом первый (знаковый) разряд указывает на направление сдвига (1 - сдвиг вправо, О - сдвиг влево), а число, определяемое разрядами 2-т регистра 1,- на количество сдвигов. Значащие разряды регистра мантиссы 2 (2-п) поступают на информационные входы блока сдвига 3, где производится Денормализация аргумента х. Во втором такте значение знака аргумента х. записывается в первые (знаковые) разряды регистров 4 и 5, в разряды 2 - Г регистра 4 записывается целая часть аргумента х, а в разряды 2-п регистра 5 - дробная 7 часть аргумента х. В регистры 1 и 2 записываются значения порядка и мантиссы нового аргумента х. С выхода регистра 5 значение дробной части аргумента х поступает на сумматер 7, Одновременно из блока памяти 6 по адресу, указанному К старшигми разрядами дробной части аргумента X, выбирается константа В и также поступает на сумматор 7, В сумматоре 7 производится выработка суммы zv + + ВЧ В третьем такте значение + В записывается в регистр 9 и возводится в квадрат в квадраторе 11. Одновременно значение К старших разрядов .дробной части аргумента х записывается в регистр 10, а целая часть аргумента X из регистра 4 переписывает ся в регистр 8. В том же такте в ре- гистры и 2 заносятся порядок и ман тисса нового числа Xj, а в регистры 4 и 5 - целая и дробная части числа х /I В четвертом такте значение (z + + ВО записывается в регистр 13 и со сдвигом на один разряд вправо поступает на сумматор 18. Одновремен но значение К старших разрядов аргумента х из регистра 10 переписывается в регистр 14 и поступает на адресные входы блока памяти 15, откуда выбирается соответствующая константа А и поступает на второй вход сумматора 18, где формируется значение у) + 0,5(2 (;+ В() с выхода сумматора 18 значение поступает на вход коммутат.ора 19. Если аргумент X, имеет положительный знак, 9098 то в первом разряде регистра 14 хранится О и значение yd) поступает на вход регистра 21 через коммутатор 19 со сдвигом на один разряд вправо, т.е. нормализуется, а на второй вход младшего разряда сумматора 17 через элемент НЕ 16 поступает значение . На первые входы сумматора 17с выхода регистра 12 поступает значение целой части аргумента х . На выходе сумматора 17 формируется значение zy + 1. Если аргумент х имеет отрицательный знак, то значение 1, поступающее с выхода первого разряда регистра 14 на управляющий вход коммутатора 19, разрешает прохождение значения у(Ч с выхода сумматора 18 на вход регистра 21 без сдвига, а на вход младшего разряда сумматора 17 через элемент НЕ 16 поступает О. В этом случае на выходе сумматора 17 значение . В этом же такте в регистры 1 и 2 заносится порядок и мантисса нового аргумента х, в регистры 4 и 5 - значения z| и z 4 для аргумента Xj, а в-регистры 8, 9 и и 10 - значения , + В и значение К старших разрядов соот ветственно. В пятом такте в регистр 20 заносится порядок выходного числа, а в регистр 21 - мантисса. В регистры 1 и 2 заносится новый аргумент Xj-, а в регистры 4, 5, 8, 9, 10, 12, 13 и 14результаты промежуточных вычислений над числами х, Xj и х. Регистр 20 имеет разрядность + 1 чтобы исключить переполнения сумматора 17.

| Устройство для потенцирования | 1976 |

|

SU633017A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для выполнения операции потенциирования с плавающей запятой | 1975 |

|

SU572780A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-15—Публикация

1984-05-17—Подача