Изобретение относится к электросвязи и может быть использовано в телеметрии и при передаче данных.

Известна система передачи и. приема информации с коррекцией ошибок, содержащая на передающей стороне последовательно соединенныесинхронизатор/ генератор эталонного кода, блок сумматоров по модулю два и регистр, а также модулятор сигналов ФРМ, на приемной стороне - демодулятор и объединенные по входу сумматор по модулю два и элемент задержки, выход которого подключен к второму входу сумматора по модулю два, выход которого подключен к первому входу коррелятора, к второму входу которого подключен выход генератора эталонного кода, к второму входу которого подключен выход синхронизатора 1

Однако у известной системы недостаточная помехоустойчивость при модуляции типа ФРМ.

, Целью изобретения является повышение помехоустойчивости.

Для этого в систему передачи и приема информации с коррекцией ошибок, содержащую на передамчей стороне последовательно соединенные синхронизатор, генератор эталонного кода, блок сумматоров по модулю два и регистр, а также модулятор сигналов ФРМ, на приемной стороне - демодулятор и объединенные по вход сумма- . тор по модулю два и элемент задержки, выход которого подключен к второму входу сумматора по модулю два, выход которого подключен к первому

10 входу коррелятора, к второму входу которого подключен выход генератора эталонного кода, к входу которого подключен выход синхронизатора, на передающей стороке введены блок счи15тывания и последовательно соединенные блок кодирования и преобразователь кода, при этом выход регистра подключен к входу модулятора сигналов ФРМ, а выход синхронизатора под20ключен к вторым входам блока кодирования и преобразователя кодов, а также через .блок считывания к управляющему входу регистра, к вторым входам которого, а также к вторым вхо25дам блока сумматора по модулю два подключены выходы преобразователя кода, на приемной стороне введены последовательно соединенные первый и второй корректоры ошибок, при

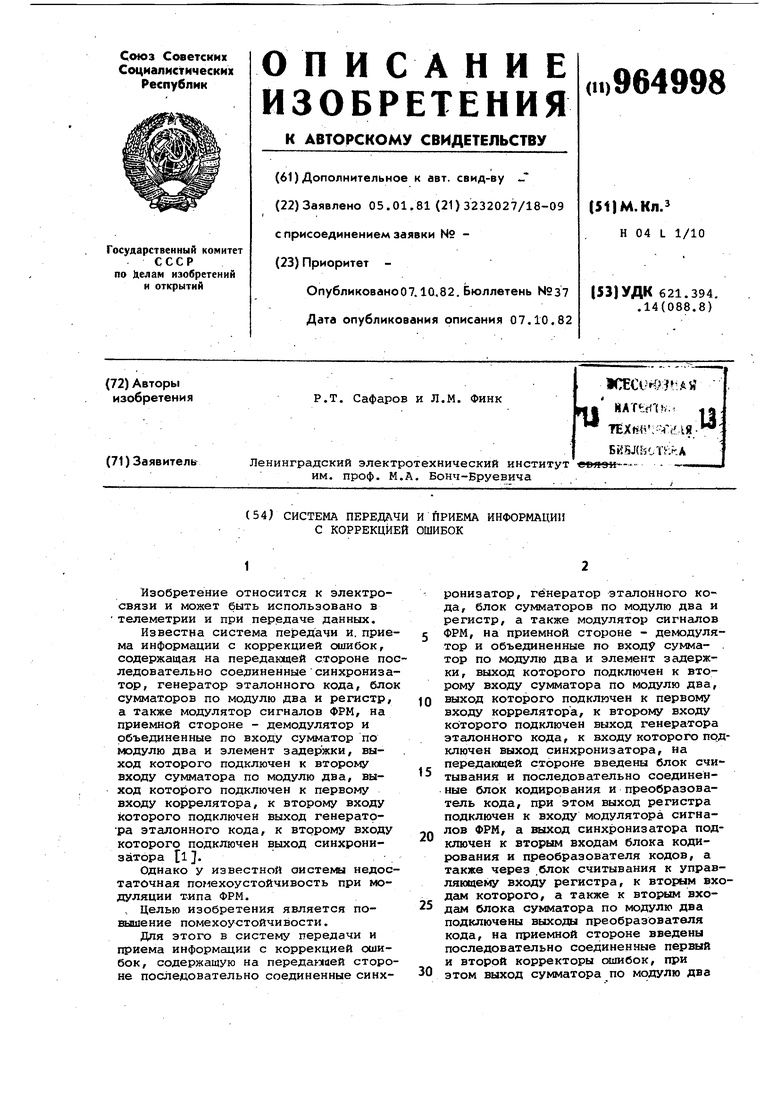

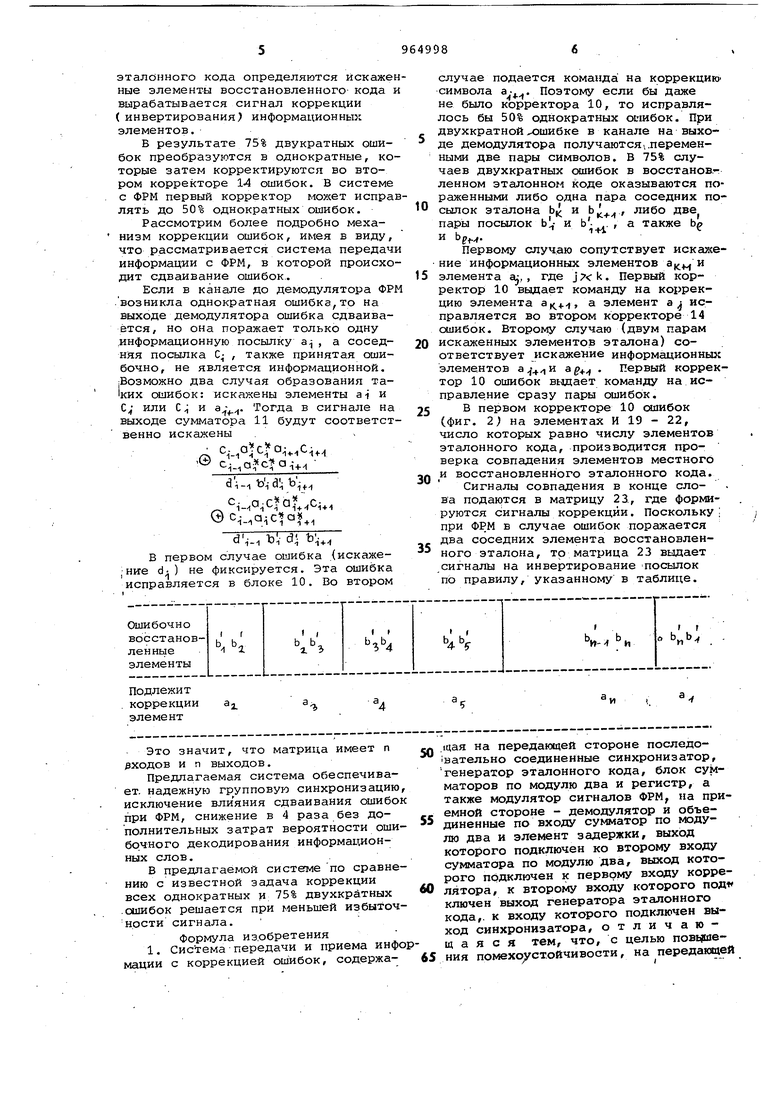

30 этом выход сумматора по модулю два подключен к первому входу первого корректора ошибок, к второму и тре.тьему входам которого подключены соответственно выходы синзсронизатора и генератора эталонного кода, .а выход демодулятора соединен с вто рым входом второго корректора сииибок, первым входом сумматора по модулю два, входом элемен та задержки и первым входом синхронизатора, второй вход которого соединен с вых дом коррелятора, а выход синхрониза тора подключен к третьему входу вто рого корректора ошибок, при этом первый корректор ошибок содержит пе вый регистр, соединенный через блок элементов И с входами матрицы, выхо ды которой являрзтся выходами первог корректора ошибок, а к вторым входа блока элементов И подключены выходы второго регистра, при этом входы пе вого и.второго регистров соответств но являются третьим и первым входами первого корректора ошибок, второ вход которого соединен с третьими входами блока элементов И. На фиг. 1 приведена структурная схема систеьфл передачи и приема информации , состоящей из передающей и приемной частей; на фиг. 2 - схема корректора ошибок. В передающую часть системы входят блок 1 кодирования, преобразова тель кода, регистр 3 на 2п элементов , блок 4 сумматоров по модулю два, генератор 5 эталонного к9Да, синхронизатор б, блок 7 считывания, модулятор ФРМ 8. В состав приемной части системы йЗсодят .демодулятор ФРМ 9, первый ко ректор 10 сшибок, сумматор 11 по мо дулю два, элемент 12 задер кки, корр лятор 13, второй корректор 14 ошибок, генератор 15 эталонного кода, синхронизатор 16. Первый корректор ошибок (фиг. 2 содержит первый регистр 17, второй регистр 18, блок элементов И 19-22 и матрицу 23. Система работает следующим образом. . В блоке 1 кодирования информационное слово, состоящее из К симво.лов преобразуется в п-разрядное слово, например, в соответствии с кодом Хэмминга, исправляющим однократные ошибки. В преобразователе 2 кода двоичная последовательность преобразуется Е другую последовательность, соответствующую передаче по методу ФРМ. Полученные п-значные кодовые комбинации записываются в регистр 3 .и подаются на вход блока сумматоров по модулю два, на вторые п входов которого поступают п-значные эталонные слова кода, обладающего ХОРОШИМИ корреляционными свойствами, вырабатываемые в генераторе 5 эталонного кода. .В блоке 4 сумматоров по модулю два производится поэлементное сугФдарование по mod 2 символов двух п-значных слов, из которых одно является информационным, а. второе - эталонным. Полученные символы вводятся на вторые п элементов регистра 3, причем информационные символы с выхода преобразователя 2 кода записываются на нечетных элемен-. тах, а производные символы с выхода блока 4 сумматоров по модулю два на четных элементах.регистра 3. Преобразователь параллельного кода (2п, k), записанного в регистре 3, в последовательный код производится с помощью блока 7 считывания, управляемого, ,как и блоки 1, 2 и 3, сигналами синхронизатора 6. Последовательность двоичных посылок подается на вход модулятора ФРМ 8, где осуществляется фазовая манипуляция несущих колебаний. На приемной стороне на выходе демодулятора ФРМ 9 получается двоич.ный видеосигнал в -виде последовательности слов по 2п элементов, из которых нечетные элементы являются информационными. Они содержат К исходных информационных элементов и п-К проверочных элементов. Четные элементы (их число также п) образованы поэлементным суммированием по mod 2 символов информационной части символов эталонного кода. Такой сигнал подвергается ряду преобразований. С помощью сумматора 11 и элемента задержки получают двоичную последователь(юсть, в которой на четных позициях слов длиной 2 располагаются элементы восстановленного эталонного кода. Действительно, если информационные символы, а элементы эталонного кода, то элементы сигнала на входе блока 11, располагающиеся на четных позициях. При поэлементном cy lмиpoвaнии по mod 2 принятого и задержанного на один элемент сигнала получаем © ..-nCi.r --- ,c,qH.... t))i, где b. a-®Ci - элемент востановленного эталонного Сигнал с выхода сумматора 11 по модулю два поступает в коррелятор 13, куда подается также эталонный код. На выходе коррелятора 13 выделяется синхросигнал, соответствующий границе слова. В первом корректоре 10 ошибок, куда подаются те ке сигналы, в результате поэлементного сравнения эталонного кода генератора 15 эталонного кода и восстановленного

эталонного кода определяются искаженные элементы восстановленного кода и вырабатывается сигнал коррекции ( инвертирования) информационных элементов.

В результате 75% двукратных ошибок преобразуются в однократные, которые затем корректируются во втором корректоре 14 ошибок. В системе с ФРМ первый корректор мохсет исправлять до 50% однократных ошибок.

Рассмотрим более подробно механизм коррекции ошибок, имея в виду, что рассматривается система передачи информации с ФРМ, в которой происходит сдваивание ошибок.

Если в канале до демодулятора ФРМ .возникла однократная ошибка, то на выходе демодулятора ошибка сдваивается, но она поражает только одну .информационную посылку а, а соседняя посылка С , также принятая ошибочно, не является информационной. Возможно два случая образования таких ошибок: искажены элементы ai и С; или С и Тогда в сигнале на выходе сумматора 11 будут соответственно искажены

. с..а,а..с,, ® ,,4-i d--, ,,

с.-,а,,С, .,,

dv, ъ;- b,,

в первом случае ошибка (искаже;ние d- ) не фиксируется. Эта ошибка

исправляется в блоке 10. Во втором

случае подается команда на коррекцию символа а. Поэтому если бы даже не было корректора 10, то исправлялось бы 50% однократных ошибок. При двухкратной хэшибке в канале на выходе демодулятора полу чаются (.переменными две пары символов. В 75% случаев двухкратных ошибок в восстанов.ленном эталонном йоде оказываются пораженными либо одна пара соседних по0сылок эталона Ь, и Ь, , либо две пары посылок bl,- и Ь- .. , а также be

f k

и bp.

Первому случаю сопутствует искадсение информационных элементов а. и

5 элемента aj, , где . Первый корректор 10 выдает команду на коррекцию элемента а,, а элемент а исправляется во втором корректоре 14 ошибок. Второму случаю (двум парам искаженных элементов эталона) со0ответствует искажение информационных элементов а . Первый корректор 10 ошибок выдает команду на исправле.ние сразу пары ошибок.

В первом корректоре 10 сядибок

5 (фиг. 2 на элементах И 19 - 22, число которых равно числу элементов эталонного кода, производится проварка совпадения элементов местного и восстановленного эталонного кода.

0

Сигналы совпадения в конце слова подаются в матрицу 23., где формируются сигналы коррекции. Поскольку; при ФРМ в случае ошибок поражается два соседних элемента восстановлен5ного эталона, то матрица 23 выдает сигналы на инвертирование посылок по правилу, указанному в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи и приема информации с коррекцией ошибок | 1982 |

|

SU1078653A1 |

| Цифровая система передачи и приема информации с обнаружением ошибок | 1982 |

|

SU1123111A1 |

| Система передачи цифровых сигналов | 1982 |

|

SU1091359A1 |

| Система передачи и приема цифровых сигналов | 1985 |

|

SU1314463A1 |

| Система передачи цифровых сигналов | 1987 |

|

SU1548849A1 |

| Система передачи и приема цифровых сигналов с обнаружением ошибок | 1984 |

|

SU1221759A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Устройство передачи сообщений | 1985 |

|

SU1506555A1 |

| Система для передачи и приема цифровой информации | 1989 |

|

SU1637025A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

Это значит, что матрица имеет п эходов и п выходов. Предлагаемая система обеспечивает, надежную групповую синхронизацию исключение влияния сдваивания ошибок при ФРМ, снижение в 4 раза без дополнительных затрат вероятности ошибочного декодирования информационных слов. В предлагаемой системе по сравнению с известной задача коррекции всех однократных и 75% двухкратных .ошибок решается при меньшей избыточности сигнала. Формула из.обретения 1. Система передачи и приема инфо мации с коррекцией ошибок, содержащая на передающей стороне последо вательно соединенные синхронизатор, генератор эталонного кода, блок сумматоров по модулю два и регистр, а также модулятор сигналов ФРМ, на приемной стороне - демодулятор и объединенные по входу сумматор по модулю два и элемент задержки, выход которого подключен ко второму входу сумматора по модулю два, выход которого подключен к первому входу коррелятора, к второму входу которого под ключен выход генератора эталонного кода,, к входу которого подключен выход синхронизатора, отличающаяся тем, что, с целью повцшения помехоустойчивости, на передающей

стороне введены блок считывания и последовательно соединенные блок код рования и преобразователь кода, при этом выход регистра подключен к входу модулятора сигналов ФРМ, а выход синхронизатора подключен к вторым входам блока кодирования и преобразователя кода, а также через блок считывания к управлякщему входу регистра, к вторым входам которого, а также к втором входам блока cyiuovtaToров по модулю два подключены выход|:1 преобразов-ателя кода, на приемной стороне введены последовательно соединенные первый и второй корректоры ойшбок, при этом выход сумматора по модулю два подключен к первому входу первого корректора ошибок, к второму и третьему входам которого подключены соответственно выходы синхронизатора и генератора эталонкого кода, а выход демодулятора соединен с вторым входом второго корректора ошибок, первым входом сумматора.rto модулю два, входом элемевта

ИХ

Фиг.1

задержки и первым входом синхронизатора, второй вход которого соединен с выходом коррелятора, а выход синхронизатора подключен к третьему входу ВТОРОГО корректора ошибок. 2. Система по п. 1, отличающая о я тем, что первый корректор ошибок содержит первый регистр, iсоединенный через блЬк элементов И с входами матрицы, выходы которой являются выходами первого корректора ошибЪк, а к вторым.входам блока элементов И подключены выходы второго регистра, при этом входы первого и второго регистров.соответственно являются третьим и первым входами. первого KoppeicTopa сяаибок, второй вход которого соединен с третьими входами блока элементов И.

Источники информации, принятые во внимание при экспертизе

i X I I

i8

2S

Фиг.1

Авторы

Даты

1982-10-07—Публикация

1981-01-05—Подача