Изобретение относится к электросвязи и может быть использовано при передаче данных в системах с информационной обратной связью.

Цель изобретения - повышение пропускной способности.

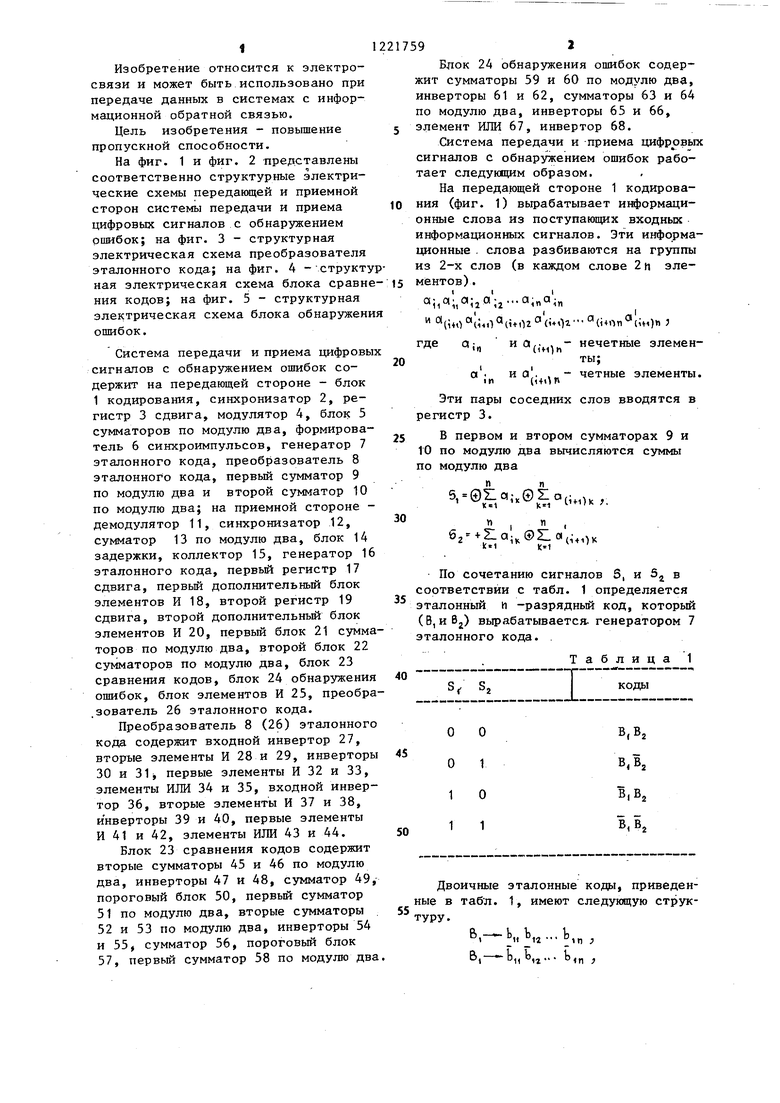

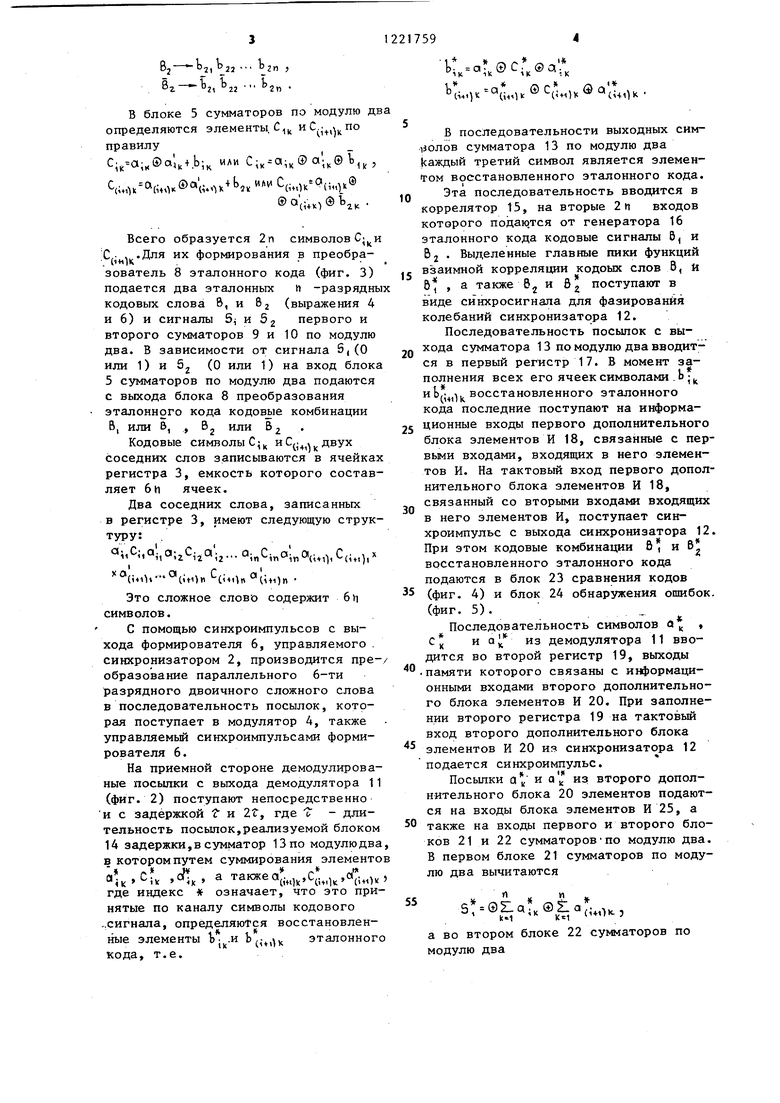

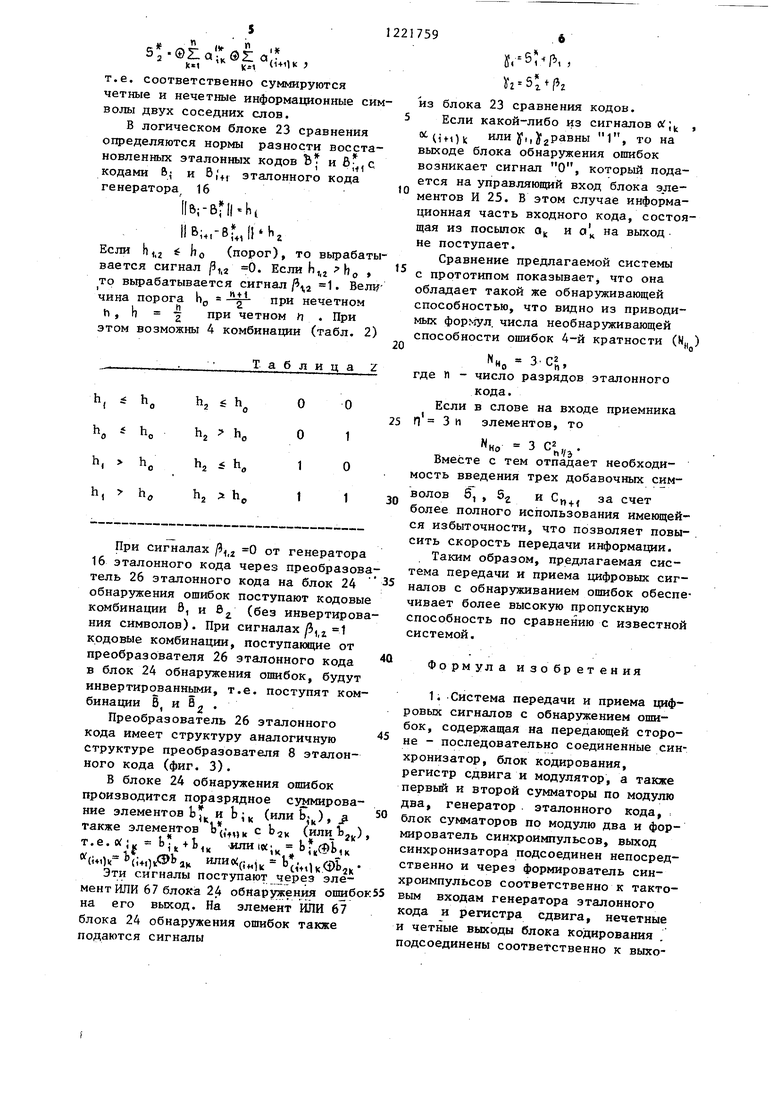

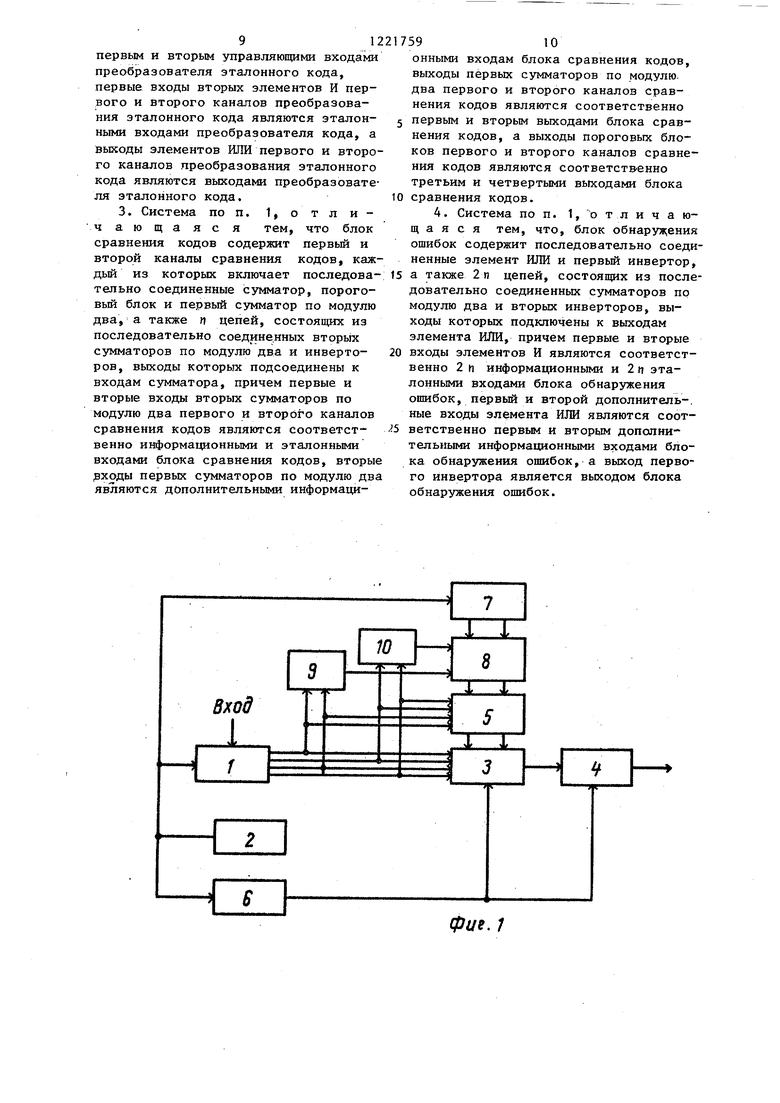

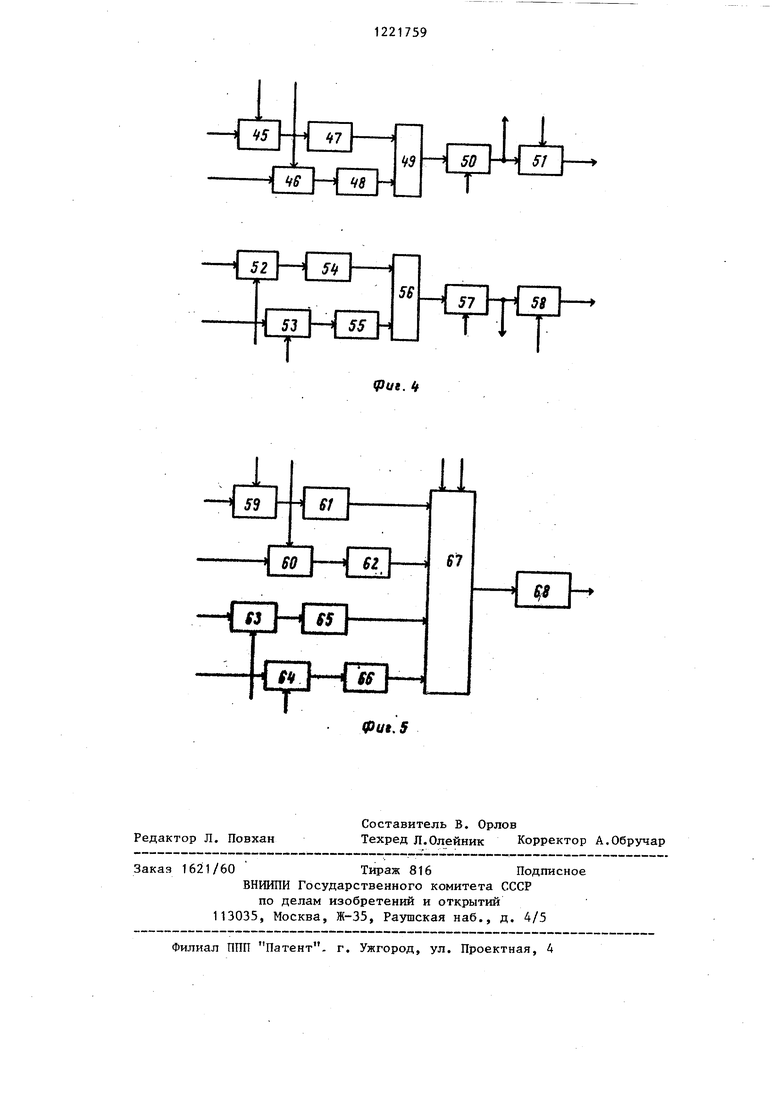

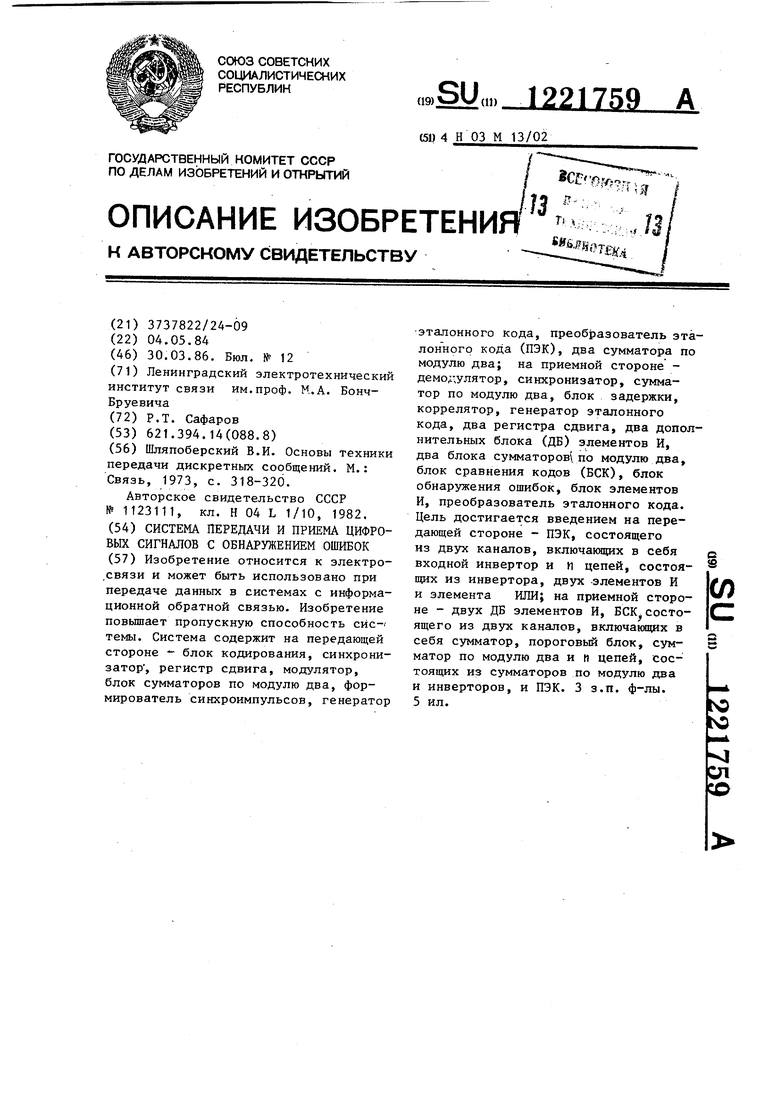

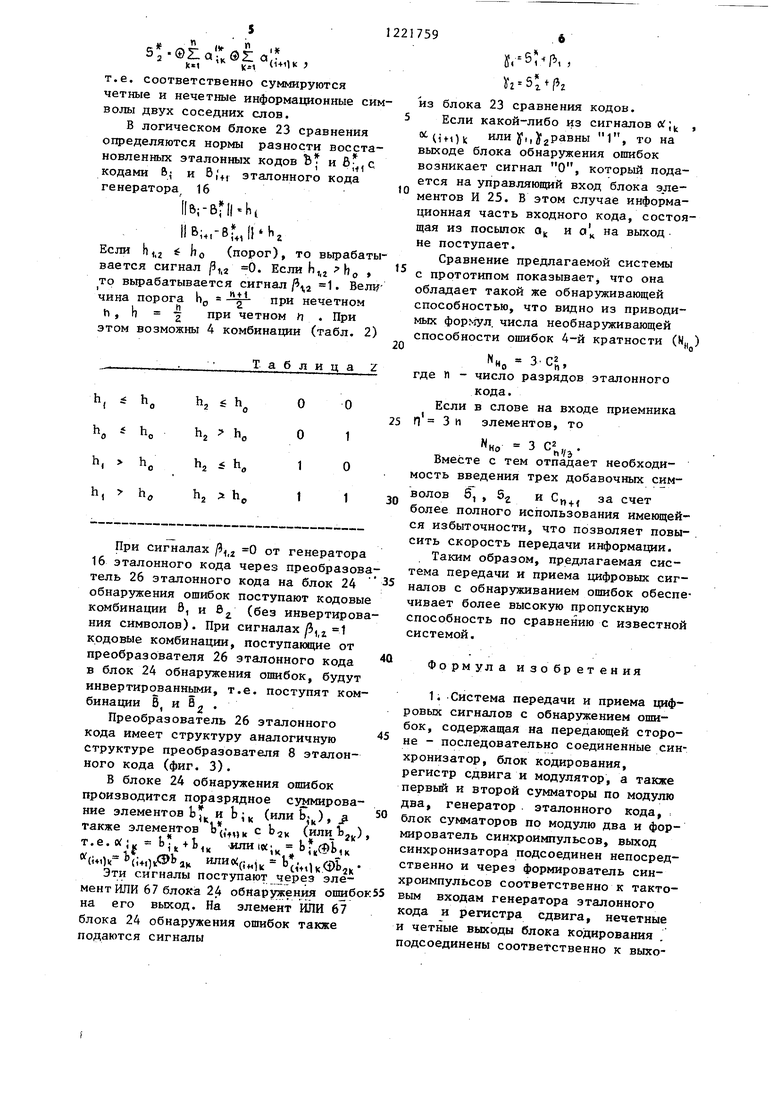

На фиг. 1 и фиг. 2 представлены соответственно структурные электрические схемы передающей и приемной сторон системы передачи и приема цифровых сигналов с обнаружением ошибок; на фиг. 3 - структурная электрическая схема преобразователя эталонного кода; на фиг. 4 - структ

ная электрическая схема блока сравн ния кодов; на фиг. 5 - структурная электрическая схема блока обнаружен ошибок.

Система передачи и приема цифровы сигналов с обнаружением ошибок содержит на передающей стороне - блок 1 кодирования, синхронизатор 2, регистр 3 сдвига, модулятор 4, блок 5 сумматоров по модулю два, формирователь 6 синхроимпульсов, генератор 7 эталонного кода, преобразователь 8 эталонного кода, первый сумматор 9 по модулю два и второй сумматор 10 по модулю два; на приемной стороне - демодулятор 11, синхронизатор 12, сумматор 13 по модулю два, блок 14 задержки, коллектор 15, генератор 16 эталонного кода, первьй регистр 17 сдвига, первьй дополнительный блок элементов И 18, второй регистр 19 сдвига, второй дополнительный блок элементов И 20, первый блок 21 сумматоров по модулю два, второй блок 22 сумматоров по модулю два, блок 23 сравнения кодов, блок 24 обнаружения ошибок, блок элементов И 25, преобра .зователь 26 эталонного кода.

Преобразователь 8 (26) эталонного кода содержит входной инвертор 27, вторые элементы И 28 и 29, инверторы 30 и 31i первые элементы И 32 и 33, элементы ИЛИ 34 и 35, входной инвертор 36, вторые элементы И 37 и 38, и нверторы 39 и 40, первые элементы И 41 и 42, элементы ИЛИ 43 и 44.

Блок 23 сравнения кодов содержит вторые сумматоры 45 и 46 по модулю два, инверторы 47 и 48, сумматор 49, пороговый блок 50, первьй сумматор

51по модулю два, вторые сумматоры

52и 53 по модулю два, инверторы 54 и 55, сумматор 56, пороговьй блок 57, первьй сумматор 58 по модулю два

2217592

БЛОК 24 обнаружения ошибок содержит сумматоры 59 и 60 по модулю два, инверторы 61 и 62, сумматоры 63 и 64 по модулю два, инверторы 65 и 66, 5 элемент ИЛИ 67, инвертор 68.

Система передачи и приема цифровых сигналов с обнаружением ошибок работает следуицим образом.

На передающей стороне 1 кодирова- 10 ния (фиг. 1) вырабатывает информационные слова из поступающих входных информационных сигналов. Эти информационные , слова разбиваются на группы из 2-х слов (в каждом слове 2 и элеентов),

aii°i;,« ;iO;2- a,na

ментов),

и сх где

(uO° n 0(itin (i+Oi

, а

() 3

«in

и а

(i«-l)h

и а.

нечетные элементы;четные элементы.

in (иЛп

Эти пары соседних слов вводятся в регистр 3.

В первом и втором сумматорах 9 и 10 по модулю два вычисляются суммы по модулю два п

5, ®

а;

И

;.

30

)

По сочетанию сигналов 5, и 5 в соответствии с табл. 1 определяется эталонный и -разрядньй код, который ( В, и Bj) вырабатывается, генератором 7 эталонного кода. .

40

45

50

55

Двоичные эталонные коды, приведенные в таб л. 1, имеют следующую структуру.

В,-ь,.ъ„...ь,„.

Вг

Ьп ь,г,

Чп i

Ьгп ,

-к. к, .,.L

-21 22

2n

В блоке 5 сумматоров по модулю дв определяются элементы. С иС,.,по правилу

С;г01;и®а к+Ь; ПАИ С;,-а;,®а ;,,,

(;.лга(.,,,®а;.„,+ Ь,, или C(,,,, a(i,,,®

®a (

Всего образуется 2п символов

С,- ..Для их формирования в преобра- , .

зователь 8 эталонного кода (фиг. 3) подается два эталонных и -разрядны кодовых слова В, и Bj (выражения 4 и 6) и сигналы Si и Sj первого и второго сумматоров 9 и 10 по модулю два. В зависимости от сигнала S,(0 или 1) и 5 (О или 1) на вход блока 5 сумматоров по модулю два подаются с выхода блока 8 преобразования эталонного кода кодовою комбинации В, или В, , Bj или 62

Кодовые символы иС. двух соседних слов записываются в ячейках регистра 3, емкость которого составляет 6н ячеек.

Два соседних слова, записанных в регистре 3, имеют следующую структуру: .

«д1С;,а .,а;,С..а ;.,.а;„С „а;„0((;,фС(„5,х

° (i40.- ° ( ()n

Это сложное слово содержит 6ц символов.

С помощью синхроимпульсов с выхода формирователя 6, управляемого . синхронизатором 2, производится пре-/ образование параллельного 6-ти разрядного двоичного сложного слова в последовательность посылок, которая поступает в модулятор 4, также управляемьй синхроимпульсами формирователя 6.

На приемной стороне демодулирова- ные посьшки с выхода демодулятора 11 (фиг. 2) поступают непосредственно и с задержкой t и 2t, где J - длительность посьшок,реализуемой блоком 14 задержки, в сумматор 13 по модулю два в котором путем суммирования элементов

а.О. где индекс # означает, что это принятые по каналу символы кодового ..сигнала, определяются восстановленные элементы Ь| .и , эталонного кода, т.е.

1 . , .- 1

а.,,

4..(t,l.®(UOx® (U,lK

0

5

0

5

0

5

0

в последовательности выходных сим- 13олов сумматора 13 по модулю два Каждый третий символ является элементом восстановленного эталонного кода.

I

Эта последовательность вводится в коррелятор 15, на вторые 2п входов которого подаются от генератора 16 эталонного кода кодовые сигналы б, и В 2 . Выделенные главные пики функций в:заимной корреляции кодоых слов 8, и 5 , а также 62 и Sj поступают в виде синхросигнала для фазирования колебаний синхронизатора 12.

Последовательность посылок с выхода сумматора 13 по модулю два вводится в первый регистр 17. В момент заполнения всех его ячеек символами

ь

Ik

KuOk восстановленного эталонного кода последние поступают на информационные входы первого дополнительного блока элементов И 18, связанные с первыми входами, входящих в него элементов И. На тактовый вход первого дополнительного блока элементов И 18, связанный со вторыми входами входящих в него элементов И, поступает синхроимпульс с выхода синхронизатора 12. При этом кодовые комбинации В и В восстановленного эталонного кода подаются в блок 23 сравнения кодов (фиг. 4) и блок 24 обнаружения ошибок, (фиг. 5).

Последовательность символов а - к и ° к демодулятора 11 вводится во второй регистр 19, выходы памяти которого связаны с ин|)ормаци- онными входами второго дополнительного блока элементов И 20. При заполнении второго регистра 19 на тактовый вход второго дополнительного блока элементов И 20 из синхронизатора 12 подается синхроимпульс.

Посылки и а из второго дополнительного блока 20 элементов подаются на входы блока элементов И 25, а также на входы первого и второго блоков 21 и 22 сумматоровпо модулю два. В первом блоке 21 сумматоров по модулю два вычитаются

п

и

а во втором блоке 22 сумматоров по модулю два

Д Hf .. I У Zl a,; КЧK-1

(i4ilK }

т.е. Соответственно суммируются четные и нечетные информационные символы двух соседних слов.

В логическом блоке 23 сравнения определяются нормы разности восстановленных эталонных кодов В и 6;, с кодами В, и В,%, эталонного кода генератора 16

llBi-Bflhb(

В;..-в

1-И

-ь.

Если h(.2 ho (порог), то вьфабаты- вается сигнал /З,, 0. Если h,,j h, , то вьфабатывается сигнал /.j 1. Besnf о Р нечетном П . При

чина порога

h , h I при четном этом возможны 4 комбинации (табл. 2)

Та б л и ц а

При сигналах /,2 0 от генератора 16 эталонного кода через преобразователь 26 эталонного кода на блок 24 обнаружения ошибок поступают кодовые комбинации 0, и В. (без инвертирования символов) . При сигналах , j, 1 кодовые комбинации, поступающие от преобразователя 26 эталонного кода в блок 24 обнаружения ошибок, будут инвертированньми, т.е. поступят комбинации 6, и §2 .

Преобразователь 26 эталонного кода имеет структуру аналогичную структуре преобразователя 8 эталонного кода (фиг. 3).

В блоке 24 обнаружения ошибок производится поразрядное сз ммирова- ние элементов Ь и (или Ь-), также элементов Ь,уц с (), т.е.л; Ь + Ь, :илИ1«; bf,(|)b,K

(U,)v ((«JK Ь.,,1 к.,, Эти сигналы поступают через элемент ИЛИ 67 блока 24 обнаружения опшбок на его выход. На элемент ИЛИ 67 блока 24 обнаружения ошибок также подаются сигналы

10

20

25

759.6

Sr51

К2 ,

из блока 23 сравнения кодов.

Если какой-либо из сигналов , , ot,-,),j или у,, Jf 2 равны 1, то на выходе блока обнаружения ошибок возникает сигнал О, который подается на управляющий вход блока элементов И 25. В этом случае информационная часть входного кода, состоящая из посылок а| и а на выход не поступает.

Сравнение предлагаемой системы с прототипом показывает, что она обладает такой же обнаруживающей способностью, что видно из приводимых формул, числа необнаруживающей способности ошибок 4-й кратности (N)

N„0 3., где П - число разрядов эталонного

кода.

Если в слове на входе приемника элементов, то

П 3 h

NU

3 Cl

Но - - vэ

Вместе с тем отпадает необходимость введения трех добавочных сим

п +

за счет

волов б, , 5 и С более полного использования имеющейся избыточности, что позволяет повысить скорость передачи информации.

Таким образом, предлагаемая система передачи и приема цифровых сигналов с обнаруживанием ошибок обеспечивает более высокую пропускную способность по сравнению с известной системой.

Формула изобретения

1. Система передачи и приема цифровых сигналов с обнаружением ошибок, содержащая на передающей стороне - последовательно соединенные синхронизатор, блок кодирования, регистр сдвига и модулятор, а также первый и второй сумматоры по модулю два, генератор эталонного кода, : Олок сумматоров по модулю два и формирователь синхроимпульсов, выход синхронизатора подсоединен непосредственно и через формирователь синхроимпульсов соответственно к такто- вьш входам генератора эталонного кода и регистра сдвига, нечетные и четные выходы блока кодирования подсоединены соответственно к выхо7

дам первого и второго сумматоров по модулю два, дополнительные информационные входы регистра сдвига подключены к соответствующим выходам блока сумматоров по модулю два, входы которого подключены к соответствующим выходам блока кодирования, на приемной стороне - последовательно соединенные демодулятор, сумматор по модулю два, коррелятор, синхрони- затор и генератор эталонного кода, последовательно соединенные блок обнаружения ошибок и блок элементов И, а также первый и второй регистры сдвига, первый и второй блоки сумма- торов по модулю два и блок задержки, выход и вход которого подключены соответственно к второму входу сумматора по модулю два и выходу демодулятора, опорный вход демодулятора под- ключен к выходу синхронизатора, а входы первого и второго блоков сумматоров по модулю два подключены к соответствующим входам блока, элементов И, причем информационный вход блока кодирования на передающей стороне и вькоды блока элементов И на приемной стороне являются соответственно информационными входом и выходом системы, а выход модулятора и вход демодулятора являются соответственно канальньми выходом и входом системы, отличающаяся тем, что, с целью повышения пропускной способности, введены на передаю- щей стороне - преобразователь эталон iHoro кода, на приемной стороне - первый и второй дополнительные блоки элементов-И, блок сравнения кодов и преобразователь эталонного кода, при этом на передающей стороне выходы первого и второго сумматоров по модулю два подсоединены соответственно к первому и второму управляющим входам преобразователя эталонного кода, 2 п эталонных входов которого подключены к соответствующим выходам генератора эталонного кода, 2п выходов преобразователя эталонного кода подсоединены к соответствующим дополнительным входам блока сумматоров по модулю два, опорный вход моду пятора подключен к выходу блока формирования синхроимпульсов, на приемной стороне выходы сумматора по модулю два и демодулятора подсоединены соответственно к входам первого и второго регистров сдвига, 2 п вы

8

ходов первого регистра сдвига через первьй дополнительный блок элементов И подсоединены к соответствующим 2и информационным входам блока сравнения кодов и к 2 п информационным входам блока обнаружения ошибок, входы первого блока сумматоров по модулю два подключены к нечетным выходам второго дополнительного блока элементов И, четные выходы которого подсоединены к входам второго блока сумматоров по модулю два, выходы первого и второго блоков сумматоров по модулю два подсоединены соответственно к первому и второму дополнительным информационным входам блока сравнения кодов, первый и второй выходы которого подсоединены соответственно к первому и второму дополнительным информационным входам блока обнаружения ошибок, третий и четвертый выходы блока сравнения кодов подсоединены соответственно к первому и второму управляющим входам преобразователя эталонного кода, 2 Ц выходов которого подсоединены к соответствующим 2 и эталонным входам блока обнаружения ошибок, 2п выходов генератора эталонного кода подсодинены к соответствукнцим 2 п эталонным входам коррелятора и 2 п эталонным входам преобразователя эталонног кода, дополнительный выход синхронизатора подсоединен к тактовым входам блока элементов И, первого и второго дополнительных блоков элементов И,а дополнительный выход блока задержки подсоединен к дополнительному входу сумматора по модулю два.

2. Система по п. 1, отличающая с я тем, что преобразователь эталонного кода содержит первый и второй каналы преобразования эталонного кода, каждый из которых включает входной инвертор и п цепей, состоящих из последовательно соеди- неньк инвертора, первого элемента И и элемента ИЛИ, а также второго элемента И, вход и выход которого подключены к входу инвертора и второму входу элемента ИЛИ, вход входного инвертора подключен к вторым входам первых инверторов и п цепей, выход входного инвертора подсоединен к вторым входам вторых элементов И И цепей, причем входы входных инверторов первого и второго каналов преобразования эталонного кода являются

первым и вторым управляющими входами преобразователя эталонного кода, первые входы вторых элементов И первого и второго каналов преобразования эталонного кода являются эталонными входами преобразователя кода, а выходы элементов ШШ первого и второго каналов преобразования эталонного кода являются выходами преобразователя эталонного кода,

3. Система по п. 1, о т л и - ч аю ща яс я тем, что блок сравнения кодов содержит первый и второй каналы сравнения кодов, каж- дьй из которых включает последовательно соединенные сумматор, пороговый блок и первый сумматор по модулю два, а также ч цепей, состоящих из последовательно соедине1нных вторьЬс сумматоров по модулю два и инверторов, выходы которых подсоединены к входам сумматора, причем первые и вторые входы вторых сумматоров по модулю два первого и второго каналов сравнения кодов являются соответственно информационными и эталонными входами блока сравнения кодов, вторые Эходы первых сумматоров по модулю два являются дополнительными информационными входам блока сравнения кодов, выходы первых сумматоров по модулю, два первого и второго каналов сравнения кодов являются соответственно первым и вторым выходами блока сравнения кодов, а выходы пороговых блоков первого и второго каналов сравнения кодов являются соответств енно третьим и четвертыми выходами блока

сравнения кодов.

4. Система по п. 1, о т л и ч а ю- щ а я с я тем, что, блок обнаружения ошибок содержит последовательно соединенные элемент ИЛИ и первый инвертор,

а также 2 п цепей, состоящих из последовательно соединенных сумматоров по модулю два и вторых инверторов, выходы которых подключены к выходам элемента ИЛИ, причем первые и вторые

входы элементов И являются соответственно 2 h информационными и 2л эталонными входами блока обнаружения ошибок, первый и второй дополнитель-. ные входы элемента ИЛИ являются соответственно первым и вторым дополнительными информационными входами блока обнаружения ошибок, а выход первого инвертора является выходом блока обнаружения ошибок.

ФШ. 1

фиг. 2

ijL

JH:

28

-4

3S

IJL

Выход

JJ |-H

J5

{ J5 jH jr}W

i JLjL-.

4

-f

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи цифровых сигналов | 1987 |

|

SU1548849A1 |

| Устройство передачи информации с защитой от ошибок | 1984 |

|

SU1188893A1 |

| Цифровая система передачи и приема информации с обнаружением ошибок | 1982 |

|

SU1123111A1 |

| Система передачи и приема цифровых сигналов | 1985 |

|

SU1314463A1 |

| Система передачи и приема информации с коррекцией ошибок | 1982 |

|

SU1078653A1 |

| Система передачи и приема информации с коррекцией ошибок | 1981 |

|

SU964998A1 |

| Устройство передачи сообщений | 1985 |

|

SU1506555A1 |

| Система передачи цифровых сигналов | 1982 |

|

SU1091359A1 |

| Система для передачи и приема цифровой информации | 1989 |

|

SU1637025A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

Изобретение относится к электро- .связи и может быть использовано при передаче данных в системах с информационной обратной связью. Изобретение повьшает пропускную способность сйс- темы. Система содержит на передающей стороне - блок кодирования, синхронизатор , регистр сдвига, модулятор, блок сумматоров по модулю два, формирователь синхроимпульсов, генератор эталонного кода, преобразователь эта- лон ногр кода (ПЭК), два сумматора по модулю два; на приемной стороне - демодулятор, синхронизатор, сумматор по модулю два, блок задержки, коррелятор, генератор эталонного кода, два регистра сдвига, два дополнительных блока (ДБ) элементов И, два блока сумматоров по модулю два, блок сравнения кодов (БСК), блок обнаружения ошибок, блок элементов И, преобразователь эталонного кода. Цель достигается введением на передающей стороне - ПЭК, состоящего из двух каналов, включающих в себя входной инвертор и И цепей, состоящих из инвертора, двух -элементов И и элемента ИЛИ; на приемной стороне - двух ДБ элементов И, БСК состоящего из двух каналов, включаннцих в себя сумматор, пороговьй блок, сумматор по модулю два и ц цепей, состоящих из сумматоров по модулю два и инверторов, и ПЭК. 3 з.п. ф-лы. 5 ил. г (Л

-l ijijl

53

5S

ri Г

iptje. ff

SO

M

Редактор Л. Повхан

Заказ 1621/60Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент - г. Ужгород, ул. Проектная, 4

Фт, 5

Составитель В. Орлов

Техред Л.Олейник Корректор А.Обручар

| Шляпоберский В.И | |||

| Основы техники передачи дискретных сообщений | |||

| М.: Связь, 1973, с | |||

| Способ изготовления фасонных резцов для зуборезных фрез | 1921 |

|

SU318A1 |

| Цифровая система передачи и приема информации с обнаружением ошибок | 1982 |

|

SU1123111A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-03-30—Публикация

1984-05-04—Подача