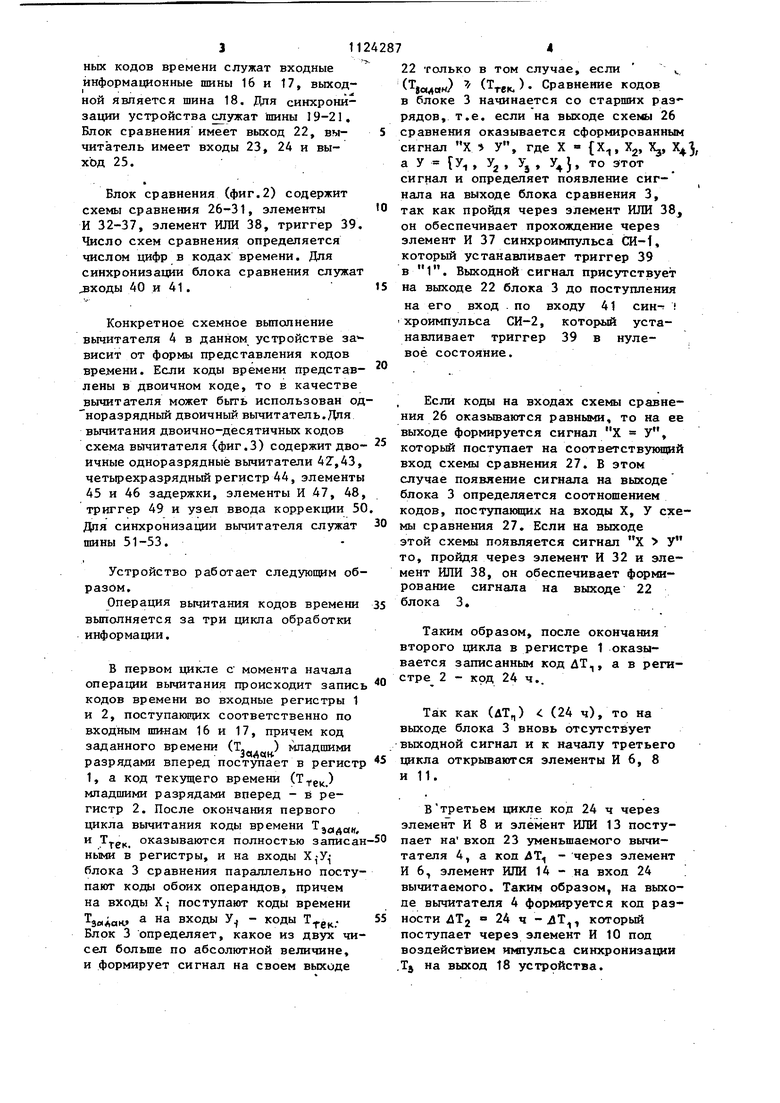

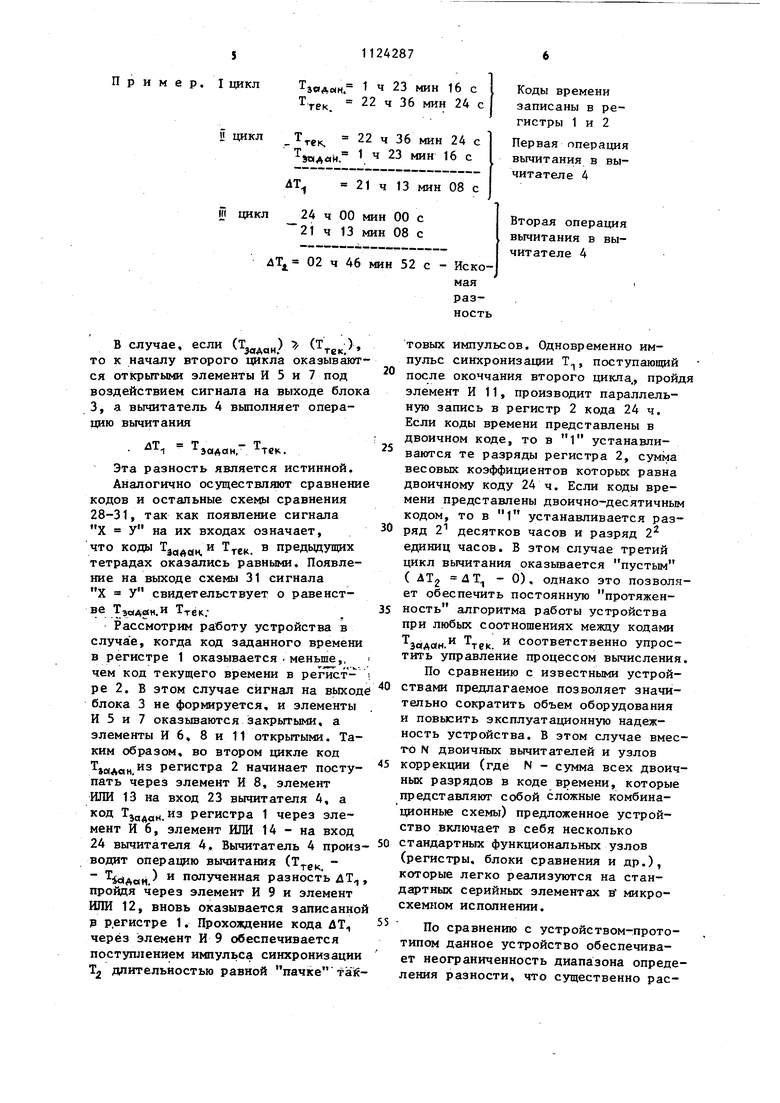

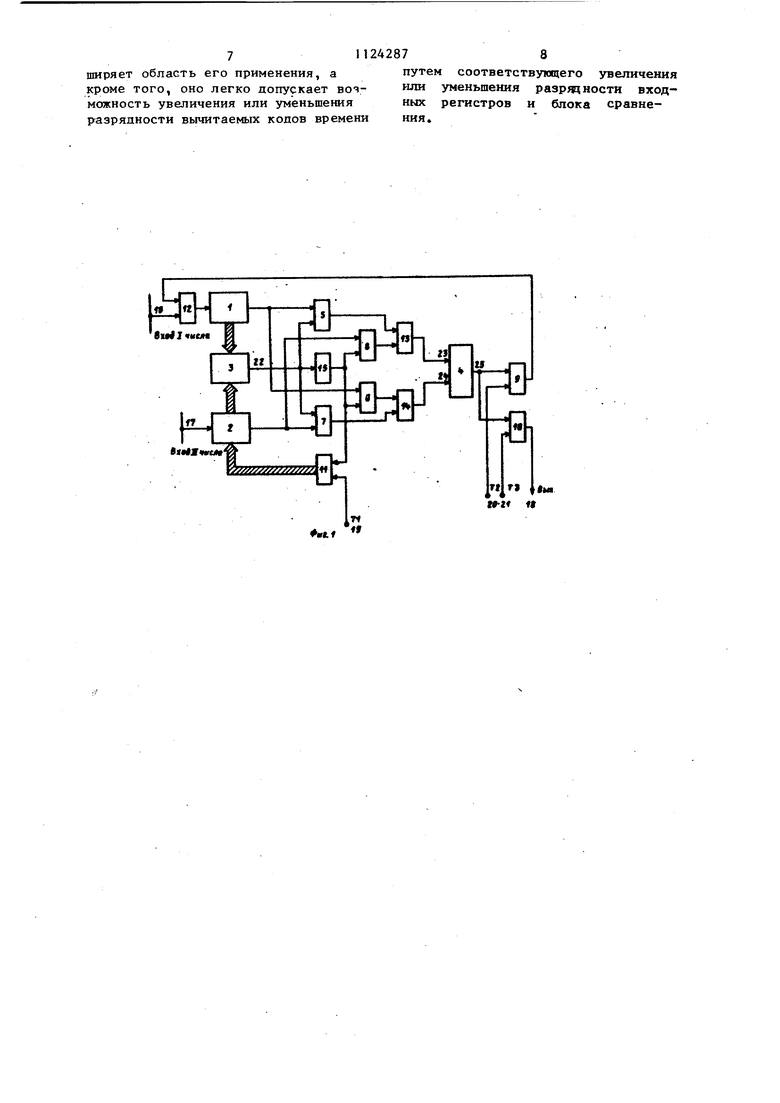

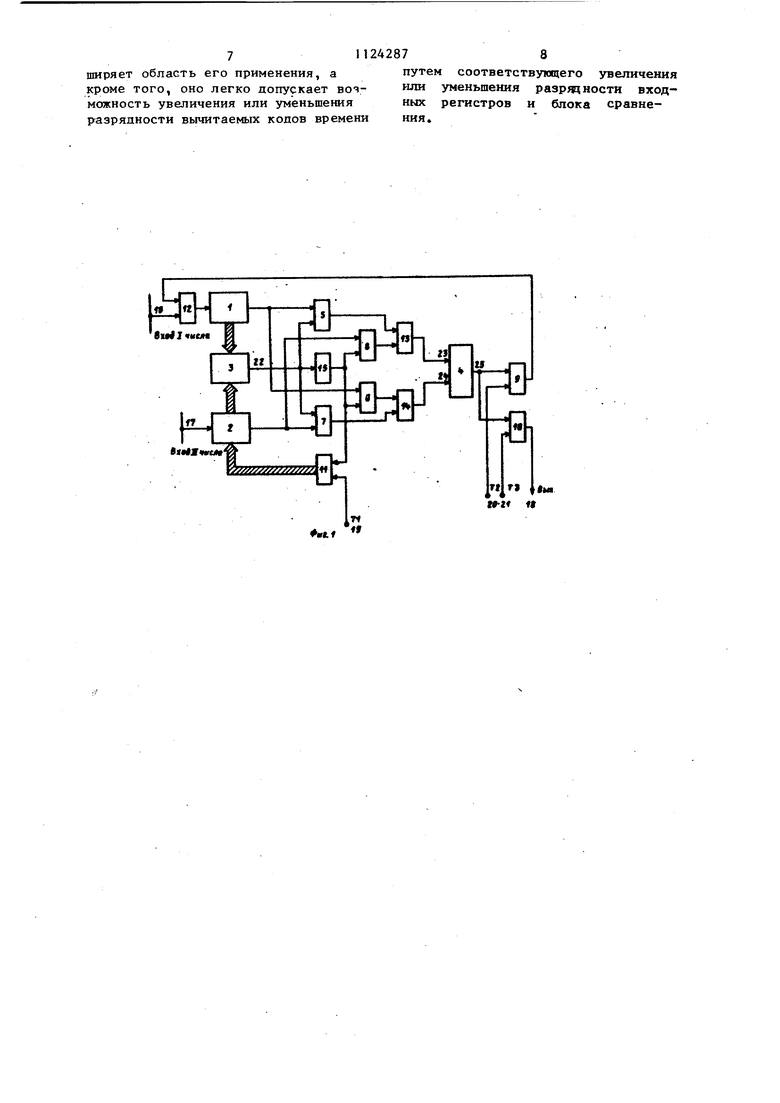

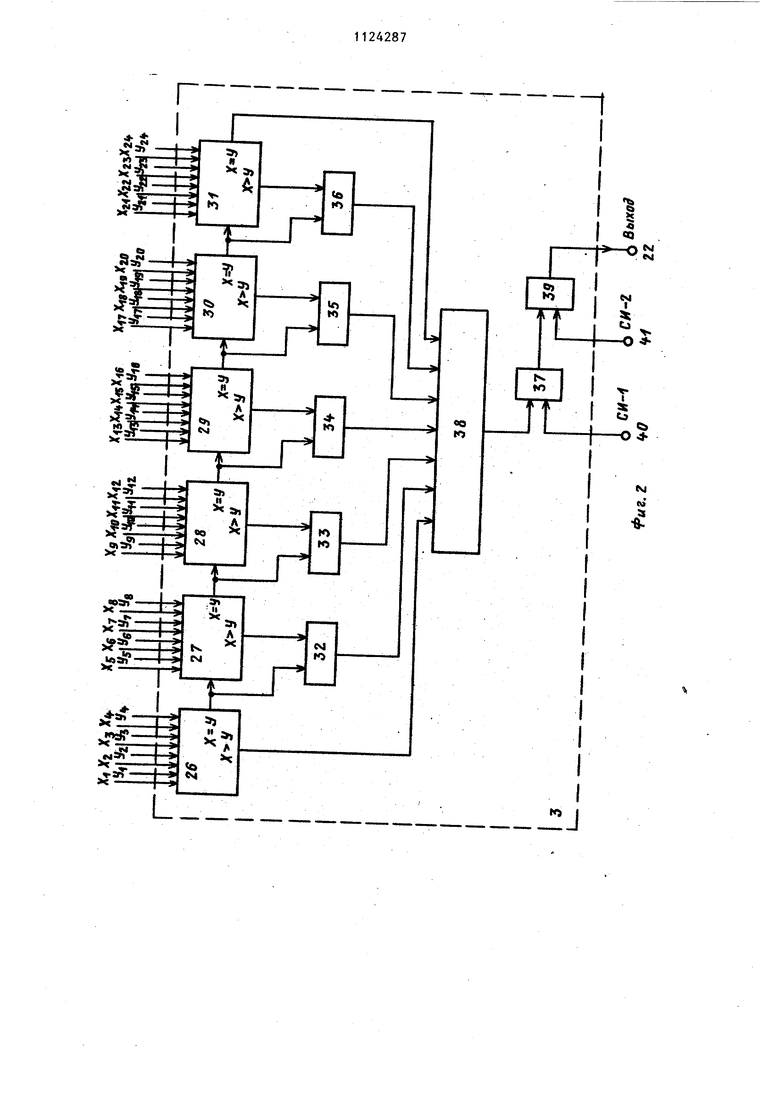

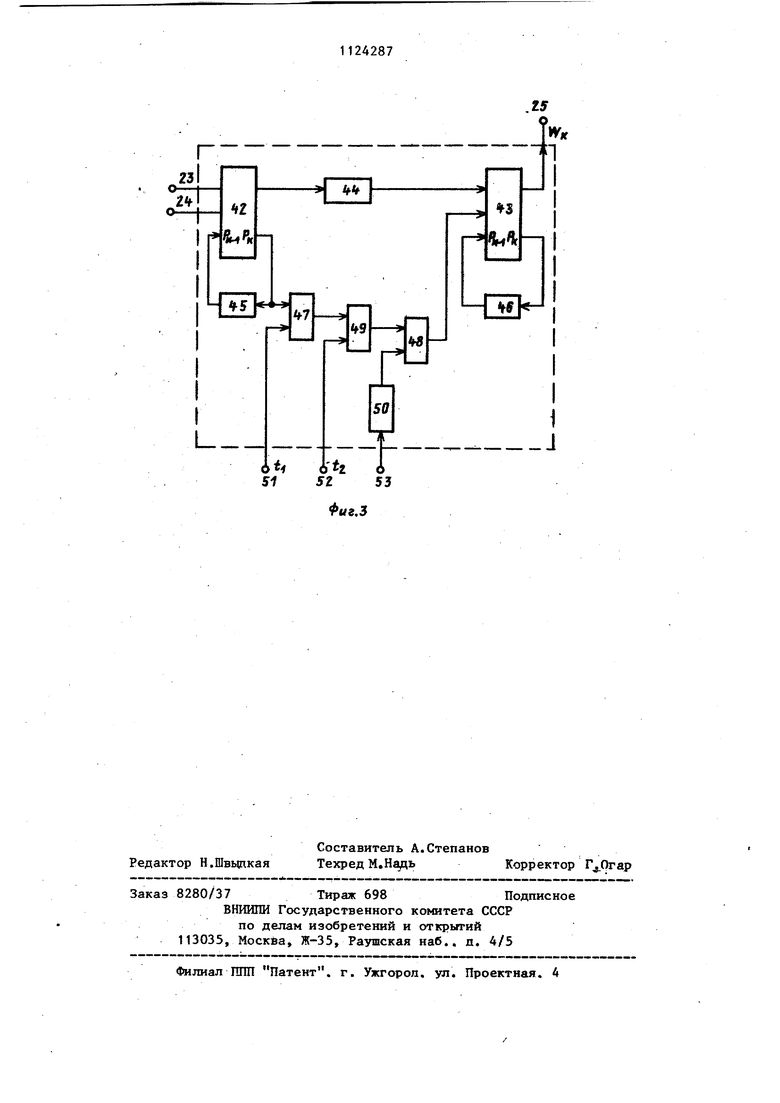

Изобретение относится к вычислиI тельной технике и может быть использовано в устройствах сравнения задан ного и текущего времени с отображени ем разностного времени. Известно устройство для вычитания двоично-десятичных кодов времени, содержащее блоки вычитания кодов десятых долей секунд, единиц секунд, десяткор секунд, единиц минут, десят ков минут, единиц часов и десятков часов Cl . Это устройство обеспечивает вычитание кодов времени с переходом кода разности через значение, 24 ч путем тройной коррекции кода разности в разрядах единиц часов и двойной коррекции кода разности в разрядах десятков часов. Недостатками известного устройства являются его сложности и большой объем используемого оборудования. Известно также устройство для вы- читания кодов времени, содержащее первый и второй регистры, блок сравнения, вьгчитатель и элемент И, приче выходы разрядов входных регистров соединены с соответствующими разряда ми первого и второго входов блока сравнения, а также с разрядами перво го и второго входов вычитателя, выхо блока сравнения соединен с первым входом элемента И, второй вход которого соединен с выходом разности вычитателя, выход заема которого соеди нен с управляющим входом блока сравнения, выход элемента И является информационным выходом устройства С2 . Недостатком известного устройства является ограниченность области его применения, вызванная узким диапазоном определения разностного времени. Этот диапазон ограничен одним часом. I Целью изобретения является расширение области применения за счет увеличения диапазона определения разностного времени. Поставленная цель достигается тем, что устройство для вычитания кодов времени, содержащее первый и второй входные регистры, блок сравнения, вьтчитатель и перпый элемент И йрнчем выходы разрядов входных регистров соединены с соответствующими раз)ядами первого и второго входов блока сравнения, выход которого .соединен с первым входом первого эле мента И, содержит также второй, третий, четвертый, пятый, шестой и седьмой элементы И, первьй, второй и третий элементы ИЛИ и элемент НЕ, первый вход первого элемента ИЛИ со.единен с первой входной информационной шиной устройства, а выход соединен с входом первого входного регистра, первый вход второго входного регистра соединен с второй входной информационной шиной устройства, выход старшего разряда первого входного регистра подключен к второму входу первого и к первому входу второго элементов И, выход блока сравнения соединен с входом элемента НЕ и с первым входом третьего элемента И, второй вход которого соединен с первым входом четвертого элемента И и с выходом старшего разряда второго входного регистра, выход элемента НЕ соединен с вторыми входами второго и четвертого элементов И и с первым входом пятого элемента И, выход которого подключен к второму входу -второго входного регистра, выходы первого и четвертого элементов И соединены с соответствующими входами второго элемента ИЛИ, выходы второго и третьего элементов И подключены к соответствующим входам третьего элемента ИЛИ, выходы второго и третьего элементов ИЛИ соединены с соответствующими входами вычитателя, выход которого подключен к первым входам шестого и седьмого элементов И, выход шестого элемента И соединен с вторым входом первого элемента ИЛИ, выход седьмого элемента И соединен с выходной шиной устройства, вторые входы пятого, шестого и седьмого элементов И соединены соответственно с первой, второй и третьей шинами синхронизации устройства. На фиг. 1 представлена структурная схема устройства для вычитания кодов времени; на фиг. 2 - структурная схема блока сравнения; на фиг. 3 - функциональная схема вычитателя. Устройство для вычитания кодов времени содержит входные регистры 1 и 2, Ълок 3 сравнения, вычитатель 4, элементы И 5-11, элементы Ш1И 1214 и элемент НЕ 15. Для приема входных кодов времени служат входные информационные шины 16 и 17, выходной является шина 18. Для синхронизации устройства служат шины 19-21, Блок сравнения имеет выход 22, вычитатель имеет входы 23, 24 и выход 25. Блок сравнения (фиг.2) содержит схемы сравнения 26-31, элементы И 32-37, элемент ИЖ 38, триггер 39 Число схем сравнения определяется числом цифр в кодах времени. Для синхронизации блока сравнения служат ходы 40 и 41. Конкретное схемное вьтолнение вычитателя 4 в данном устройстве за висит от формы представления кодов времени. Если коды времени представлены в двоичном коде, то в качестве вычитателя может быть использован од норазрядный двоичный вычитатель.Для вычитания двоично-десятичных кодов схема вычитателя {фиг.3) содержит дво ичные одноразрядные вычитатели 47,43 четырехразрядный регистр 44, элементы 45 и 46 задержки, элементы И 47, 48 триггер 49 и узел ввода коррекции 5 Для синхронизации вычитателя служат шины 51-53. Устройство работает следую цим об разом. Операция вычитания кодов времени выполняется за три цикла обработки информации. В первом цикле с момента начала операции вычитания происходит запис кодов времени во входные регистры 1 и 2, поступакнцих соответственно по входным ши-нам 16 и 17, причем код заданного времени (Т,„, ) младшими заАвн разрядами вперед поступает в регист 1, а код текущего времени (Туе) младшими разрядами вперед - в регистр 2. После окончания первого цикла вычитания коды времени Т. задан, оказываются полностью записа ными в регистры, и на входы Х,-У блока 3 сравнения параллельно посту пают коды обоих операндов, причем на входы X,- поступают коды времени ТЗ«АС,К.. а на входы У - коды . Блок 3 определяет, какое из двух чи сел больше по абсолютной величине, и формирует сигнал на своем выходе 22 только в том случае, если () . Сравнение кодов в блоке 3 начинается со старших раэ рядов, т.е. если на выходе схемы 26 сравнения оказывается сформированным сигнал X У, где X « {Х, Х2, Х, , У {У, . У. то этот 2 3 4 J сигнал и определяет появление сигнала на выходе блока сравнения 3, так как пройдя через элемент ИЛИ 38, он обеспечивает прохождение через элемент И 37 синхроимпульса СИ-t, который устанавливает триггер 39 в 1. Выходной сигнал присутствует на выходе 22 блока 3 до поступления на его вход . по входу 41 син-г хроимпульса СИ-2, который устанавливает триггер 39 в нулевое состояние. Если коды на входах схемы сравнения 26 оказываются равньо4и, то на ее выходе формируется сигнал X У который поступает на соответствующий вход схемы сравнения 27. В этом случае появление сигнала на выходе блока 3 определяется соотношением кодов, поступакяцих на входы X, У схемы сравнения 27. Если на выходе этой схемы появляется сигнал X У то, пройдя через элемент И 32 и элемент ИЛИ 38, он обеспечивает формирование сигнала на выходе 22 блока 3, Таким образом, после окончания второго цикла в регистре 1 оказывается записанным кодДТ, а в регистре 2 - код 24 ч.. Так как (ДТ) (24 ч), то на выходе блока 3 вновь отсутствует выходной сигнал и к началу третьего цикла открываются элементы И 6, 8 и 11. Втретьем цикле код 24 ч через элемент И 8 и элемент ИЛИ 13 поступает на вход 23 уменьшаемого вычи- тателя 4, а код ЛТ - через элемент И 6, элемент ИЛИ 14 - на вход 24 вычитаемого. Таким образом, на выходе вычитателя 4 формируется код разности ЛТ2 24 ч -ЛТ, который поступает через элемент И 10 под воздействием И1 шульса синхронизации .Т на выход 18 устройства. Пример, I цикл ТЗЯАММ. Т.е ji цикл .

24 ч 00 мин 00 с

ш цикл 21 ч 13 мин 08 с

ЛТ, 02 ч 46 мин 52 с - ИскоВ случае, если () / (), то к началу второго цикла оказываются открьггыми элементы И 5 и 7 под воздействием сигнала на выходе блока 3, а вычитатель 4 выполняет операцию вычитания

. ЛТ -

Эта разность является истинной.

Аналогично осуществляют сравнение кодов и остальные схемы сравнения 28-31, так как появление сигнала X У на их входах означает, что коды Тзадан.и . предыдущих тетрадах оказались равными. Появление на выходе схемы 31 сигнала X У свидетельствует о равенстве TJOIAOIH. и Ттёк;

Рассмотрим работу устройства в случае, когда код заданного времени в регистре 1 оказывается .меньше,, чем код текущего времени в регистре 2. В этом случае сигнал на выход блока 3 не формируется, и элементы И 5 и 7 оказываются :закрытыми, а элементы И 6, 8 и 11 открытыми. Таким образом, во втором цикле код Т,ддд„ из регистра 2 начинает поступать через элемент И 8, элемент ИЛИ 13 на вход 23 вычитателя 4, а код .з регистра 1 через элемент И 6, элемент ИЛИ 14 - на вход 24 вычитателя 4. Вычитатель 4 производит операцию вычитания ( - ) и полученная разность ЛТ пройдя через элемент И 9 и элемент ИЛИ 12, вновь оказывается записанно Э регистре 1. Прохождение кода йТ через элемент И 9 обеспечивается поступлением импульса синхронизации Т- длительностью равной пачке тайВторая операция вычитания в вычитателе 4

мая разность

товых импульсов. Одновременно импульс синхронизации Т, поступающий после окончания второго цикла,, пройд элемент И 11, производит параллельную запись в регистр 2 кода 24 ч. Если коды времени представлены в двоичном коде, то в 1 устанавливаются те разряды регистра 2, сумма весовых коэффициентов которых равна двоичному коду 24 ч. Если коды времени представлены двоично-десятичным кодом, то в 1 устанавливается разряд 2 десятков часов и разряд 2 единиц часов. В этом случае третий цикл вычитания оказьшается пустым ( ЛТ2 ЛТ -0), однако это позволяет обеспечить постоянную протяженность алгоритма работы устройства при любых соотношениях межцу кодами зегдан тек соответственно упростить управление процессом вычисления По сравнению с известными устройствами предлагаемое позволяет значительно сократить объем оборудования и повысить эксплуатационную надежность устройства. В этом случае вмест-о N двоичных вычитателей и узлов коррекции (где N - сумма всех двоичных разрядов в коде времени, которые представляют собой сложные комбинационные схемы) предложенное устройство включает в себя несколько стандартных функциональных узлов (регистры, блоки сравнения и др.), которые легко реализуются на стандартных серийных элементах в микросхемном исполнении.

По сравнению с устройством-прототипом данное устройство обеспечивает неограниченность диапазона определения разности, что существенно рас11242871 ч 23 мин 16 с Коды времени 22 ч 36 мин 24 с записаны в регистры 1 и 2 22 ч 36 мин 24 с Первая операция вычитания в вычитателе 4 21 ч 13 мин 08 с

711242878

ширяет область его применения, а путем соответствующего увеличения кроме того, оно легко допускает воч- или уменьшения разрщности входможность увеличения или уменьшения ных регистров и блока сравнераэряпности вычитаемых кодов времени ния.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Генератор двоичных чисел | 1981 |

|

SU1062674A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Устройство для формирования отрезка прямой линии на экране электронно-лучевой трубки | 1979 |

|

SU919163A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1988 |

|

SU1547066A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ КОДОВ ВРЕМЕНИ, содержащее первьш и второй входные регистры, блок сравнения, вычитатель и первый элемент И, причем выходы разрядов входных регистров соединены с соответствующими разрядами первого и второго входов блока сравнения, выход которого соединен с первым входом первого элемента И, отличающееся тем, что, с целью расширения области применения за счет увеличения диапазона определения разностного времени, устройство содержит второй, тре- тий, четвертьй, пятый, шестой и седьмой элементы И, первый, второй и третий элементы ИЛИ и элемент НЕ,первый вход первого элемента ИЛИ соединен С первой входной информационной шиной устройства, a выход соединен с входом первого входного регистра, первый вход второго входного регистра соединен с второй входной И1 ормационной шиной устройства, выход старшего разряда первого входного регистра подключен к второму входу первого и к первому входу второго элементов И, выход блока сравнения соединен с входом элемента НЕ и с первым входом третьего элемента И, второй вход которого соединен с первым входом четвертого элемента И и с выходом старшего разряда второго входного регистра, выход элемента НЕ соединен с вторыми входами второго и четвертого элементов И и с первым входом пятого элемента И, выход которого подключен к второму входу второго входного регистра, выходы первого и четвертого элементов И (П соединены с соответствующими входами второго элемента ИЛИ, выходы второго и третьего элементов И подключены к соответствующим входам третьего элемента ИЛИ, выходы второго и третьего элементов ИЛИ соединены с соответствуюш 1ми входами вычитателя, выход которого подключен к первым входам шестого и седьмого элементов И, выход шестого элемента И соединен с вторьм входом первого элемента ИЛИ, выход седьмого элемента И соединен с выходной шиной устройства, вторые входы пятого, шестого и седьмого элементов И соединены соответственно с первой, второй и третьей шинами синхронизации устройства.

и

п

ТЭ

ft

Г

L

-1

.-JZJ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычитания двоичнодесятичных кодов времени | 1976 |

|

SU595730A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления разности | 1976 |

|

SU583431A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-05-23—Подача