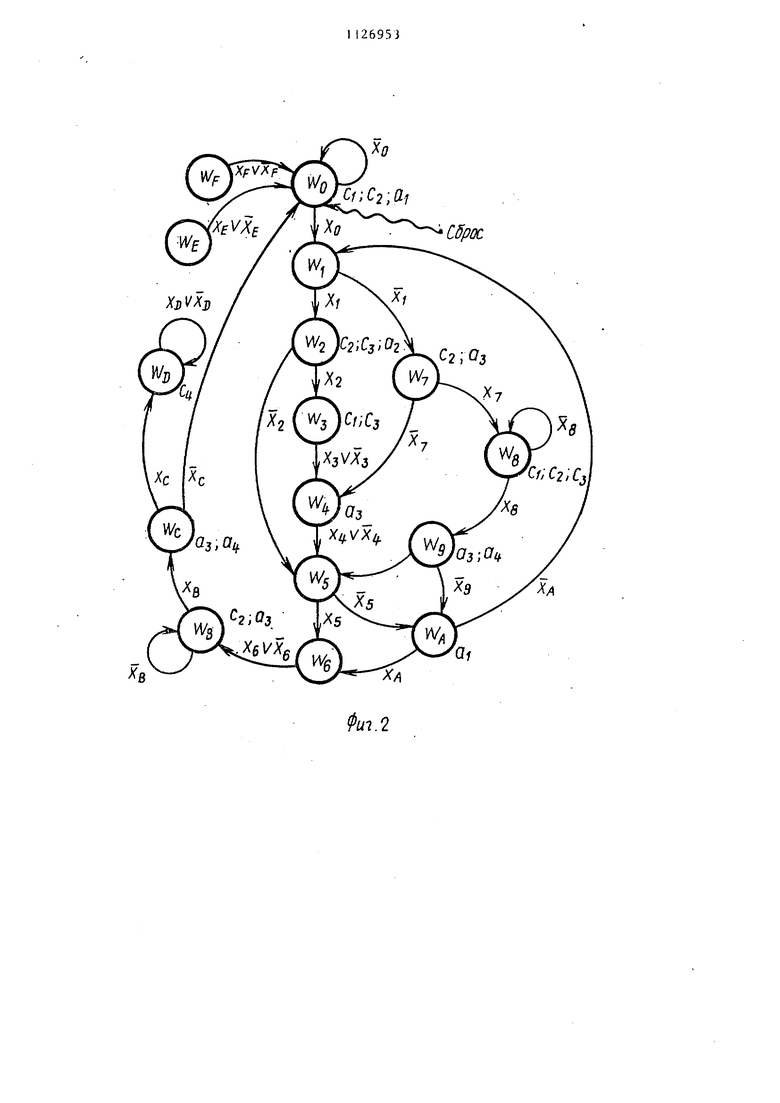

Изобретение относится к автома-, тике и вычислительной технике и может быть использовано п устройствах цифровой автоматики. Известно устройство микропрограммного управления, содержащее элементы ИЛИ, группы элементов И, блоки памяти, регистры, генератор импульсов и элемент задержки ClJНедостатком известного устройства является большой объем оборудования. Наиболее близким к предлагаемому является устройство управления, содержащее полупроводниковое постоянное запоминающее устройство (ГШЗУ), первая и вторая группы выходов которого подключены к р -входам соответственно первого и второго Б -ре гистров с динамическими.тактирующими С-входами, связанными с входной шиной тактов, входные шины усло1ВИЙ, входную шину сброса, соединенну с И-входом первого В,-регистра, вькоды которого подключены к входам старших разрядов адреса ППЗУ, а выходы второго Б -регистра соединены с шинами синхронных выходных управляющих сигналов, причем входная шина тактов подключена к блокирующему потенциальному входу схемы фикс дии, D -ВХОДЫ которой связаны с входными шинами условий, выходы схемы фиксации подключены к входам млад ших разрядов адреса ШЗУ, а входная шина сброса - с f -входом второго В-регистра. Данное устройство отличается достаточно простой структурой и применимо для реализации широкого класса устройств цифровой автоматикиfZJ. Недостатками данного устройства являются большие аппаратурные затраты, обусловленные значительным объемом ППЗУ (введение каходого входного условия требует удвоения объема ППЗУ), усложнение программирования (связанное с нарапщпанием ППЗУ) и невозможность реализации асинхрон ных выходных управляющих сигналов при произвольном изменении во времени входных условий (в этом слугае выходные сигналы ППЗУ не детерменированы) . Слояпюсть введения достато но большого числа входных условий и отсутствие асинхронных выходных упр ляющих сигналов значительно ограничивают функциональные возможности длнгюго устройства. 1 Цель изобретения - сокращение объема оборудования. Поставленная цель достигается тем, что в устройство управления, содержащее бдок памяти и два регистра, причем первая и вторая группы выходов блока памяти соединены соответствен11о с группами информационных входов первого и второго регистров, тактовые входы которых соединены с тактовым входом устройства, вход сброса первого регистра соединен с входом сброса ус.тройства, группа выходов первого регистра соединена с группой старших адресных разрядов блока памяти, группа выходов второго регистра является первой группой выходов устройства, введены триггер,, мультиплексор и элемент НЕ, причем управляющие входы мультиплексора соединены с груцпой вь ходов первого регистра, тактовый вход устройства через элемент НЕ соедр1нен. с тактовым входом триггера. D -вход которого соединен с выходом мультиплексора, информационные входы которого являются группой кодовых входов устройства, третья группа вьгходов блока памяти является второй группой выходов устройства, выход триггера соединен с младшим адресным разрядом блока памяти. На фиг. 1 приведена структурная схема устройства. Устройство содержит вход 1 сброса, группы кодовых входов 2, тактовый вход 3, мультиплексор 4, элемент НЕ 5 триггер 6, блок 7 памяти,регистры 8 и 9 группы выходов 10 и 11. Устройство работает следующим образом. Устройство (как цифровой автомат) имеет 2 устойчивых состояний -- вер,шин, где h- разрядность первого Б-регистра 8. Установочный сигнал, . поступающий на вход 1 сброса устанавливает Б -регистр 8 в начальное нулевое состо гние. В дальнейшем состояния D-регистра 8 изменяются по тактовым сигналам, поступающим по шине тактов 3 на С-вход D -регистра 8 в соотпетствии с алгоритмом функционирования устройства управления. На фиг. 2 приведен пример граф-алгоритма функционирования. На графе реализовано устройство управления на 16 состояяий -состояний-вершин от О до F (п lиecтIie дцaтиричном коде), что соответствует четырехразрйдиому регистру 8, причем четырнадцать состояний (от О до I ) являются функциональными, а. два сос тояния (ЕЙ F) - избыточными. На граф-алгоритме внутри кружков вершин приведена нумерация состояний WQ-WP (состояния регистра 8), соответствующие внутренние состояния, проверяемые внешними условиями Хр- Хр (сигналы на шинах условий 2) в прямом или инверсном виде, отмечены стрелки переходов. Кроме того, операторные вершины, в которых возбуждаются синхронные (С, С, Cj, С и/или асинхронные ( с( -I 2 3 выходные управляющие сигналы, посту пающие на выходы 10 и 11, отмечены соответствующими символами. В данно случае рассмотрен вариант четырех синхронных (регистр 9 - четырехразрядньй) и четырех асинхронных выход ных управляющих сигналов В предлагаемом устройстве управления на нумерацию вершин графа не накладываются никакие ограничения (нумерация вершин произвольная), за исключением нулевой вершины нача ного состояния WQ, в которую произ водится сброс по входу 1. Из каждого текущего состояния г вершины (в зависимости от состояния соответствующей выбранной входной шины условий) по тактовым сигна лам производится переход в одном из двух возможных последующих состояний, при этом возможны следующие варианты переходов: оба последующих состояния.различ ны между собой и отличаются от теку щего состояния (на приведенном граф . текущие состояния W , 2 №д) - вершины двух условных перехо дов-. одно из доследующих состояний повторяет текущее состояние, а второе последующее состояние отлично от него (текущие состояния VQ , Ч„ Wgj ) - вершины ожидания вьтолнения условий перехода; оба последующих состояния идентичны между собой и отличаются межд собой от текущего состояния (текущие состояния Vj , fj, W, Wg ЭДд) - вершины безусловных переходов оба последующих состояния идентичны текущему состоянию (текущее состояние WQ) - тупиковые вершины, из которых переход в иное состояние возможен только по сигналу сброса. Таким образом, предлагаемое устройство управленрш реализует все возможные последовательностные алгоритмические переходы, причем каждому состоянию поставлено в соответствие индивидуальное входное условие, поступающее с группы входов 2. Кроме того, каждая из вершин одновременно может быть операторной, т.е. п пей могут возбуждаться произвольггые наборы синхронных и/или асинхронных : выходных управляющих сигналов, поступающих соответственно на группы выходов 10 и 11. Изменение состояний устройств.а и генерации выходных управляющих сигналов происходит след тощтм образом. По входу 3 поступают внешние тактовые сигналы отрицательной полярности. Сигналы кода тек пдего состояния с выходов регистра 8 подаются на управляющие входы мультиплексора 4, который транслирует на D-вход р-триггера 6 состояние одного из входов 2, соответствующее тек тцему СОСТОЯН1ПО. Одновреме} но код текущего состояния поступает на старшие разряды адреса блока 7, а на младший разряд адреса блока 7 поступает выходной сигнал-триггера 6. В паузах между тактовыми сигналами состояния В-триггера 6, регистров 8 и 9 фиксированы, а с рыходов регистра 9 и с третьей группы выходов блока 7 на выходы 10 и 11 поступают соответственно синхронные (С - С) и асинхронные ( ot), выходные управляющие, сигналы. По переднему (отрицательному) фронту очередного тактового сигнгша, поступающему через элемент НЕ 5 на С-вход триггера 6 последний фиксирует код условия на входе 2, выбран ном мультиплексором 4 по коду текущего состояния. Код текущего состояния регистра 8 и код нового состояния триггера 6 образуют адрес блока 7, по которому на первой и втор.ой группах выходов блока 7 формируются соответственно коды последующих состояний регистров 8 и 9, поступающие на В -входы ЭТТ-ОС регистров. По заднему (положительному) фронту тактового сигнала, -поступающему на С-входы регистров 8 и 9 в последних фиксируется код последующего состояния и код синхронных выхсздных сигналов, соответству1 .1цих этому состоянию, Одновременкс на треттзей группе выходов блока 7 формируется код асинхронных выходных сигналовэ со- , ответствующий зафиксированному состояний регистра 8„ Далее состояние сохраняется неизменным до прихода следующего тактового сигнала.

Так как блок 7 имеет двоичную адресациюд то каждому из 2 состояний устройства соответствует 2 пар выходных слов блока 7 (адресация по старшим разрядам), а альтернативный выбор нужного, слова из т;ары определяется состоянием триггера б (адресация младшего разряда блока 7)

Программиров-ание блока 7 по графалгоритму является достаточно просты

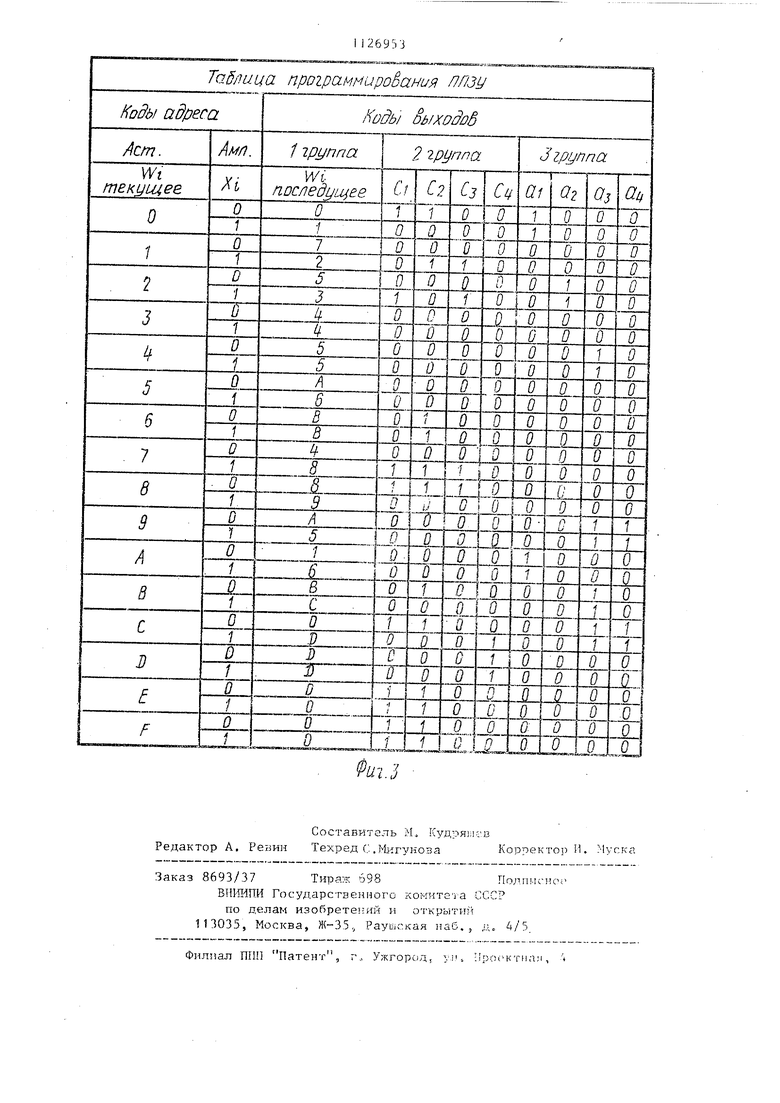

На фиг„ 3 «представлена таблица программирования, блока 7 по пример-ному граф-алгоритт.1у функционирования устройства управления,

Здесь код адреса блока 7 представлен шестнадцатиричным адресом четырех старших разрядов А (код текущего состояния регистра 8) и . двоичным адресом младшего ркзряда А, (код текущего условия Х- на л -м информационной входе 2 мультиплегсора 4, эафи1ссированньгй в триггере 6) „

Код первой группы выходов блока 7 (код последхтощего состояния регистра 8) представлен в шестнадцатиричном коде. Коды второй и третьей

групп выходов блока 7 представлены поразрядно в двоичньк кодах - соответственно столбцы синхронных (С 5 С,; 3 С,,з С) и асинхронных

5 ( , 9 2 , 3 °4 выходных управля JOIItHX сигналов.

Асинхронные выходные управляющие сигналы поступают с второй группы выходов блока 7 на выходы 11 непосредO ственно,, поэтому кодировка столбцов &1, - производится а соответствии с граф-алгоритмом по столбцу W . текпцих состоянийр Так как наборы выходных управляющих сигналов опреде 5 ляготся только внутренним состоянием устройства и не зависят от внешних условий, то их значения заносятся в таблицу идентичными парами Б две строки альтернатив0 ных значений X. для каждого vX-. Длительность просечек в асинхронных выходных упр пзляющих сигналах, возникающих на фронтах тактовых сигналов, не превышает задержки блока 7

5 (при необходимости, просечки легко устраняются последующим стробкрова- .vL-ieM или интегрированием)

Сикхронные управляющие сигналь: пес,, с второй группы выходов

Г блока 7 на выходы 1,0 через тактируемый регистр 9 с задержкой на такт,, ьюэтому кодировка столбцов С - €4 производится в соответствии с графалгоритмом по столбцу W послед таirrtix с о с то я: н ий

fa.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для вывода информации | 1988 |

|

SU1501028A2 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для определения путей в графе | 1984 |

|

SU1292000A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

.УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти и два регистра, причем первая и вторая группы выходов блока памяти соединены соответственно с группами информационных входов первого и второго регистров j тактовые входы которых соединены с тактовым входом устройства, вход сброса первого регистра соединен с входом сброса устройства. группа выходов первого регистра соединена с группой старших адресных разрядов блока памяти, группа выходов второго регистра является первой группой выходов устройства, отличающееся тем,что, с целью сокращения объема оборудования, устройство содержит триггер, мультиплексор и элемент НЕ, причем управляющие входы мультиплексора соединены с группой выходов первого регистра, тактовьг вход устройства через элемент НЕ соединен с тактовым входом триггера, 1 -вход которого соединен с выходом мультиплексора, информационные входы которого являются группой кодовых входов устройства, третья группа выходов,блока С г памяти является второй группой выходов устройства, выход триггера соединен с младшим адресным разрядом блока памяти. ГС 01

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство микропрограммного управления | 1979 |

|

SU855662A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Экспресс-информация ВИНИТИ | |||

| Сер | |||

| Приборы и элементы автоматики в вычислительной технике, 1982 № 19, с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1984-11-30—Публикация

1983-01-12—Подача