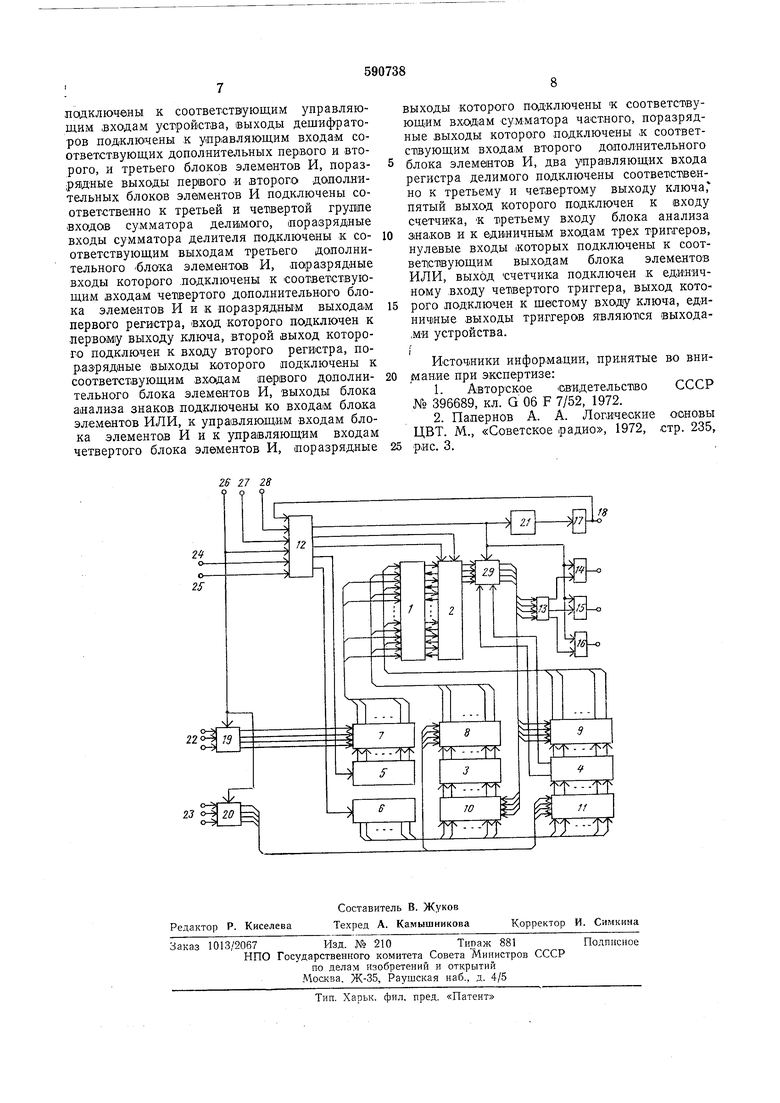

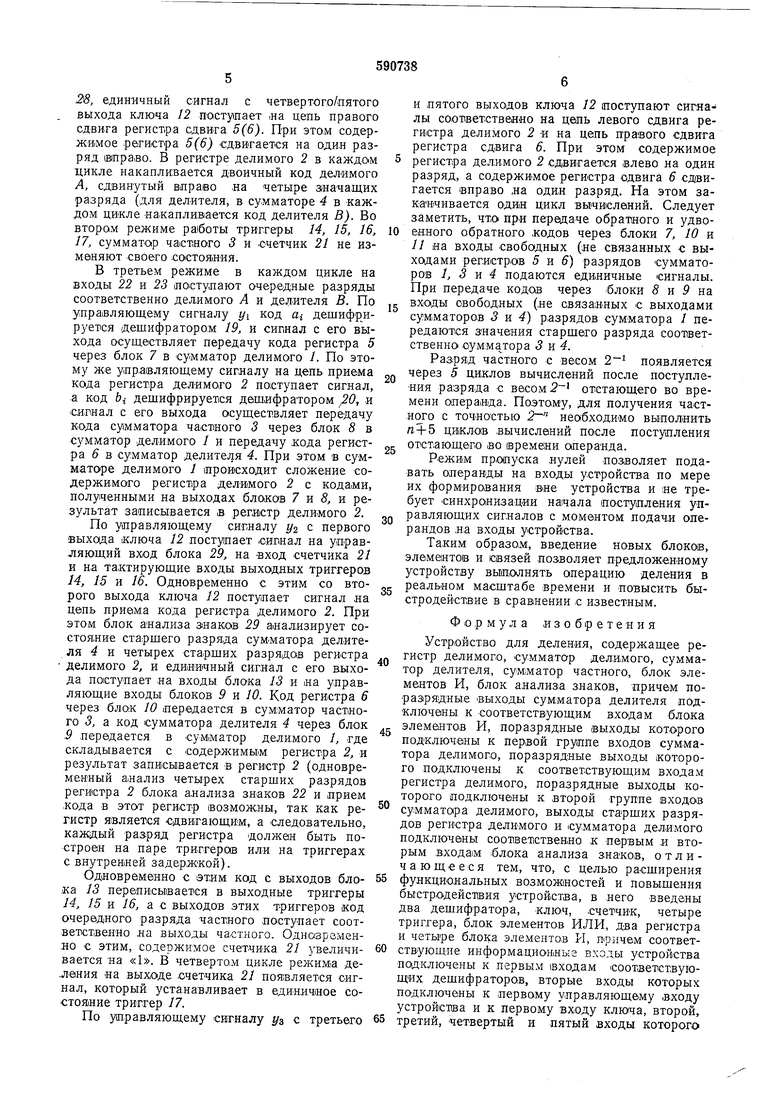

(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ первого регистра, вход .которого подключен к первому выходу ключа, второй выход которого подключен к входу второго регистра, поразряйные выходы которого подключены к соответствующим входам первого дополнительного блока элементов И, выходы блока анализа зпаков подключены к входам блока элементов ИЛИ, к управляющим входам блока элементов И и к улравляющдм входам четвертого блока элементов И, поразрядные выходы которого подключены к .соответствующим входам сумматора частного, поразрядные выходы которого подключены к соответствующим входам второго дополлительного блока элементов И, два |управляющих входа регистра делимого подключены соответственно к третьему и четвертому выходам ключа, пятый выход которого ладключеп к входу счетчи-ка, к третьему входу блока анализа знаков ,и к единичным входам трех триггеров, нулевые входы которых подключены к соответствующим выходам блока элементов ИЛИ, выход счетчика подключен к единичному входу четвертого триггера, выход которого подключён к шестому входу ключа, единичные выходы триггеров являются выходами устройства. На чертеже изображена схема устройства, где сумматор / делимого, регистр 2 делимого сумматор 5 частного, сумматор 4 делителя, регистры 5, б сдвига, блоки И 7-11 элементов, ключ 12, блок ИЛИ 13 элементов, триггеры , выход 18 триггера 17, дещифраторы 19, 20, счетчик 21, входы 22-28 устройства, блок 25 анализа знаков. Работает устройство следующим образом. Делимое А и делитель В могут поступать поразряднона входьГ блока деления одновременно без относительного сдвига, то есть в каждый -момент времени на вхо.ды поступают разряды делимого и делителя с одинаковыми весами, пли со сдвигом разрядов одного веса друг относительно друга на любое количест30 разрядов. На величины делимого Л и делителя В накладывают ся следующие ограничения: , . Ограничения на знаки делимого А и делителя В не накладываются. Стробы делимого и делителя, момент поступления которых совпадает с моментом поступления цифры с весом 2- соответствующего операнда, представляют собой сигналы, которые снимаются только по окончании поступления соответствующего операнда. Строб частного, МОМ6НТ поступления которого совпадает с моментом поступления цифры с весо.м 2 частного, представляет -сигнал, который -снимается после установки блока в исходное состояняе. Можно условно выделить три режима работы блока, а именно: 1)режим (Пропуска нулей; 2)режим приема одного операнда; 3)режим деления. Первый режим продолжается от момента начала поступления управляющих сигналов на ВХ.ОЙЫ 26, 27, 28 до момента поступления строба делимого «ли делителя. В этом случае на входы 22 и 23 очередные разряды опер андов не поступают. Второй режим блока продолжается от момента поступления строба делимого (делителя) на вход 24 (25) до момента поступления строба делителя (делимого) на вход 25(24). Третий режим работы блока начинается непосредственно после окончания второго режима и продолжается до момента получения требуемого количества разрядов частного С. Перед началом вычисления в старший разряд регистров сдвига 5 и 6 записана единица, а остальные сумм:аторы, триггеры, счетчик и регистр блока установлены в нулевое состояние. В каждом цикле вычислений на управляющие входы 26, 27 и 2S поочередно поступают соответственно управляющие сигналы г/ь г/2 и Уз. В режиме пропуска нулей стробы делимого и делителя отсутствуют. В этом случае сумматоры, регистры, триггеры и счетчик блока не изменяют своего состояния, При поступлении на вход 24 или 25 строба операнда, блок .переходит в реж.и,м приема одного операнда. Предположим, что первым прищел строб делимого (делителя) на вход 24(25) ,и соответственно старший разряд делимого GI (делителя &) на входы 22(23). Тогда до прихода строба делителя (делпмого), по управляющему сигналу г/, поступаю У « управляющий вход 26, на цепь прие регистра делимого 2 со второго выхода ключа 12 поступает единичный сигнал, а на управляющие входы дешифраторов 19 и 20 поступает сигнал. Прл этом код разряда делимого (делителя) дешифрируется дешифратором 19(20), и единичный сигнал с его выхода поступает ,на управляющие входы блока элементов И 7. В результате этого код регистра сдвига 5 через блок элементов И передается в сумматор делимого /, а через блок ° сумматора частного 3 передается в сумматор делимого /. При этом, если цифра операнда «2, то блоки 7 и // передают удвоенныи прямой код, а блок 8 - удвоенный обратный код. Для «1 .блоки 7 и // пере прямой код, блок 8 - обратный код, . Ь блок 7 и // передают обратный код, блок 8 - прямой код, для «2 блоки 7 и // передают удвоенный обратный код, а блок 5 - -удвоенный прямой код. Бели цифра операнда «О, то блоки 7, 8 и 11 кода не передают. Управляющий сигиал г/г, поступающий «а управляющий вход 27, не изменяет состояния блока, а по управляющему сигналу УЗ, поступающему яа управляющий вход

2в, единичный сигнал с четвертого/пятого выхода ключа 12 поступает ,на цепь правого сдвига регист.р:а сдвига 5(6). При этом содержигмое регистра 5(6) сдвИгается на один разряд онправо. В регистре делимого 2 в каждом цикле накапливается двоичный код делимого А, сдвинутый BnpaiBO на четыре значащих разряда (для делителя, в сумматоре 4 в каждом цикле на.капливается код делителя В). Во втором режиме работы триггеры 14, 15, 16, 17, сумматор частного 3 и счетчик 21 не изменяют .своего .састояйия.

В третьем режиме в каждом цикле на входы 22 и 23 лостулают очередные разряды соответственно делимого А и делителя В. По управляющему сигналу у код а дешифрируется дешифратором 19, и силнал с его выхода асуш,ествляет передачу кода регистра 5 через блок 7 в сумматор делимого /. По этому же упрл1вляюш,ему сигналу на цепь приема кода регистра делимого 2 поступает сигнал, а код bi дешифрируется дешифратором (, и сигнал с его выхода осуществляет передачу кода сумматора частного 3 через блок 8 в сумматор делимого / и передачу кода регистра 6 в сумматор делителя 4. При этом в сумматоре делимого 1 -происходит сложение содержимого регистра делимого 2 с кодами, полученными на выходах блоков 7 и S, и результат записывается в регистр делимого 2. По управляющему сигналу г/2 с первого выхода (Ключа 12 поступает силнал на управляющий вход блока 29, на вход счетчика 21 и на тактирующие входы выходных триггеров 14, 15 и 16. Одновременно с этим со второго выхода ключа 12 поступает сигнал на цепь приема кода регистра делимого 2. При этом блок анализа 31наков 29 анализирует состояние старшего разряда сумматора делителя 4 и четырех старших разрядов регистра делимого 2, и единичный сигнал с его выхода поступает на входы блока 13 и на управляющие входы блоков 9 и 10. Код регистра в через бло;к 10 передается в сум.матор частного 3, а код сумматора делителя 4 через блок ,5 передается в сумматор делимого /, где складывается с содержимым регистра 2, и результат записывается в регистр 2 (одновременный анализ четырех старших разрядов регистра 2 блока анализа зваков 22 и прием .кода в этот регистр возможны, так как регистр является сдвигающим, а следовательно, каждый разряд регистра должен быть построен на паре триггеров или на триггерах с внутренней задержкой).

Одновременно с этим код с выходов блоа 13 переписывается в выходные триггеры 14, 15 и 16, а с выходов этих триггеров код очередного разряда частного поступает соответственно .на выходы частного. Однаараменно с этим, содержимое счетчика 21 увеличивается на «1. В четвертом цикле режим1а деения на выходе счетчика 21 поя1вляется сигнал, который устанавливает в единичное сотоя1ние триггер 17.

По управляющему сигналу уз с третьего

И пятого выходов ключа 12 поступают сигналы соответственно на цепь левого сдвига регистра делимого 2 « на цепь правого сдвига регистра сдвига 6. При этом содержимое регистра делимого 2 сдвигается влево на один разряд, а содержимое регистра сдвига 6 сдвигается вправо на один разряд. На этом заканчивается один цикл вычислений. Следует заметить, что при передаче обратного и удвоенного обратного кодов через блоки 7, 10 и // на входы свободных (не связанных с выходами регистров 5 и 6) разрядов сумматоров 1, 3 vi 4 подаются единичные сигналы. При передаче кодов через блоки 5 и 9 на входы свободных (не связанных с выходами сумматоров 3 к. 4) р1азрядов сумматора 7 передаются значения старшего разряда соответственно оумма тора и 4.

Разряд частного с весом появляется через 5 циклов вычислений после поступления разряда с весом отстающего во времени операнда. Поэтому, для получения частного с точностью 2 необходимо выполнить «+5 циклов .вычислений после поступления отстающего во времени операнда.

Р.ежим пргоиуска .нулей позволяет подавать операнды на входы устройства по мере их формирования вне устройства и не требует синхронизации начала поступления управляющих сигналов с моментом подач.и опера.ндов .на входы устройства.

Та.ким образо,м, введение новых блоков, элементов и связей .позволяет предложенному устройству вып олнять операцию деления в реальном масштабе времени и повысить быстродействие в сравнении с известным.

Ф о .р м у л а изобретения

Устройство для деления, содержащее регистр делимого, сумматор делимого, сумматор делителя, сумматор частного, блок элементов И, блок анализа знаков, причем поразрядные ВЫХОДЫ сумматора делителя подключены к соответствующим входам бло.ка элементов И, поразрядные выходы которого подключены к первой группе входов сум.матора делимого, поразрядные выходы которого подключены к соответствующим входам регистра делимого, поразрядные выходы которого подключены к второй группе входов сумматора делимого, выходы старших разрядов регистра делимого и сумматора дел.имого подключены соответственно к первым я вторым входам блока анализа знаков, отличающееся тем, что, с целью расширения функциональных возмож1ностей и повышения быстродействия устройства, в него введены два дешифр.атора, ключ, .счетчик, четыре триггера, блок элементов ИЛИ, два регистра и четыре блока элементо.в И, причем соответствующее информационные входы устройства подключены к первым 1входам соответствующих дешифраторов, вторые входы которых подключены к первому управляющему входу устройства и к первому входу ключа, второй, третий, четвертый и пятый входы которого

подключены к соответствующим управляющим входам устройства, выходы дещифраторов подключены к у,пр1авляющим входам соответствующих дополнительных первого и второго, и третьего блоков элементов И, поразрядные выходы первого и второго доподнительных блоков элементов И подключены соответственно к третьей и четвертой группе входов сумматора делимого, поразрядные входы сумматора делителя подключены к соответствующим выходам третьего дополнительного блока элементов И, поразрядные входы которого .подключены к соответствующим входам четаертого дополнительного блока элементов И и к поразрядным выходам первого регистра, вход которого подключен к первому выходу ключа, второй выход которого подключен к входу второго регистра, поразрядные выходы которого подключены к соответствующим входам первого дополнительного блока элементов И, выходы блока анализа знаков подключены ко входам блока элементов ИЛИ, к управляющим входам блока элементов И и к управляющим входам четвертого блока элементов И, поразрядные

выходы которого подключены к соответствующим входам сум-матора частного, поразрядные выходы которого подключены к соответствующим входам второго дополнительного

блока элементов И, два управляющих входа регистра делимого подключены соответственно к третьему и четвертому выходу ключа, пятый выход которого подключен к входу счетчика, к третьему входу блока анализа

знаков и к единичным входам трех триггеров, нулевые входы которых подключены к соответствующим выходам блока элементов ИЛИ, выход Счетчика подключен к единичному входу четвертого триггера, выход которого подключен к шестому входу ключа, единичные выходы триггеров являются выхода,МИ устройства.

. I

Источники информации, принятые во внимание при экспертизе:

1.Авторское Свидетельство СССР № 396689, кл. G 06 F 7/52, 1972.

2.Папернов А. А. Логические основы ЦВТ. М., «Советское радио, 1972, стр. 235,

рис. 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Устройство для деления | 1974 |

|

SU556435A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

Г

23 о 0-&

Авторы

Даты

1978-01-30—Публикация

1976-01-09—Подача