. Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Известно вычислительное устройст во, содержащее четыре цифровых управ ляемых сопротивления, включенные по мостовой схеме, усилитель разбаланса преобразователь аналог - код Л . Однако устройство решает сравнительно малый класс задач. Наиболее близким к изобретению яв ляется вычислительное устройство,содержа 1ее первый и второй элементы с управляемой проводимостью, выполненные на полевых транзисторах, первое цифровое управляемое сопротивление, первый вывод ко.торого соединен с первым выводом первого ключа, второе цифровое управляемое сопротивление, выводыкоторого подключены к истокам соответственно первого и вто рого полевых транзисторов, затворы которых являются соответственно первым и вторым входами устройства, пер вый масштабный резистор, первый вы вод которого соединен с вторым вьтодом первого цифрового управляемого сопротивления и с первым выводом источника питания, второй масштабный резистор, первый вывод которого подключен к первому выводу третьего циф рового управляемого сопротивления, к истоку первого полевого транзистора и к первому входу нуль-органа, второй вход которого соединен с вторым выводом первого ключа, второй вывод .второго масштабного резистора через второй ключ подключен к первому выводу четвертого цифрового управ ляемого сопротивления, к истоку вто рого полевого транзистора и второму выводу источника питания, первый вывод первого масштабного резистора через третий ключ соединен с вторым выводом третьего цифрового управляемого сопротивления, второй вывод чет вертого цифрового управляемого сопро тивления через четвертый ключ подклю чен .к второму входу нуль-органа, второй вывод первого масштабного резистора через пять1й ключ соединен с вторым входом нуль-органа, выход которого подключен к входу блока управ ления, выход которого соединен с управляющим входом второго цифрового управляемого сопротивления, с первым входом коммутатора кодов и входом дешифратора, выход которого подключен к входу блока отсчета, выход коммутатора кодов соединен с управляющим входом первого 1шфрового управляемого сопротивления, второй вход коммутатора кодов, управляющие входы третьего и четвертого цифровых управляемых сопротивлений являются соответственно первым, вторым и третьим установочными входами устройства, сток перэого полевого транзистора соединен с вторым выводом первого цифрового управляемого сопротивления, второй вывод первого ключа соединен со стоком второго полевого транзистора 2j . Недостатком устройства является сравнительно узкий класс решаемых задач. Цель изобретения - расширение класса решаемых задач. Цель достигается тем, что в вычислительное устройство, содержащее первый и второй элементы с управляемой проводимостью, выполненные на полевых транзисторах, первое цифровое управляемое сопротивление, первый вывод которого соединен с первым выводом первого ключа, второе цифровое управляемое сопротивление, выводы которого подключены к истокам соответственно первого и второго полевых транзисторов, затворы которых являются соответственно первым и вторым входами устройства, первый масштабный резистор, первый вывОд которого соединен с вторым выводом первого цифрового управляемого сопротивления и с первым выводом источника питания, второй масштабный резистор , первый вывод которого подключен к первому выводу третьего цифрового управляемого сопротивления, к истоку первого полевого транзистора и к первому входу нуль-органа, второй вход которого соединен с вторым выводом первого ключа, второй вьшод второго масштабного резистора через второй ключ подключен к первому выводу четвертого цифрового управляемого сопротивления, к истоку второго полевого транзистора и второму выводу источника питания, первый вывод первого маспггабного резистора через третий ключ соединен с вторым выводом третьего цифрового управляемого сопротивления, второй вывод четвертого цифрового управляемого

сопротивления через четвертый ключ подключен к второму входу нуль-органа, второй вывод первого масштабного резистора через пятый ключ соединен с вторым входом нуль-органа, выход которого подключен к входу блока управления, выход которого соединен с управляющим входом второго цифрового управляемого сопротивления, с первым входом коммутатора кодов и входом дешифратора, выход которого подключен к входу блока отсчета, выход коммутатора кодов соединен с управляющим входом первого цифрового з равляемого сопротивления, второй вход коммутатора кодов, управляющие входы третьего и четвертого цифровых управляемых сопротивлений являются соответственно первым, вторым и третьим установочными входами устройства, введены шестой и седьмой ключи, причем сток первого полевого транзистора через шестой ключ соединен с вторым выводом первого цифрового управляемого сопротивления, сток второго полевого транз.истора через седьмой ключ подключен к второму выводу первого ключа.

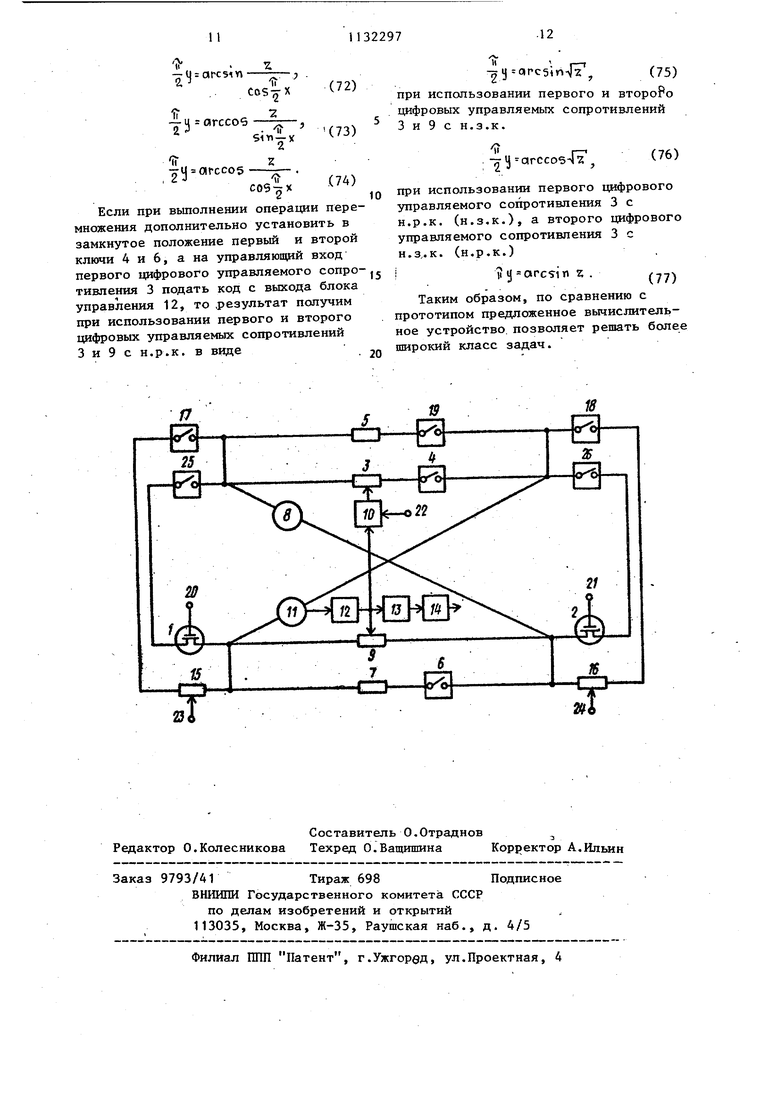

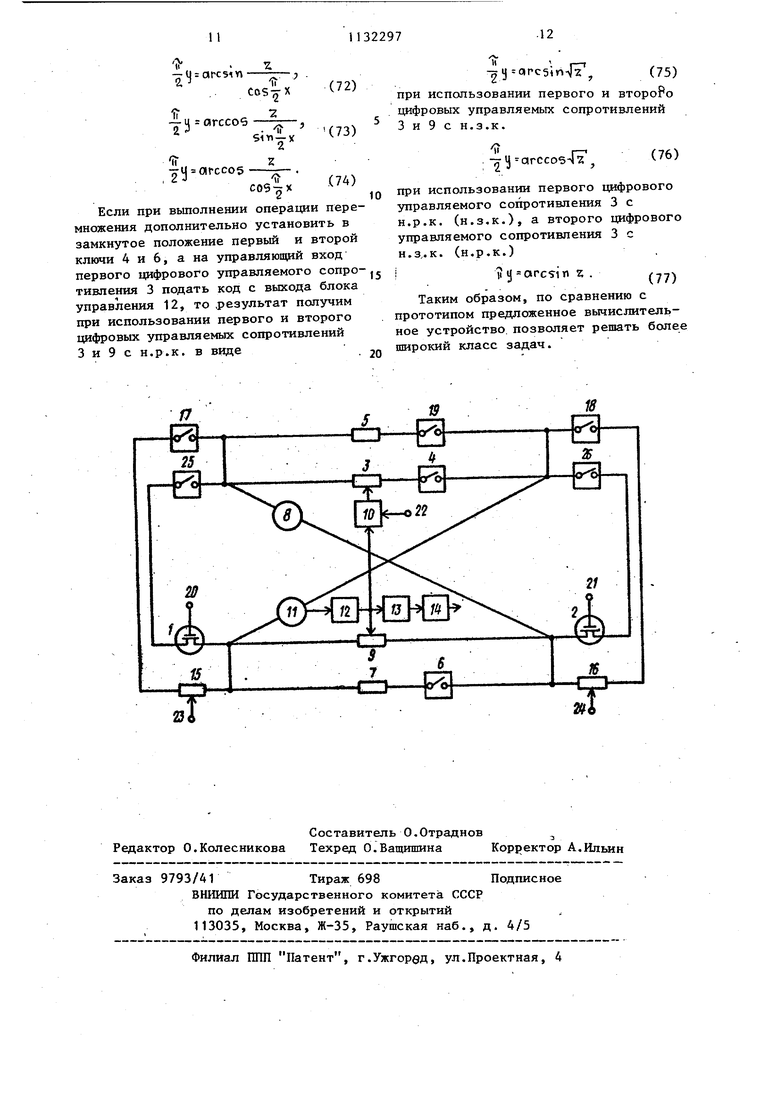

На чертеже изображена функциональная схема предложенного вычислительного устройства.

На схеме обозначены первый и второй полевые транзисторы 1 и 2, первое цифровое управляемое сопротивление 3, первый ключ 4, первый масштаб ный резистор 5, второй ключ 6, второй масштабный резистор 7, источник питания 8, второе цифровое управляемое сопротивление 9, коммутатор кодов 10, нуль-орган 11, блок управления 12, дешифратор 13, блок отсчета 14, третье и четвертое цифровые управляемые сопротивления 15 и 16, третий - пятый ключи 17 - 19, первый и второй входы 20 и 21, первый - тре тий установочные входы 22 - 24, шестой и седьмой ключи 25 и 26.

Вычислительное устройство работает следующим обра.зом.

Первый и второй полевые транзисторы 1 и 2, выполняющие функции управляемых проводимостей, первое цифровое управляемое сопротивление 3 первый ключ 4 и второе цифровое управляемое сопротивление 9 образуют множительный мост. В зависимости от этого, какие элементы вклю1чены в плечи этого моста (посредством соответствуюр их ключей), -вычислительное устройство выполняет ту или иную операцию.

Вьшолнение операции перемножения двух величин. С первого и второго входов 20 и 21 на затворы первого и второго полевых транзисторов 1 и 2 поступают напряжения Ц, и U2 которые отображают аналоговые сомножители. При мальк значениях напряжения стока сопротивление кангша стокисток полевого транзистора прямо пропорционально напряжению, приложенному к затвору.

На второй и третий устанойочные входы 23 и 24 поступают коды N и N, которые отображают цифровые сомножители. Относительные значения кодов:

- maxN,

(2)

N

max

Первый, случай. Замкнуты третий пятый ключи 17 - 19. Условие равновесия множительного моста записьшается как

R,R R,-R

(3)

16

RC - сопротивление первого

де масштабного резистора 5;

у - текущее значение второго цифрового управляемого сопротивления 9 с нормально разомкнутыми ключами (н..) в функции управляющего кода y Nf/Nway

R Кд-р - текущее значение третьего цифрового управляемого сопротивления 15 с н.р.к. в функции кода Nj;

R ROг - текущее значение четвертого цифрового управляемого сопротивления 16 с н.р.к. в функции кода Rjj - полное сопротивление цифрового управляемого сопротивления. Из условия равновесия (3) следует

y l S-p-r, (4) .о

« ъ-/const.

Второй случай. Замкнуты третий пятый и седьмой ключи 17 - 19 и 26. Если напряжение на втором входе 21 выбрать из условия R2-k-U.,H.8Ro, (5) где R, - сопротивление канала второ го полевого транзистора 2, Чогда общее сопротивление параллельно соединенных четвертого цифрового управляемого сопротивления 16 и второго полевого транзистора 2 равно .R . в - oTTe+l- (6) 1,8+f Известно, что с погрешностью, не превьшающей 0,1%, lti;V 1- (« Из условия равновесия множит.ельного моста RqRs iV в (8) с учетом вьфажений (6)и (7) полу чим . (Т Ij-l yp-Sin -T. (9) Если использовать четвертое цифровое управляемое сопротивление 16 с нормально замкнутыми ключами (н.з.к.) текущее сопротивление которого равно - Rife-RoM: - / .(10) тогда общее сопротивление равно .8(1-f) , (11) Известно, что с погрешностью 0,1% 16 «О -iT 8г;:- ° т- (t2) . Из условия равновесия множительно го моста (8) с учетом выражений (11) и (12) 1| К,.р.Соб|.г, (3) Аналогично при замкнутых третьем шестом ключах 17 - 19 и 25 и при условииR, X,-U,M,8Ro. (14) Общее сопротивление параллельно соединенных первого полевого транзис тора 1 и третьего цифрового управляе мого сопротивления 15 равно . (15) или 13U-P) о ir Из условия равновесия множительно го моста и с учетом выражений (15) и (16) ЧГ (17) tJ t-Sin- р,: tj Kjf coe-g-p, В третьем случае замкнуты третий седьмой ключи 17 - 19, 25 и 26. При этом в одно плечо множительного моста включены параллельно соединенные третье цифровое управляемое сопротивление 15 и первый полевой транзистор 1, общее сопротивление которых определяется (15) или (16), а в другое плечо включены параллельно соединенные четвертое цифровое управляемое сопротивление 16 и второй полевой транзистор 2, общее сопротивление которых определяется (6) или (11). Из условия равновесия множительного моста для третьего случая имеем при использовании третьего и четвертого цифровых управляемых сопротивлений 15 и 16с н.р.к. y v,si4p5 4. 19) при использовании этих же сопротив- лений с н.3.к. y-K.-co p-coel., (20) при использовании третьего цифрового управляемого сопротивления 15 с н.р.к. (н.з.к.), а четвертого Щ1фрового управляемого сопротивления 16 с н.з.к. (н.р.к.) соответственно y V,.6in-p-co5-т . 1} К,.со9|р., В четвертом случае замкнуты пятый седьмой ключи 19, 25 и 26. Условие равновесия множительного моста. R,. (23) где Ед - сопротивление канала первого полевого транзистора 1. С учетом прямой пропорциональности сопротивления канала сток-исток полевого транзистора величине напряжения, на его затворе имеем y K4-U,.U2, (24) где В пятом случае замкнуты четвертый - седьмой ключи 18, 19, 25 и 26. Если значение кода на третьем установочном входе 24 выбрать из условия.8Я, (25) где R - сопротивление второго полевого транзистора 2 при максимальном напряжении на втором входе 21, общее сопротивление параллельно соединенных четвертого цифрового сопротивления 16 и второго полевого тракзистора 2; в этом случае равно 0- о l., ( Д и 77 15 Из, условия равновесия множительного моста . 5 С (.2/J с учетом (26) получим II V .11 .я;и -II y-XgU, s.ngU, (28) где ... K.-R . l, „ Если U 7j TO о M KcUfin -U , (29) Если на второй вход 21 подать напряжение (,-,), то 30 Г И.&И-и, К С - , 2.8-U2 . Из усЛовия равновесия множительного моста с учетом (30) Ч CCS-и Аналогично при замкнзггых третьем, пятом - седьмом ключах 17, 19, 25 и 26 при соответствующем выборе кода на втором установочном входе 23, выполняющем роль опорной величины , .S+Tl, (32) или J-«-4fi 5 (33) ИЗ условия равновесия множительного моста получаем соответственно I. V II , 50 .y-kj-U -S n-gUj. (34) . или ГЧи.,. В шестом случае замкнуты третий - 55 седьмой ключи 17 - 19, 25 и 26. Из условия равновесия множительного моста получим ,,IjVirei U.-sin Uj, (36) , Со9-U. , П7) з ч. 2 . 7. IT . r 5 2-lJi-co5-2U2 , (38) п - - и I) 1.:7со5 gUiSiM и 2 - (39) В седьмом случае замкнуты третий, пятый и седьмой ключи 17, 19 и 26. условия равновесия множительного моста 9-Si5-R2 (0) получим а (41) При замкнутых четвертом - шестом ключах 18, 19 и 25 при условии равновесия множительного моста R. sRieRi (2) получим ,, (43) где t . восьмом случае замкнуты четвертый - седьмой ключи 18, 19, 25 и 26. условия равновесия множительного моста 9 в .(44) получим у и,5,4г. (45) Если использовать четвертое цифро- . it вое управляемое сопротивление 16 с н.з.к., то из условия равновесия множительного моста получим lj KgU,cog-т. Аналогично при замкнутых третьем, пятом - седьмом ключах 17, 19, 25 и 26 имеем для третьего цифрового управляемого сопротивления 15 с н.р.к. и н.э.к, соответственно: ., ., „ . -IT Ч A 7 7i:P 1 fii э о 2 (47) ,-|р. «8, В девятом случае замкнуты третий « седьмой ключи 17 - 19 и 26. Из условия равновесия множительного моста y,,p.5in.-|u2 (49) или1, Ч .-и,. (50) Р замкнутых третьем - шестом ключах 17 - 19 и 25 получим r-c-Ji/i (51) 3 10 W . . « « у-1с,огсо9-|и,. (52) В десятом случае замкнуты третий седьмой ключи 17 - 19, 25 и 26. Из условия равновесия множительного мое та для этого случае имеем (|-K,,5i«|-p5in|-U2. Аналогично можно получить; у нС05-|-рсо5 и2 7 l( l,,sin|-pco9-|-U2, Lj-l,,,n|U2. (56) В одиннадцатом случае замкнуты третий - седьмой ключи 17 - 19, 25 и 26. Из условия равновесия множительного моста имеей f K,,, (57) У-1,2С05|гсо5 и,, (58) ,, (59) Ч 1 «соб|гб,п|и,. (60) Во всех рассмотренных случаях при разбалансе -множительного моста нульорган 11 по величине и знаку рассог(Ласования формирует импульсы, которые поступают в блок управления 12. Последний изменяет состояние второго цифрового управляемого сопротивле НИН 9 до момента установления равновесия множительного моста, после чего информация преобразуется дешифратором 13 в удобную для отсчета форму Если в- указанных случаях выполнения операции перемножения вместо пятого ключа 19 установить в замкнутое положение первый ключ 4 и на управляющий вход первого цифрового управляемого сопротивления 3 подать код с выхода блока управления 12, то получим результат в виде (1) где Z - результат выполнения множительной операции в указанных случаях. Если вместо пятого ключа 19 установить в замкнутое положение первый ключ 4, а коммзтатор кодов 10 установить в положение, при котором к уп равляющему входу первого цифрового управляемого сопротивления 3 подключен код с первого установочного входа 22, то получим результат в виде гт J4 код с первого установочного входа 22. Если при выполнении операции перемножения установить в замкнутое положение первый ключ 4 и подать на управляющий вход первого цифрового управляемого сопротивления 3 код с первого установочного входа 22, то при выборе сопротивления первого масштабного резистора 5 RgM.SRo результат примет вид 2, Если при выполнении операции перемножения дополнительно установить в замкнутое положение второй ключ 6, то при выборе сопротивления второго масштабного резистора 7 ,8Ro конечный результат примет вид .IT - j orcsinz или - 1} агссо5% . Если при вьтолнении операции перемножения вместо пятого ключа 19 установить в замкнутое положение первый второй ключи 4 и 6 и на управляюий вход первого цифрового управляеого сопротивления 3 подать код с ервого установочного входа 22, то олучим результат в виде -g- j arcsin2ij apcco9Если при вьшолнении операции перемножения дополнительно установить в замкнутое положение первый и второй ключи 4 и 6, а на управляющий вход первого цифрового управляемого сопротивления 3 подать код с первого становочного входа 22, то результат олучим в ввде - (jiorcsiirt -yij arcco9 oircco5 coe-gx Если при вьшолнении операции пере множения дополнительно установить в замкнутое положение первый и второй ключи 4 и 6, а на управляющий вход первого цифрового управляемого сопро тивления 3 подать код с выхода блока управления 12, то результат получим при использовании первого и второго цифровых управляемых сопротивлений 3 и 9 с Н.Р.К. в виде - у-агсбшл (75) при использовании первого и второРо цифровых управляемых сопротивлений 3 и 9 с н.э.к. - ij arccos-Ti., (76) при использовании первого цифрового управляемого сопротивления 3 с н.р.к. (н.з.к.), а второго цифрового управляемого сопротивления 3 с н.з.к. (н.р.к.) iiii| arcsiTi z . j Таким образом, по сравнению с прототипом предложенное вычислительное устройство, позволяет решать более широкий класс задач.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1982 |

|

SU1080152A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Множительно-делительное устройство | 1982 |

|

SU1030810A1 |

| Аналоговое множительное устройство | 1986 |

|

SU1319047A1 |

| Множительное устройство | 1977 |

|

SU667971A1 |

| Преобразователь перемещения в код | 1983 |

|

SU1164883A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Аналоговое множительное устройство | 1985 |

|

SU1280401A1 |

| Аналоговое множительно-делительное устройство | 1989 |

|

SU1640717A1 |

| Аналоговое делительное устройство | 1980 |

|

SU957224A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый и второй элементы с управляемой проводимостью, выпол.ненные на полевых транзисторах, первое цифровое управляемое сопротивление, первый вывод которого соединен с первым выводом первого ключа, второе цифровое управляемое опротивление, выводы которого подключены к истокам соответственно первого и второго полевых транзисторов, затворы которых являются соответственно первым и вторым входами устройства, первый масштабный резистор, первый вывод которого соединен с вторым выводом первого цифрового управляемого сопротивления и и первым выводом источника питания, второй масштабный резистор, первый вьшод которого подключен к первому выводу третьего цифрового управляемого сопротивления, к истоку первого полевого транзистора и к первому входу нуль-органа, второй вход которого соединен с вторым выводом первого ключа, второй вывод второго масштабного резистора через Ьторой ключ подклю(чен к первому выводу четвертого цифрового управляемого сопротивления, к истоку второго полевого транзистора и второму выводу источника питания, первый вывод первого масштабного резистора через третий ключ соединен с вторым выводом третьего цифрового управляемого сопротивления, второй вывод четвертого цифрового управляемого сопротивления через четвертый ключ подключен к второму входу нуль-органа, второй вывод первого масштабного резистора через пятый ключ соединен с вторым входом нуль-органа, выход которого подключен к входу блока управления, выход которого соединен с -управляющим входом второго цифрового управляемого сопротивления, с первым входом коммутатора кодов и входом дешифратора, выход которого подключен к входу блока отсчета, выход коммутатора кодов соединен с управляющим входом первого цифрового управляе мого сопротивления, второй вход коммутатора кодов, управляющие входы третьего и четвертого цифровых управляемых сопротивлений являются соответственно первым, вторым и третьим установочными входами устройства, отличающееся тем, что, с целью расширения класса решаемых задач , в него введены естой и седьмой ключи, причем сток первого полевого транзистора через, шестой ключ соединен с вторым выводом первого цифрового управляемого сопротивления, сток второго полевого транзистора через седьмой ключ подключен к второму выводу первого ключа.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смолов В.Б | |||

| и др | |||

| Мостовые вычислительные устройства | |||

| Л., Энергия, 1971, с | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3494438/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-30—Публикация

1983-09-01—Подача