(S4) МНаПО1КЖ ОГСЯВЫЙ ЛОГИЧЕСКИЙ ЭЛ ЕМЕНТ ЧЕТНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| Многопороговый логический элемент | 1979 |

|

SU788384A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU900455A2 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2000 |

|

RU2189110C2 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент | 1979 |

|

SU790341A1 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Многопороговый логический элемент | 1985 |

|

SU1272499A2 |

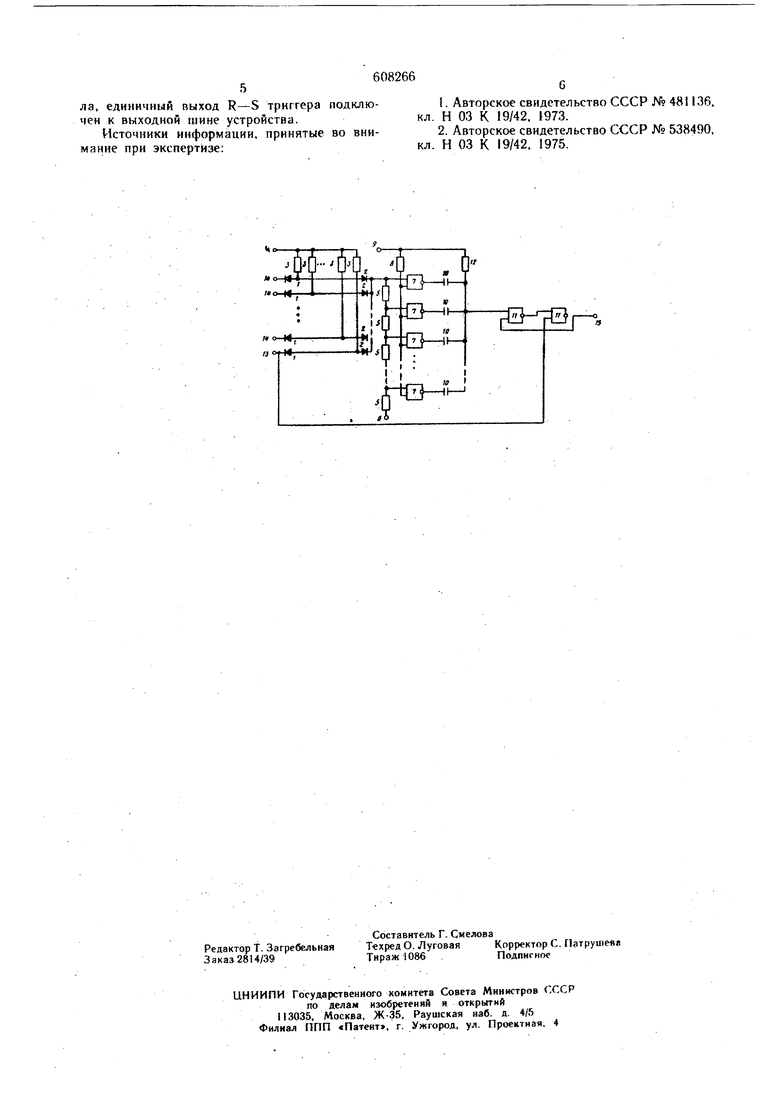

Изобретение относится к области автоматики и вычислительной техники, в частности к пороговым логическим элементам. Известны многопороговые логические элемеитЫ| содержащие линейный сумматор, выполненный на резисторах и управляемый входШлми диодами, и многопороговый дискриминатор 11. Недостаток известных многопороговых Логических элементов заключается в том, что lix быстродействие определяется числом переменных, от которых реализуется логическая фуикцня, и оно тем ниже, чем больше входов имеет многопороговый элемент. Кроме того, примеиение подобных многопороговых логических элементов с различным чнслом входов в одном цифровом устройстве требует наличия в Нем синхронизирующих устройств, так как быстродействие устройства будет определяться пороговым элементом с наибольшим числом входов. Наиболее близким по технической сущности к предложенному устройству является миогопороговый логический элемент четности, содержащий линейнь1Й сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к источнику смещення и к анодам соответствующих раздеЛнтельных Диодов, катоды которых соедииены со входом резисторного делителя, выходы которого соединены с первыми входами .соответствующих элементов И-НЕ, и R-S триггер, выполненный на двух элементах И-НЕ (2. Недостаток известного устройства -низкое быстродействие. Цель изобретения-повышение быстродействия устройства. Это достигается тем, что в многопороговый логический элемент четности, содержащий линейный сумматор, состоящий нз входных диодов, аноды которых через соответствующие резисторы подключены к источнику смещения и к анодам соответствуюпхих разделительных диодов, катоды которых соединены с входом резисториого делителя, выходы которого соединены ё первыми входами соответствующих элементов И-НЕ, и R-S триггер, выполненный на двух элементах И-НЕ, введены разделительные конденсаторы и резисторы, вторые входы элементов И-НЕ через резистор подключены к положительной щине питания, нулевой вход R-S триггера через разделительные конденсаторы соединен с выходами элементов. И-НЕ и через резистор - с положительной шиной питания, единичный вход R - S триггера подключен к одному из входов линейного сумматора и к шине стробирующего сигнала, единичный выход R-S триггера подключен к выходной шине устройства. На чертеже изображена принципиальная ехема предлагаемого многопорогового логического элемента четности. Многопороговый логический элемент состоит из линейного сумматора, имеющего п основных и один дополнительный вход, многопорогового дискриминатора, дифференцирующих цепей и R-S триггера. Линейный сумматор для каждого входа содержит попарно соединенные входные I и разделительные 2 диоды. Каждая пара диодов в точках, объединяющих их аноды через резисторы 3, управляющие весовыми коэффициентами по соответствующему входу, подключена к положительному полюсу 4 источника смещения. Катодь диодов 2 объединены и подсоединены через делитель, состоящий из резисторов 5, к отрицательному полюсу 6 источника смещения, причем выходы делителя соединены с первыми входами соответствующих элементов И-НЕ 7, образующих многопороговый дискриминатор, развязывая тем самым каждый последующий однопороговый дискриминатор на двухвходовом элементе И-НЕ 7 с большим значением порога, чем предыдущий. Другие входы элементов И-НЕ 7 через резистор 8 подключены к положительной щине 9 источника питания. Выходы однопороговых дискриминаторов через конденсаторы 10 объединены и подсоединены к нулевому входу R-S триггера на элементах 11, а через резистор 12 - к положительной щине 9 источника питания. Единичный R-S триггера подключен к дополнительному вхоДу 13 линейного сумматора. ШинЫ 14 являются основными входами линейного сумматора. Единичный выход R-S триггера, соединенный с щиной 15, является выходом многопорогового элемента. Работает многопороговый логический элемент четности следующим образом. Значения весовых коэффициентов основных .и дополнительного входа линейного сумматора равны единице; порог срабатывания первого из дискриминаторов на элементах И-НЕ 7 равен двум. Пороги срабатывания следующих по порядку дискриминаторов равны соответственно 4, 6, 8 ... В исходном состоянии диоды I проводят ток от источника смещения через соответствующие резисторы 3, на выходах логических элементов 7 потенциал логической единицы, конденсаторы 10 разряжены, на тине 15 потенциал логической единицы. Входные сигналы, подаваемые на шины 14 запирают в любых комбинациях диоды 1. Это приводит к переключению тока от источника смещения через резистор 3 в цепь соответствующего диода 2. Предположим, что на входы многопорогового элемента подан двоичный код, содержащий две единицы. В этом случае ток от источника смещения через резисторы 3 переключится в цепь двух диодов 2, что приведет к срабатыванию олнопорогового дибкоиминатора с порогом, равным двум. При этом потенциал его выхода становится равным нулю, и связанный с ним конденсатор 10 через резистор 12 начинает заряжаться от источника питания. В момент начала заряда конденсатора 10 потенциал нулевого входа R-S триггера становится равным нулю и по мере заряда конденсатора возрастает до уровня логической единицы. Через время t, равное времени переходных процессов в элементах 7 и времени RC-цепи резисторов 12 и конденсаторов 10, на вход 13 подается стробнруюший импульс, увеличивающий число единиц на входах многопорогового элемента на одну. Так как теперь на входе многопорогового логического элемента будет присутствовать три единицы, то больше не срабатывает ни один однопороговый дискриминатор, и на шине .15 МногопорогоБого элемента сохранится потенциал логической единицы, свидетельствующий о том, что число единиц в контролируемом коде четно. Если на вход многопорогового логического элемента поступит двоичный код, содержащий нечетное число единиц (например 5), то после подачи стробирующего импульса срабатывает однопороговый дискриминатор с порогом, равным шести. При этом конденсатор 10, связан ный с выходом срабатывающего дискриминатора на элементе И-НЕ 7 начинает заряжаться, что приводит к понижению потенциала нулевого входа триггера и его переключению в нулевое состояние. На шине 15, связанной. с единичным выходом R-S триггера, устанавливается потенциал логического нуля, свидетельствующий о нечетном числе единиц в контролируемом коде. Формула изобретения Многопороговый логический элемент четности, содержащий линейный сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к источнику смещения и к анодам соответствующих разделительных диодов, катоды которых соединены с входом резисторного делителя, выходы которого соединены с первыми входами соответствующих элементов И-НЕ, и R-S триггер, выполненный на двух элемейтах И-НЕ, отличающийся тел, что, с целью повышения быстроде-йствия, в иего введены разделительные конденсаторы и резисторы,вторые входы элементов И-НЕ через резистор подключены к положительной щине питания, нулевой вход R-S триггера через разделительные конденсаторы соединен с выходами элементов И-НЕ и через резистор - с положительной шиной питания, единичный вход R-S триггера подключен к одному из входов линейного сумматора и к шине стробирующего сигиа5

ла. единичный выход R-S триггера подключен к выходной шине устройства.

Источники информации, принятые во внимание при экспертизе:

.)4,

Ти л т

м-г-л-1-4 4 п г

608266

Авторы

Даты

1978-05-25—Публикация

1976-07-06—Подача