(54) МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1979 |

|

SU790341A1 |

| Многопороговый логический элемент | 1985 |

|

SU1272499A2 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2000 |

|

RU2189110C2 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент четности | 1976 |

|

SU608266A1 |

| Многопороговый логический элемент | 1984 |

|

SU1223359A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

1

Изобретение относится к автоматике и вычислительной технике, в частности к пороговым логическим элементам.

Как известно, использование элементов пороговой логики в цифровых схемах приводит к существенной экономии оборудования, необходимого для технической реализации того или иного устройства. Существуют многопороговые логические элементы, легко реализуемые в интегральном исполнении, содержащие линейный сумматор, выполненный на резисторах, управляемый входными диодами, многопороговый дискриминатор 1.

Недостатком известных многопороговых логических элементов является то, что их быстродействие определяется числом последовательно включенных однопороговых дискриминаторов и, в общем случае, тем ниже, чем от больщего числа переменных реализуется многопороговая функция. С другой стор0(ны, использование в цифровом устpoйctвe многопороговых элементов, реализующих функции различного числа переменных, требует наличия в нем синхронизирующих сигналов, поскольку быстродействие устройства будет определяться многопороговым элементом с наибольщим числом последовательно включенных однопороговых дискриминаторов.

Наиболее близким по технической сущности к предлагаемому является многопороговый элемент четности, содержащий линейный сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к источнику смещения и к анодам соответствующих разделительных диодов, катоды которых соединены со входом резисторного делителя, выходы которого соединены с первыми входами соответствующих элементов И-НЕ, образующих однопороговые дискриминаторы 2.

Недостатком многопорогового логического элемента четности является наличие конденсаторов, изготовление которых сопряжено с определенными трудностями при использовании интегральной технологии. Кроме того, известный элемент может реализовать только функцию четности.

Цель изобретения - повыщение технологичности и расщирение функциональных возможностей.

Цель достигается тем, что в многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных

диодов, аноды которых через соответствующие резисторы подключены к полюсу источника смещения и к анодам соответствующих разделительных диодов, катоды которых соединены со входом резисторного делителя, выходы которого соединены с первыми входами соответствующих элементов И-НЕ, образующих однопороговые дискриминаторы, введен многовходовой логический элемент И-НЕ, выход которого подключен к выходной клемме многопорогового логического элемента, а входы соединены с выходами нечетных однопороговых дискриминаторов, второй вход каждого из которых подключен к выходу соответствующего четного однопорогового дискриминатора с ближайщим больщим порогом срабатывания; вторые входы четных однопороговых дискриминаторов подключены к положительному полюсу источника питания.

Изменения в схеме многопорогового логического элемента и обеспечивают независимость быстродействия от числа однопороговых дискриминаторов.

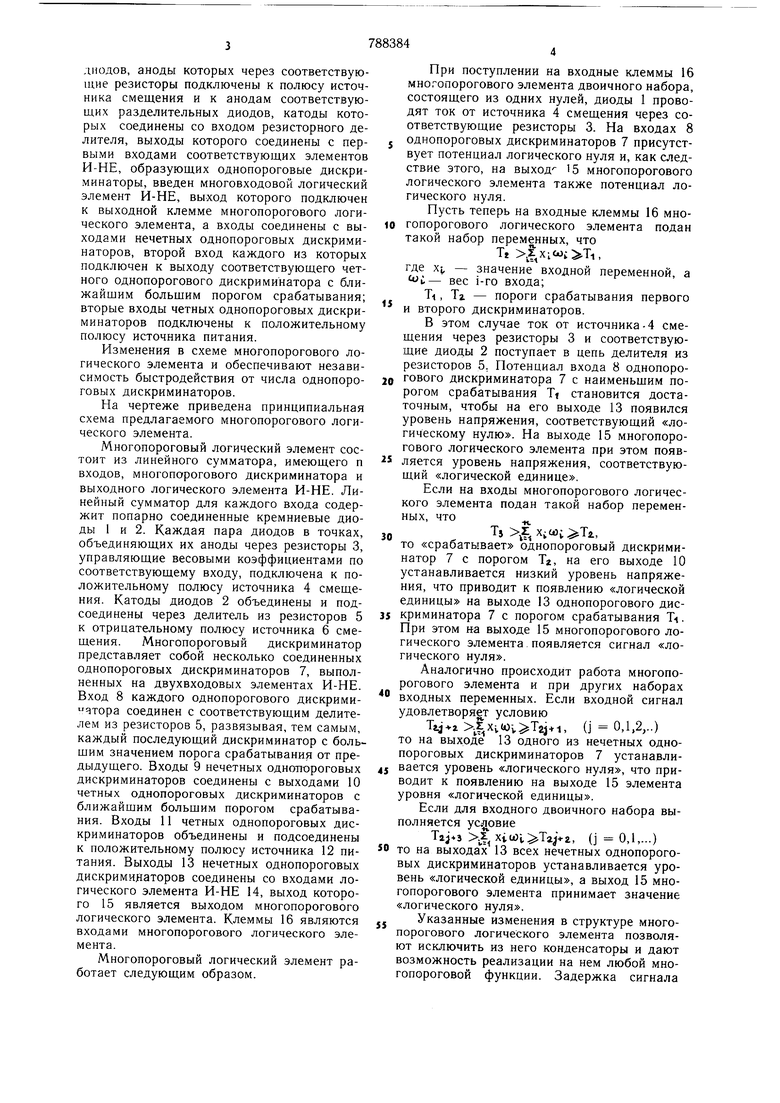

На чертеже приведена принципиальная схема предлагаемого многопорогового логического элемента.

Многопороговый логический элемент состоит из линейного сумматора, имеющего п входов, многопорогового дискриминатора и выходного логического элемента И-НЕ. Линейный сумматор для каждого входа содержит попарно соединенные кремниевые диоды 1 и 2. Каждая пара диодов в точках, объединяющих их аноды через резисторы 3, управляющие весовыми коэффициентами по соответствующему входу, подключена к положительному полюсу источника 4 смещения. Катоды диодов 2 объединены и подсоединены через делитель из резисторов 5 к отрицательному полюсу источника 6 смещения. Многопороговый дискриминатор представляет собой несколько соединенных однопороговых дискриминаторов 7, выполненных на двухвходовых элементах И-НЕ. Вход 8 каждого однопорогового дискрими атора соединен с соответствующим делителем из резисторов 5, развязывая, тем самым, каждый последующий дискриминатор с большим значением порога срабатывания от предыдущего. Входы 9 нечетных однотгороговых дискриминаторов соединены с выходами 10 четных однопороговых дискриминаторов с ближайщим большим порогом срабатывания. Входы 11 четных однопороговых дискриминаторов объединены и подсоединены к положительному полюсу источника 12 питания. Выходы 13 нечетных однопороговых дискриминаторов соединены со входами логического элемента И-НЕ 14, выход которого 15 является выходом многопорогового логического элемента. Клеммы 16 являются входами многопорогового логического элемента.

Многопороговый логический элемент работает следующим образом.

При поступлении на входные клеммы 16 многопорогового элемента двоичного набора, состоящего из одних нулей, диоды 1 проводят ток от источника 4 смещения через соответствующие резисторы 3. На входах 8 однопороговых дискриминаторов 7 присутствует потенциал логического нуля и, как следствие этого, на выходу 15 многопорогового логического элемента также потенциал логического нуля.

Пусть теперь на входные клеммы 16 многопорогового логического элемента подан такой набор переменных, что Т | xico; Ti,

где Xj, - значение входной переменной, а вес i-ro входа;

TI , Та - пороги срабатывания первого и второго дискриминаторов.

В этом случае ток от источника-4 смещения через резисторы 3 и соответствующие диоды 2 поступает в цепь делителя из резисторов 5, Потенциал входа 8 однопорогового дискриминатора 7 с наименьшим порогом срабатывания Tf становится достаточным, чтобы на его выходе 13 появился уровень напряжения, соответствующий «логическому нулю. На выходе 15 многопорогового логического элемента при этом появS ляется уровень напряжения, соответствующий «логической единице.

Если на входы многопорогового логического элемента подан такой набор переменных, что

TS ,, XiOJOTi,

то «срабатывает однопороговый дискриминатор 7 с порогом Тг, на его выходе 10 устанавливается низкий уровень напряжения, что приводит к появлению «логической единицы на выходе 13 однопорогового дискриминатора 7 с порогом срабатывания Тл. При этом на выходе 15 многопорогового логического элемента появляется сигнал «логического нуля.

Аналогично происходит работа многопорогового элемента и при других наборах

входных переменных. Если входной сигнал удовлетворяет условию

|xvWv Taj+i, (j 0,1.2,..) то на выходе 13 одного из нечетных однопороговых дискриминаторов 7 устанавливается уровень «логического нуля, что приводит к появлению на выходе 15 элемента уровня «логической единицы.

Если для входного двоичного набора выполняется условие

| xiu)t Ta|+2, (j 0,1,...)

o то на выходах 13 всех нечетных однопороговых дискриминаторов устанавливается уровень «логической единицы, а выход 15 многопорогового элемента принимает значение «логического нуля.

Указанные изменения в структуре многопорогового логического элемента позволяют исключить из него конденсаторы и дают возможность реализации на нем любой многопороговой функции. Задержка сигнала

для данного многопорогового логического элемента постоянна и не зависит от вида реализуемой функции (от числа входных переменных).

Формула изобретения

Многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к полюсу источника смещения и к анодам соответствующих разделительных диодов, катоды которых соединены со входом резисторного делителя, выходы которого соединены с первыми входами соответствующих элементов И-НЕ, образующих однопороговые дискриминаторы, отличающийся тем, что, с целью повыщения технологичности и

М.

- Й

5ПЛ

расщирения фуикциональных возможностей, в него введен многовходовой логический элемеит И-НЕ, выход которого подключен к выходной клемме многопорогового логического элемента, а входы соединены с выходами

нечетных однопороговых дискриминаторов, второй вход каждого из которых подключен к выходу соответствующего четного однопорогового дискриминатора с ближайщим большим порогом срабатывания; вторые входы четных одопороговых дискриминаторов

подключены к положительному полюсу источника питания.

Источники информации, принятые ВОвнимание при экспертизе

1Авторское свидетельство СССР № 538490, кл. Н 03 К 19/12, 1977.

2Авторское свидетельство СССР № 608266, кл. Н 03 К 19/42, 1978.

Авторы

Даты

1980-12-15—Публикация

1979-01-25—Подача