мента И первой дополнительной группы, а его другой входподключен к выходу соответствующего элемента ИЛИ дополнительной группы, выход данного триггера подключен к первым в.ходам элементов И второй дополнительной группы соответствующего разряда, вторые входы соответствующих элементов И второй дополнительной группы каждого разряда соединены с выходом соответствующих элементов И третьей дополнительной группы, входы каждого элемента И третьей дополнительной группы подключены к выходам соответствунлцего разряда второго, регистра сдвига и элемента НЕ первой группы, выход каждого элемента И второй дополнительный группы подключен к входу соответствующего триггера второй группы, к одному входу соответствующих элементов ИЛИ дополнительной группы через соответствукядий элемент НЕ второй группы подключены третьи входы соответствующих элементов И первой дополнительной группы, а к другим входам соответствующих элементов ИЛИ дополнительной группы подключены выходы триггера второй группы, выходы элементов ИЛИ дополЪительной группы подключены к входам первого элемента И, выход которого соединен с входом первого триггера, один выход первого триггера подключе к одному входу второго элемента И, второй вход которого соединен с выходом первого формирователя одиночных импульсов, выход второго элемента И подключен к перв№1 входам двух регистров сдвига и к входу второго тригера, выход которого подключен к одному входу третьего элемента И, а другой вход соединен с генератором тактовых импульсов, выход третьего элемента И подключен к одним входам четвертого и пятого элементов И, выходы которых подключены к вторым

входам соответственно первого и второго регистров сдвига, выход четвертого элемента И подключен к входу первого счетчика, информационные выходы которого подключены к входам дешифратора, выход которого подключен к управляющему входу элемента сравнения, информационные входы которого подключены к соответствующим выходам второго и третьего счетчиков .входы которых подключены к старшему разряду соответственно первого и второго регистров сдвига,.выходэлемента сравнения подключен к входу второго формирователя одиночных импульсов, к входу третьего триггера и к одному входу первого элемента ИЛИ, другой вход которого соединен с выходом второго элемента ИЛИ, входы данного элемента ИЛИ соединены с выходами элементов И второй дополнительной группы, выходы элементов И первой дополнительной группы подключены к входам третьего элемента ИЛИ, выход которого подключен к одному входу четвертого триггера и к одному входу пятЬго триггера, другие входы которых соединены с выходом первого элемента ИЛИ, выходы четвертого и пятого триггеров подключены соответственно к другим входам четвертого и пятого элементов И, выход второго формирователя одиночных импульсов подключен к третьим входам двух регистров сдвига, выход третьего триггера подключен к первым входам элементов И первой дополнительной группы, причем вход первого формирователя одиночных импульсов является входом блока подключения корректирующих разрядов, выходами первой группы которого являются выходы элементов НЕ второй группы, выходами второй группы - выходы триггеров второй группы, а выходом - другой выход первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с частичным резервированием | 1986 |

|

SU1434503A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Запоминающее устройство с коррекцией информации | 1980 |

|

SU907587A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Схема управления жидкокристаллическим экраном | 1988 |

|

SU1695390A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

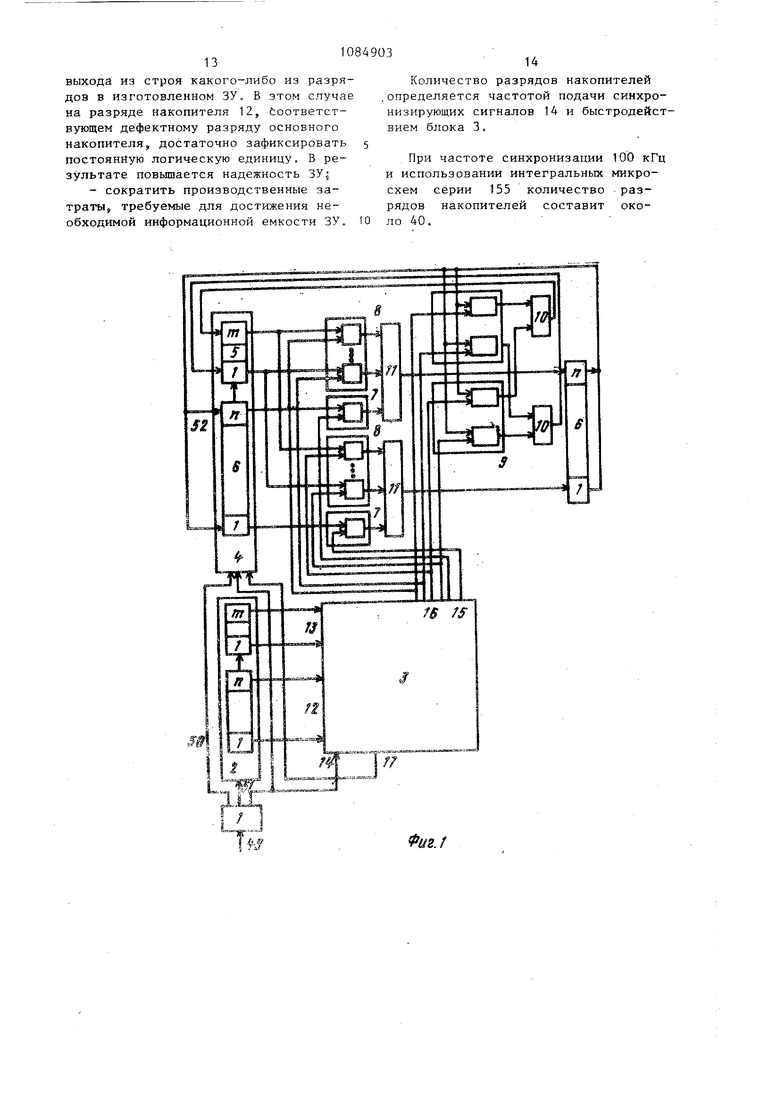

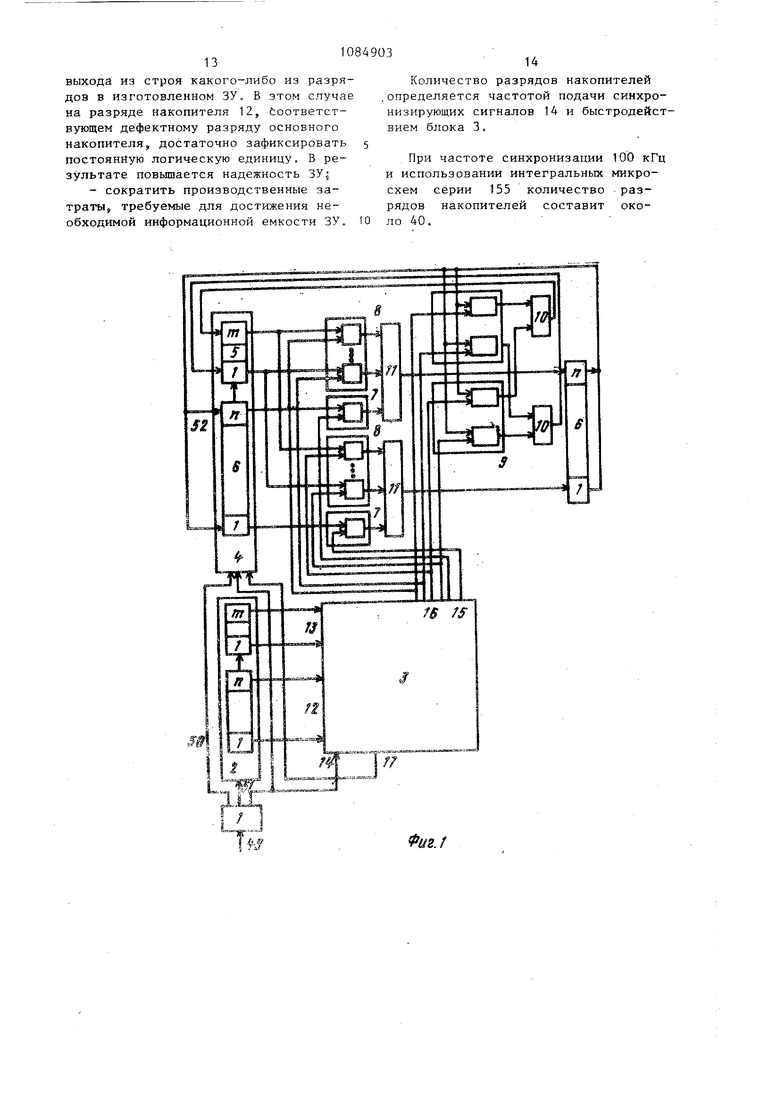

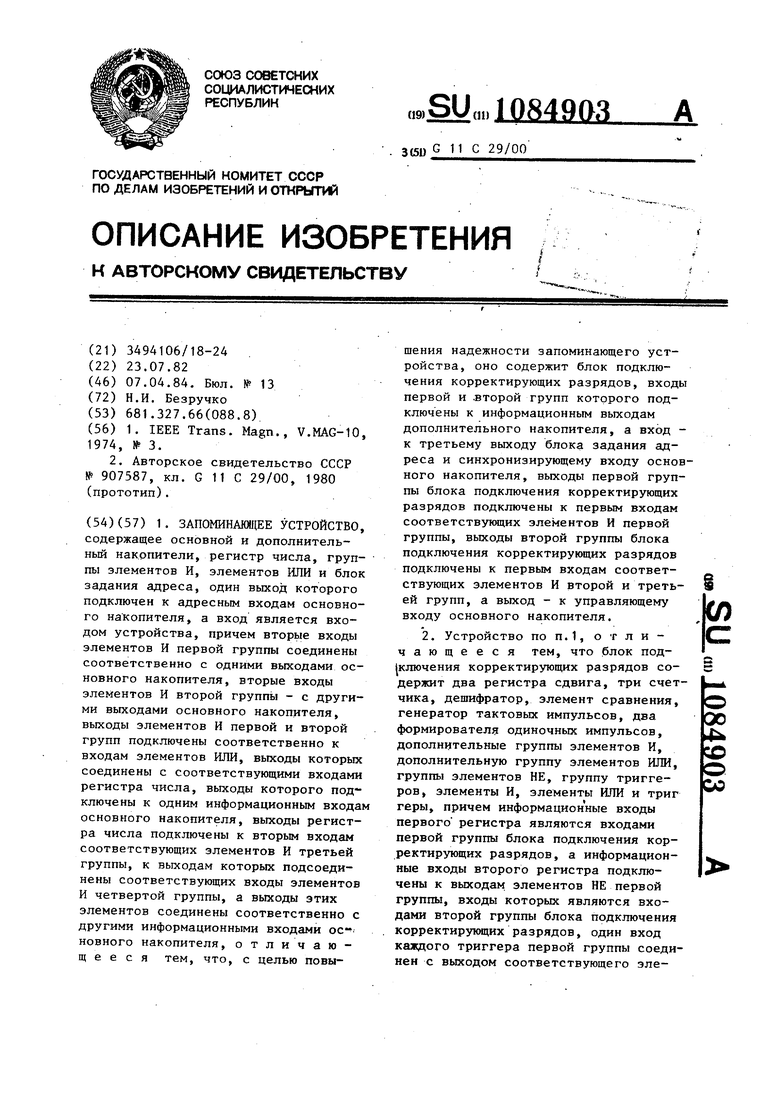

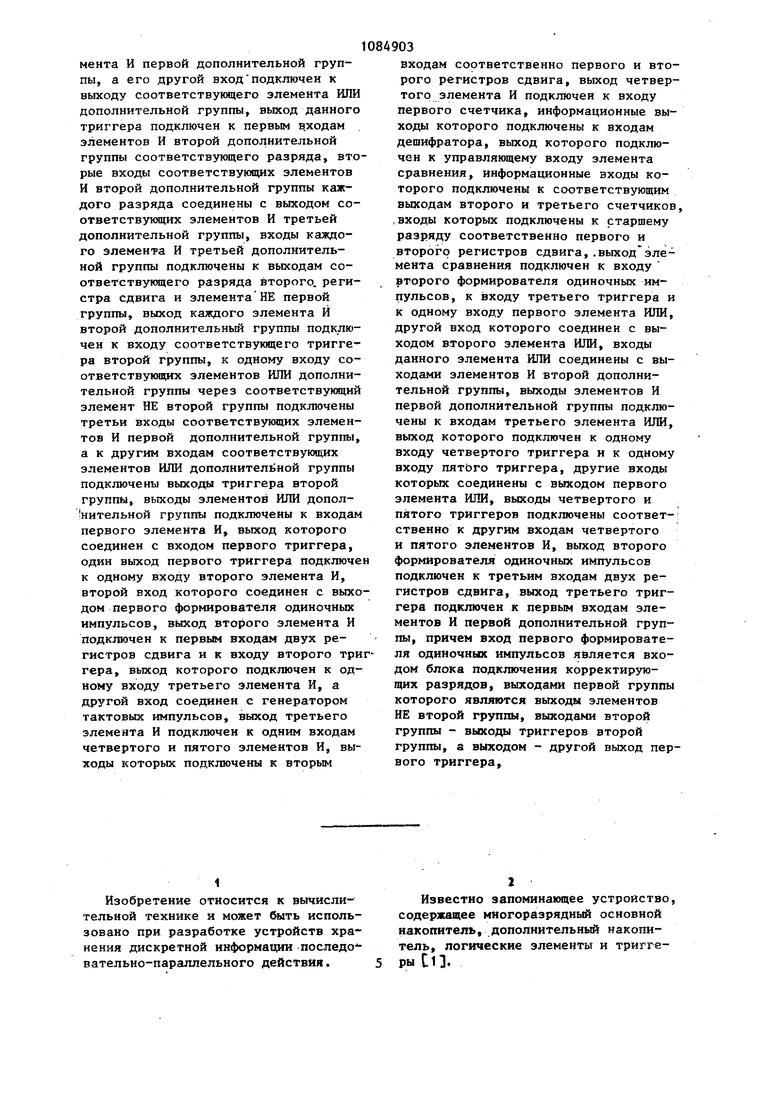

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее основной и дополнительный накопители, регистр числа, группы элементов И, элементов ИЛИ и блок задания адреса, один выход которого подключен к адресным входам основного накопителя, а вход является входом устройства, причем вторые входы элементов И первой группы соединены соответственно с одними выходами основного накопителя, вторые входы элементов И второй группы - с другими выходами основного накопителя, выходы элементов И первой и второй групп подключены соответственно к входам элементов ИЛИ, выходы которых соединены с соответствующими входами регистра числа, выходы которого подключены к одним информационным входам основного накопителя, выходы регистра числа подключены к вторым входам соответствующих элементов И третьей группы, к выходам которых подсоединены соответствующих входы элементов И четвертой группы, а выходы этих элементов соединены соответственно с другими информационными входами основного накопителя, отличающееся тем, что, с целью повышения надежности запоминающего устройства, оно содержит блок подключения корректирующих разрядов, входы первой и .второй групп которого подключены к информационным выходам дополнительного накопителя, а вход к третьему выходу блока задания адреса и синхронизирующему входу основного накопителя, выходы первой группы блока подключения корректирующих разрядов подключены к первым входам соответствующих элементов И первой группы, выходы второй группы блока подключения корректирующих разрядов подключены к первым входам соответствующих элементов И второй и треть9 ей групп, а выход - к управляющему входу основного накопителя. 2. Устройство по П.1, отличающееся тем, что блок под|ключения корректирующих разрядов содержит два регистра сдвига, три счетчика, дешифратор, элемент сравнения, 00 генератор тактовых импульсов, два формирователя одиночных импульсов, дополнительные группы элементов И, со дополнительную группу элементов ИЛИ, о со группы элементов НЕ, группу триггеров, элементы И, элементы ИЛИ и триг геры, причем информационные входы первого регистра являются входами первой группы блока подключения корректирующих разрядов, а информационные входы второго регистра подключены к выходам элементов НЕ первой группы, входы которых являются входами второй группы блока подключения корректирующих разрядов, один вход каждого триггера первой группы соединен с выходом соответствующего эле

1

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств хранения дискретной информации последо вательно-параллельного действия.

Известно запоминающее устройство, содержащее многоразрядный основной накопитель, дополнительный накопитель, логические элементы и триггеры Г.1. В этом запоминающем устройстве дополнительный накопитель является маркировочным и служит для хранения адресов неисправных слов основного накопителя с целью дальнейшей блоки ровки их использования. При этом в технологическом цикле изготовления ЗУ, для получения его оптимальной информационной емкости, необходимо предусматривать сортировочные операции позиционного размещения устройств памяти в разрядах основного накопителя в соответствии с числом и местом расположения неисправных элементов в каждом из них. Недостатком устройства является то, что сортировочные операции значительно удлиняют технологический цикл изготовления ЗУ и увеличивают стоимость. Кроме того, недостатком является отсутствие автоматической блокировки информации. Это ведет к тому, что замена в разрядах основного накопителя любого из блоков памяти требует нового их размещения, замены дополнительного накопителя, что крайне сложно производить в изготов ленном образце ЗУ. Наиболее близким техническим решением к изобретению является запоминающее устройство с коррекцией информации, содержащее основной и дополнительный накопители, регистр числа, группы элементов И, элементо ИЛИ и блок адреса, один вькод котор го подключен к адресным входам осно ного накопителя, другой выход - к адресным входам дополнительного накопителя, а вход является входом устройства, причем вторые входы эле ментов И первой группы соединены со ответственно с одними из выходов ос новного накопителя, вторые входы эл ментов И второй группы - с другими выходами основного накопителя, выхх) ды элементов И первой и второй груп подключены соответственно к входам элементов ИЛИ, выходы которых подключены соответственно к входам регистра числа, выходы которого подкл чены к одним из информационных входов основного накопителя. Кроме тог выходы регистра числа подключены к вторым входам соответствующих элеме тов И третьей группы, к выходам которых подсоединены соответствующие входы элементов И четвертой группы. а выходы этих элементов соединены соответственно с другими информацион ными входами основного накопителя 2. . В известном устройстве используется еще один дополнительный накопитель для хранения номеров неисправных разрядов, который управляет работой элементов И первых трех групп. Недостатком известного устройства является то, что замена любого вышедшего из строя разряда основного накопителя или введение дополнительного разряда требует замены- дополнительного накопителя для хранения номеров неисправных разрядов, а отсутствие автоматической коррекции информации в неисправных разрядах основного накопителя снижает надежность запоминающего устройства. Целью изобретения является повышение надежности запоминающего устройства. Поставленная цель достигается тем что запоминающее устройство, содержащее основной и дополнительный накопители, регистр числа, группы элементов И, элементов ИЛИ и блок задания адреса, один выход которого подключен к адресным входам основного накопителя, а вход является входом устройства, причем вторые входы элементов И первой группы соединены соответственно с одними выходами основного накопителя, вторые входы элементов И второй группы - с другими выходами основного накопителя, выходы элементов И первой и второй групп подключены соответственно к входам элементов ИЛИ, выходы которых соединены с соответствующими входами регистра числа, выходы которого подключены к одним информационным входам основного накопителя, выходы регистра числа подключены к вторым входам соответствующих элементов И третьей группы, к выходам которык подсоединены соответствующие входы элементов И четвертой группы, а выходы этих элементов соединены соответственно с другими информационньми входами основного накопителя, содержит блок подключения корректирующих раз-рядов, входы первой и второй групп которого подключены к информационным выходам дополнительного накопителя, а вход - к третьему выходу блока задания сщреса и синхронизирующему входу основного накопителя, выходы первой группы блока подключения корректирующих разрядов подключены к первым входам соответствукицих элементов И первой группы, выходы второй группы блока подключения корректирующих разрядов подключены к первым входам соответствующих элементов И второй и третьей групп, а вых.од к управляющему входу основного накопителя . Кроме того, блок подключения корректирующих разрядов содержит два ре гистра сдвига, три счетчикаJ дешифратор, элемент сравнения, генератор тактовых импульсов, два формироватё,ля одиночных импульсов, дополнительные группы элементов И, дополнительную группу элементов ИЛИ, группы элементов НЕ, группу триггеров, элементы И, элементы ИЛИ и триггеры, причем информационные входы первого регистра являются входами первой группы блока подключения корректирую щих разрядов, а информационные входы второго регистра подключены к выходам элементов НЕ первой группы, входы которых являются входами второй группы блока подключения корректирую ших разрядов, один вход каждого три гера первой группы соединен с выходом соответствующего элемента И первой дополнительной группы, а его другой вход подключен к выходу соответствующего элемента ИЛИ дополнительной группы, выход данного тригге ра подключен к первым входам элементов И второй дополнительной группы соответствующего разряда, вторые входы соответствующих элементов И второй дополнительной группы каждого разряда соединены с выходом соответствующих элементов и третьей дополнительной группы входы каждого элемента И третьей дополнительной группы подключены к выходам соответствующего разряда второго регистра сдвина и элемента НЕ первой группьг, выход кажсдого элемента И второй до-полнительной группы подключен к вкоду соответствующего триггера второй -группы, к одному входу соответствующих -элементов ИЛИ дополнительной группы через соответствукиций элемент НЕ второй группы подключены третьи входы соответствующих элементов И первой дополнительной группы, а к другим входам соответствующих 03 6 элементов ИЛИ дополнительной группы подключены выходы триггеров второй группы, выходы элементов ИПИ дополнительной группы подключены к входам первого элемента И, выход которого соединен с входом первого триггера, один выход первого триггера подключен к одному входу второго элемента И, второй вход которого соединен с вьгходом первого формирователя одиночных импульсов, выход второго элемента И подключен к первым входам двух регистрюБ сдвига и к входу второго. триггера, выход которого подключен к одному входу третьего элемента И, а другой вход соединен с генератором тактовых импульсов, выход третьего элемента И подключен к одним входам четвертого и пятого элементов И, выходы которых подключены к вторым входам соответственно первого и второго регистров сдвига, выход четвертого элемента И подключен к входу первого счетчика, информационные выходы которого подключены к входам дешифратора. выход которого подключен к управляющему входу элемента сравнения, информационные входы которого подключены к соответствующим выходам второго и третьего счетчиков, входы которых подключены к старшему разряду соответственно первого и второго регистров сдвига, выход элемента сравнения подключен к входу второго формирователя одиночных импульсов, к входу третьего триггера и к одному входу (первого элемента ИЛИ, другой вход которого соединен с выходом второго элемента. ИЛИ, вкоды данного элемента ИЛИ соединены с выходами элементов И второй дополнительной группы, выходы элементов и первой дополнительной группы подключены к входам третьего элемента ШМ выход которого подклю-чен к одному входу четвертого триггера и к одному входу пятого триггера, другие входы которык соеднкены с выходом первого элемента ИЛИ, выходы четвертого и пятого триггеров подкгаочены соответственно к другим входам четвертого и пятого элементов И, выход .йторс-.-э формирователя одиночных импульсов подключен к третьим входам двух регистров сдвига, вьпсод третьего триггера подключен к первым входам элемемтов И первой дополнительной группы, причём вход первого фсрм; рсвателя одиночных импульсов является входом блока подключения корректирующих разрядов, выходами первой групп которого являются выходы элементов НЕ второй группы, выходами второй группы - выходы триггеров второй группы, а. выходом - другой выход пе вого триггера. На фиг. 1 изображена блок-схема предложенного запоминающего устройс ва; на фиг. 2 - функциональная схема блока автоматического подключени корректирующих разрядов. Запоминающее устройство содержит блок 1 задания адреса, дополяительньй накопитель (ДП) 2, блок 3 подключения корректируюощх разрядов (ПК), основной накопитель 4, состоя щий из (n+m) разрядов, где m разрядов 5 корректирующие, регистр 6 чис ла, первую 7, вторую 8, третью 9, четвертую 10 группы элементов И и группу элементов ИЛИ 11. Первые 12 и вторые 13 входы блока 3 подключены к информационным вы ходам ДП 2, а третий вход 14 - к третьему выходу блока 1 задания и к синхронизирующему входу основного накопителя. Первые 15 выходы блока подключены к первым входам первой группы элементов И 7, вторые 16 выходы подключены к ие-рвътм входам соо ветствующих элементов И второй 8 и третьей 9 групп, а третий выход 17 - к управляющему входу основного накопителя 4, за счет чего разрешается вьщача. информации из накопителя 4 в регистр 6 числа или запись в накопитель 4. В каждом разряде основного накопителя 4 расположен блок памяти с последовательным вводом-выводом дан ных, номера неисправных элементов в соответствующих которых записаны разрядах ДП 2. ДП 2 может быть реализован на программируемых полупроводниковых микросхемах. Блок 3 подключения корректирующих разрядов содержит первый 18, второй 19 регистры сдвига, первый 20, второй 21, третий 22 счетчики, дешифратор 23, элемент 24 сравнения, генератор 25 тактовых импульсов, первый 26, второй 27 формирователи оди ночных импульсов, первую 28, вторую 29, третью 30 дополнительные.группы элементов И, первый 31, второй 32, третий 33, четвертый 34, пятый 35 элементы И, дополнительную группу 38 элементов ИЛИ 36, первый 37, второй 38, третий 39 элементы ИЛИ, первую 40, вторую 41 группы элементов НЕ, первую 42, вторую 43 группы триггеров, первый 44, второй 45, третий 46, четвертый 47, пятьй 48 триггеры. Первые 12 входы блока 3 подключены к информационным Ьходам первого регистра 18 сдвига, к входам соответствующих элементов НЕ 41 и третьим входам соответствующих элементов И 28, Вторые 13 входы подключены через инверторы 40 к информационным входам второго регистра 19 сдвига, а третий 14 вход - к входу формирователя 26 одиночных импульсов, Один вход триггера 42 соединен с выходом соответствующего элемента И 28, а его другой вход подключен к выходу соответствующего элемента ИЛИ 36. Выход триггера 42 подключен к первым входам всех элементов И 29 в каждом разряде. Вторые входы соответствующих элементов И 29 каждого разряда соединены с выходом соответствующих элементов И 30, входы которых подключены к выходам соответствующих элементов НЕ 40 и регистра 19 сдвига. Выход элементов И 29 подключен к входу соответствующих триггеров 43, выходы которых в каждой группе подключены к одним входам элементов ИЛИ 36, к другому входу которых подключен выход элемента НЕ 41. Выходы элементов ИЛИ 36 подключены к входам элемента И 31, выход которого соединен с входом триггера 44. Один выход триггера 44 подключен к одному входу элемента И 32, второй вход которого соединен с формирователем 26 одиночных импульсов. Выход элемента И 32 подключен к первым входам регистров 18 и 19 сдвига и к входу триггера 45, выход которого подключен к одному входу элемента И 33, а другой вход - к выходу генератора 25 тактовых импульсов. Выход элемента И 33 подключен к одним входам элементов И 34 и И 35, к другим входам которых подключены выходы соответственно триггеров 47 и 48. Выходы элементов И J4 и И 35 подключены к вторым входам соответстkeiTHo регистров 18 и 19 сдвига. Кроме того, выход элемента И 34 подключен К входу счетчика 20, информационные выходы которого подключены к входам дешифратора 23. Выход дешифратора 23 подключен к управляющему входу элемента 24 сравнения, информационные входы которого подключены к соответствующим выходам счетчиков 21 и 22, а выходы данных счетчиков подключены к последнему разряду соответственно регистров 18 и 19 сдвига Выход элемента 24 сравнения подключен к входу формирователя 27 одиночных импульсов, к входу триггера 46 и к одному входу элемента ИЛИ 37, другой вход которого соединен с выходом элемента ИЛИ 38, Входы элемента ИЛИ 38 соединены с выходами элементов И 295 а выходы элементов И 28 подключены к входам элемента ИЛИ 39, выход которого подключен к одному входу триггера. 47 и одному входу триггера 48, другие входы кото рых подключены к выходу элемента ИЛИ 37. Выход формирователя 27 одиночных импульсов подключен к третьим входам регистров 18 и 19 сдвига, выход триггера 46 - к первым входам элементов И 28, Первые 15 вьжоды блока 3 подключе ны к соответствующим выходам группы элементов НЕ 41, вторые 16 выходы к соответствующим выходам группы триггеров 43, а третий 17 выход - к другому выходу триггера 44 о В блоке 3 используется элемент 24 сравнения, который реализует функцию нестрогого (/) неравенства по информации двух счетчиков 21 и 22. Запоминающее устройство работает следующим образом. Перед выборкой очередного слова все исполнительные -элементы блока 3 сброшены в исходное состояние (на чертежах шина управления сбросом не показана), По адресу 49 и по птине 50 выбирается страница памяти в оснозном накопителе 4, а путем подачи из блока задания адреса синхронизирующего сигнала по шине 14 производится последовательное считывание (запись) многоразрядных слов из (в) вы ранной страницы. По синхронизирующему сигналу 14 производится также блоком адреса перебор адресов допол нительного накопителя 2 шинами 51. Если все элементы памяти очередного слова основного накопителя 4 исправ ные, то сигналы с дополнительного накопителя 2, в котором записан код О, проходя через группу элементов НЕ 41, элементы ИЛИ 36 вызывают срабатывание элемента И 31 который переключает триггер 44, Данный триггер дает разрешение по шине 17 на считывание слова из основного накопителя 4, которое через элементы И 7. ИЛИ 11 записывается в регистр 6 числа. При этом выходной уровень сигнала НЕ 41 разрешает работу элементам И 7 по первому входу. Наличие разрешения по шине 17 требуется также для записи чисел из регистра 6 числа в основной накопитель 4. Запись при наличии кода О в разрядах дополнительного накопителя 2 производится обычным способом по шинам 52, Организацию процесса считывание запись в основной накопитель по сигналу разрешение 17 можно произвестид например, с использованием буферного регистра и шинного формирователя которые на чертежах не показаны. При неисправном элементе памяти в разряде (одном или нескольких) основного накопителя 4 и в соответствующем разряде дополнительного накопителя 2 записана 1. В этом случае элемент И 31 не срабатывает, триггер 44, находясь в исходном состоянии, разрешает работать элементу И 32э через который проходит одиночный импульс, сформированный формирователем 26, Данный формирователь срабатывает с задержкой относительно подачи синхронизирующего сигнала 14, равной суммарной длительности переходньк процессов работы элементов НЕ 41,, ИЛИ 36, И 31 и триггера 44. По сигналу с элемента И 32 записывается информация дополнительного на.копителя 2 в оба регистра 18 и 19 сдвига параллельно во все разряды и перебрасывается триггер 45, тем самьт подключает генератор 25 тактовьпс имщшьсов к регистрам гдгвига через элементы И 33-35 Запоминакядее устройство переходит в режим . В этом ре.жиме генератор 25 сдвигает .информацию о;з.новременно в двух регистрах сдвига. тем самым производится запись единиц с регистров в счетчики 21 к 22, Так как запись в регистр 19 сцв-лга из дополнительного накопите.пя 2 п15О55зводиася через элемент НЕ 40, то le ре зультате сдвига в счетчике 22 храни ся информация о числе исправных элементов m корректирующих разрядов а в счетчике 21 - число неисправных элементов в п разрядах основного на копителя. После сдвига на п тактов (предпо лагается ) регистры 18 и 19 сдви га очи1цаются1 и выходной сигнал де шифратора 23, управляемый счетчиком 20, разрешает работу элемента 24 сравнения, который срабатывает, есл число исправных элементов m разрядов 5 больше или равно числу неисправных элементов п разрядов накопителя 4. В противном случае элемент 24 сравнения не срабатьшает, выбирается второе слово, а первое блокируется блоком управления (не показан). После срабатывания элемента 24 сравнения запоминающее устройство переходит в режим работы подключения корректирующих разрядов. По сигналу с элемента 24 сравнения формирователь 27 записывает единицу одновременно в оба регистра 18 и 19 сдвига, перебрасывается триггер 46, который подает разрешающий уровень на первые входы группы элементов И 28 и через элемент ИЛИ 37 перебрасывается триггер 48. Данный триггер блокирует элементом И 35 входрегистра 19 сдвига от генератора 25 тактовых импульсов. Далее, производят через элементы И 33 и 34 последовательный сдвиг ранее записанной единицы в регистр 18, определяют разряд, в котором хранится неисправный элемент, при этом на выходе соответствующего разряда 12 накопителя 2 находится постоянная единица. В результате последова тельного обращения к каждому разряду, за счет потактного сдвига в регистре 18 единицы, срабатывает соответствующий элемент И 28 и триг гер 42, разрешающий работу по первому входу элементам И 29. После ср батывания элемента И 29 сигнал чере элемент ИЛИ 39 перебрасывает тригге ры 47 и 48, тем самым запрещает через элемент И 34 выдавать тактиру щие импульсы в регистр 18, а разреш ет сдвигать единицу в регистре 19 сдвига. Единица в этом регистре пер писывается поразрядно и при наличии исправных элементов памяти корректи рующих 5 разрядов срабатывают элемент И 30 и соответствующий элемент И 29, который находится в группе, ранее выбранной триггером 42, и соответствующий триггер 43. Кроме того, выходной сигнал элемента И 29 через элемент ИЛИ 38 опять перебрасывает триггер 47 и 48, а в момент срабатывания триггера 43 через элемент ИЛИ 36 сбрасывается соответствукиций триггер 42. Таким образом, потенциальный уровень выходного сигнала триггера 43 подключает соответствующие элементы И 8 и 9 к разрядам основного накопителя 4. При этом, если элемент И 31 не срабатывает, значит имеется еще неисправный элемент памяти, информацию которого необходимо корректировать. Поскольку триггеры 47 и 48 уже переброшены, то это позволяет продолжить сдвиг единицы в регистре 18 сдвига. Далее производится работа аналогично описанной до тех пор, пока не срабатывает элемент И 31 и не перебросится триггер 44. В итоге выходы 16 триггеров 43 за счет элементов И 8 и 9 подключают взамен всех разрядов с неисправными элементами памяти корректирующие разряды с исправньми элементами основного накопителя . После такого подключения разрешающий сигнал 17 позволяет получить скорректированное слово из накопителя 4. Коррекция числа при записи в основной накопитель 4 из регистра 6 числа производится через элементы И 9 и 10, а коррекция числа при считывании - через элементы И 8 и ИЛИ 11. Таким образом, предложенное запоминакидее устройство позволяет автоматически корректировать информацию неисправных элементов основного накопителя во время работы. По числу несрабатываний элемента 24 сравнения в режиме контроля ЗУ определяется требуемая дополнительная емкость основного накопителя. Введение автоматической коррекции в сравнении с прототипом позволяет: -оперативно набрать требуемую недостающую емкость ЗУ за счет добавления (или имеющегося резерва) разрядов основного накопителя; -не заменять дополнительный накопитель при увеличении разрядов основного накопителя, что важно в случае

выхода из строя какого-либо из разрядов в изготовленном ЗУ. В этом случае на разряде накопителя 12, йоответствующем дефектному разряду основного накопителя, достаточно зафиксировать постоянную логическую единицу, В результате повьшзается надежность ЗУ;

сократить производственные заTpaTHj требуемые для достижения необходимой информационной емкости ЗУ. to ло 40.

Количество разрядов накопителей ,определяется частотой подачи синхронизирующих сигналов 14 и быстродействием блока 3.

При частоте синхронизации 100 кГц и использовании интегральных микросхем серии 155 количество разрядов накопителей составит око

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| IEEE Trans | |||

| Magn., V.MAG-10, 1974, № 3 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с коррекцией информации | 1980 |

|

SU907587A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-07—Публикация

1982-07-23—Подача