10

15

20

25

11242962

Изобретение относится к вычислительной технике и может быть использовано для контроля временной диаграммы работы различных блоков управ- л ения и контроллеров.

Цель изобретения - повышение достоверности контроля.

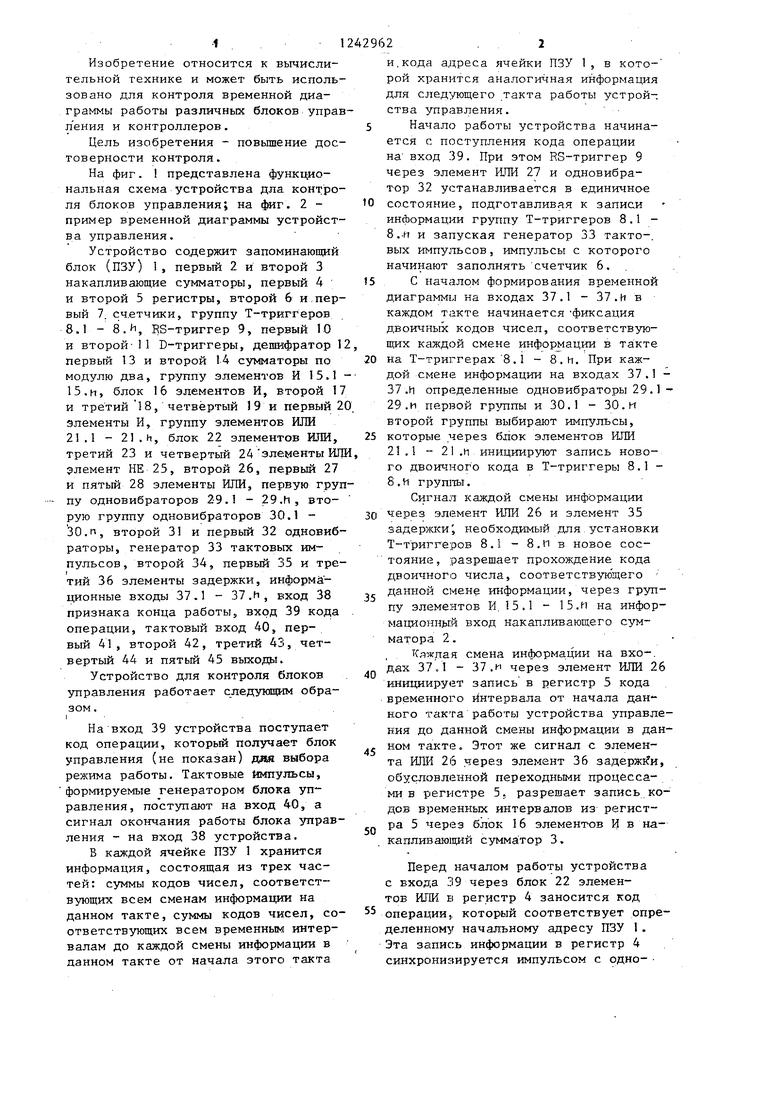

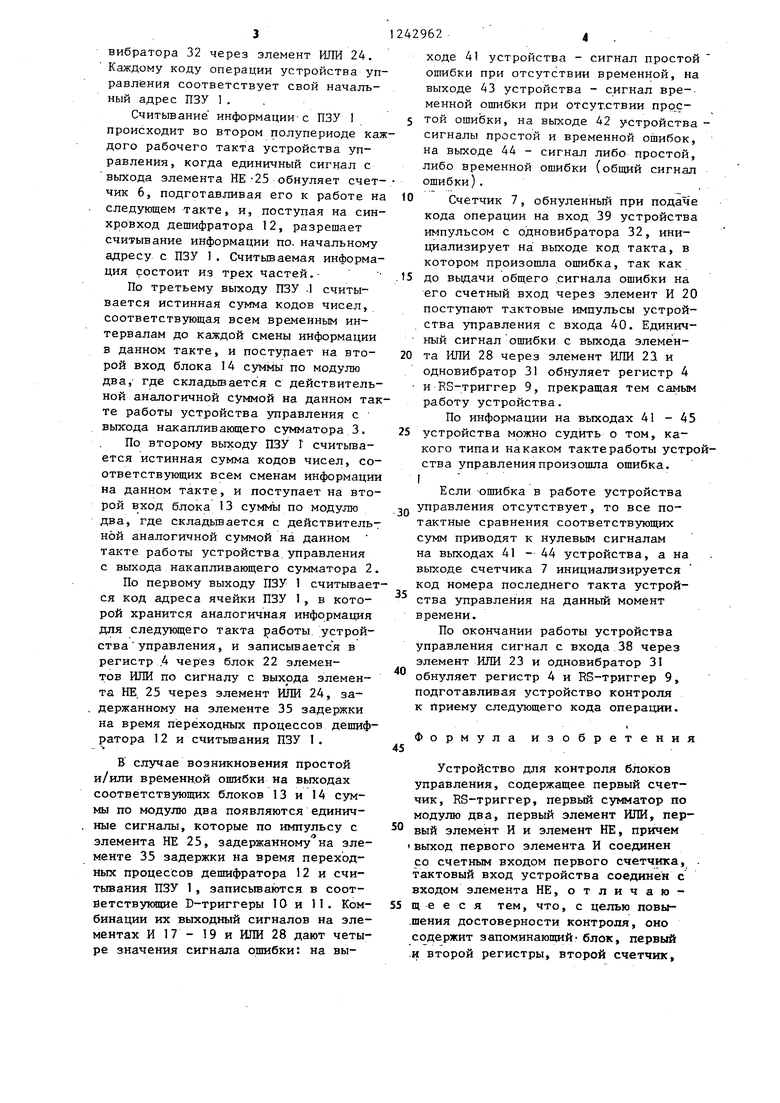

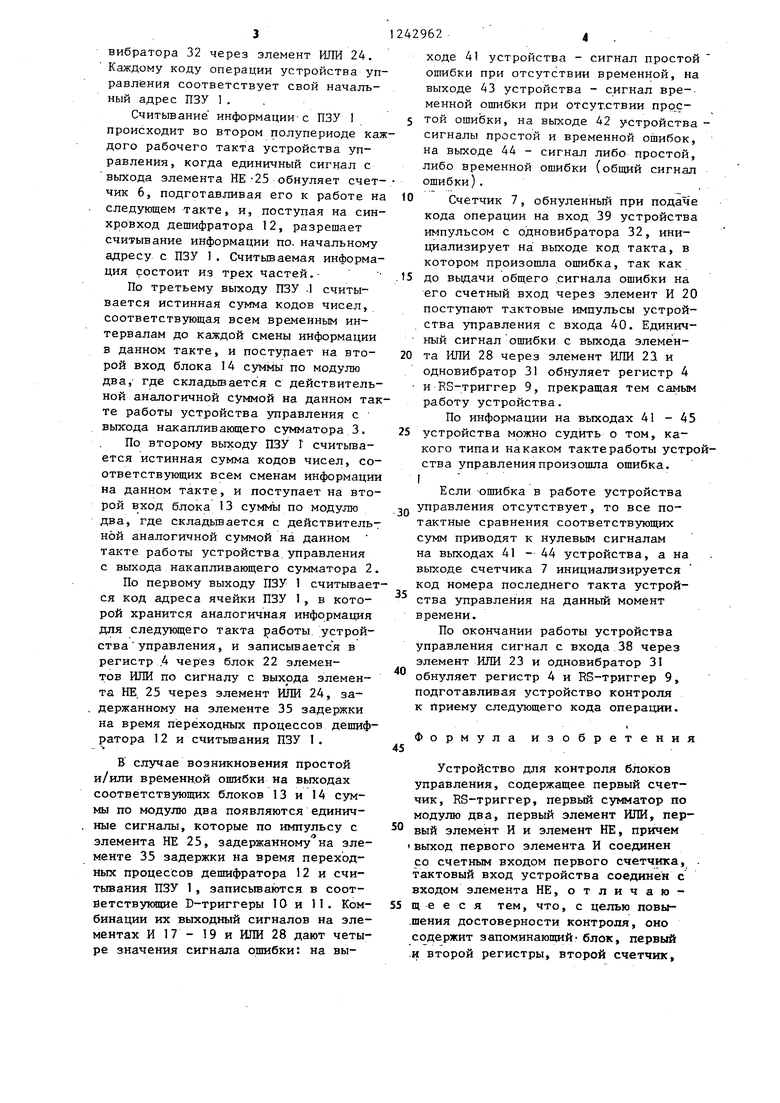

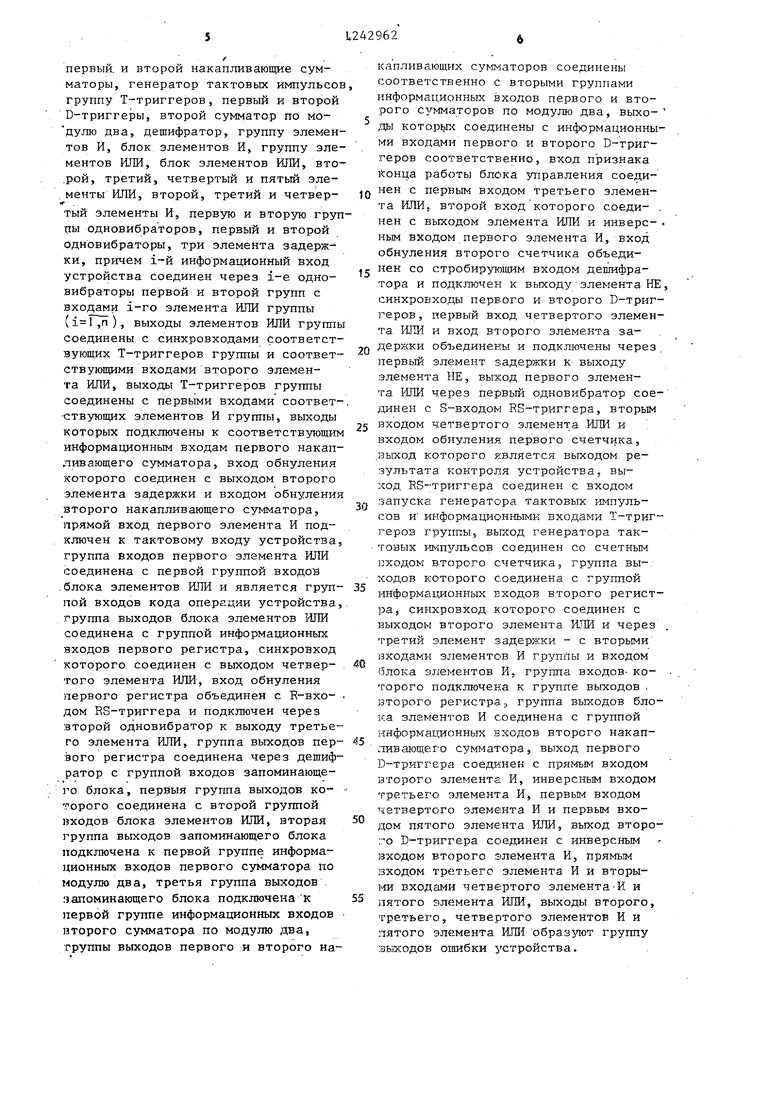

На фиг. 1 представлена функциональная схема устройства дла контроля блоков управления; на фиг. 2 - пример временной диаграммы устройства управления.

Устройство содержит запоминающий блок (ПЗУ) 1, первый 2 и второй 3 накапливающие сумматоры, первый 4 ; и второй 5 регистры, второй 6 и первый 7. сч.етчики, группу Т-триггеров 8.1 - в.Ь, RS-триггер 9, первый 10 и второй- 1 D-триггеры, дешифратор 12, первый 13 и второй 14 сз мматоры по модулю два, группу элементов И 15.1 - 15.и, блок 16 элементов И, второй 17 и третий 18, четвёртый 19 и первый 20, элементы И, группу элементов ИЛИ 21,1 - 21.h, блок 22 элементов ИЛИ, третий 23 и четвертый 24 элементы ИЛИ, элемент НЕ 25, второй 26, первый 27 и пятый 28 элементы ИЛИ, первую группу одновибраторов 2-9.1 - 29.h , вторую группу одновибраторов 30.1 - 30.п, второй 31 и первый 32 одновиб- раторы, генератор 33 тактовых импульсов, второй 34, первый 35 и третий 36 элементы задержки, информационные входы 37.1 - 37.h, вход 38 признака конца работы вход 39 кода операции, тактовый вход 40, первый 41, второй 42, третий 43, четвертый 44 и пятый 45 выходы.

Устройство для контроля блоков управления работает следукшщм образом ., I

На вход 39 устройства поступает код операции, который получает блок управления (не показан) дям выбора режима работы. Тактовые ймпута сы, формируемые генератором блока управления, поступают на вход 40, а сигнал окончания работы блока управления - на вход 38 устройства.

В каждой ячейке ПЗУ 1 хранится информация, состоящая из трех частей: суммы кодов чисел, соответствующих всем сменам информации на данном такте, суммы кодов чисел, соответствующих всем временным интервалам до каждой смены информации в данном такте от начала этого такта

30

35

40

45

50

и с

е н ч т и в н

к н в к г

ч т м м

д ин в н н н т о ми к

с то 55 оп де Эт си

и.кода адреса ячейки ПЗУ 1, в кото- рой хранится аналогичная информация для следующего такта работы устройства управления.

Начало работы устройства начинается с поступления кода операции на вход 39. При этом RS-триггер 9 через элемент РШИ 27 и одновибра- тор 32 устанавливается в единичное состояние, подготавливая к записи информации группу Т-триггеров 8.1 - В..ц и запуская генератор 33 такто-, вых импульсов, импульсы с которого начинают заполнять счетчик 6. .

С началом формирования временной диаграммы на входах 37.1 - 37.(i в каждом такте начинается фиксация двоичных кодов чисел, соответствующих Ксшдой смене информации в на Т-триггерах 8.1 - 8.и. При каждой смене информации на входах 37.1- 37.И определенные одновибраторы 29.1 - 29.и первой грушпы и 30,1 - 30.и второй группы выбирают импульсы, которые через блок элементов ИЛИ 21.1 - 21.и инициируют запись нового двоичного кода в Т-триггеры 8.1 - 8.и грушты.

Сигнал каждой смены информации через элемент ИЛИ 26 и элемент 35 задержки , необходимый для. установки Т-т риггеров 8.1 - 8.и в новое состояние , разрешает прохождение кода двоичного числа, соответствую щего данной смене информации, через группу элементов И. 15.1 - 15.П на информационный вход накапливающего сумматора 2.

смена информации на вхо-. дах 37.1 - 37.и через элемент ИЛИ 26 инициирует запись в регистр 5 кода временного интервала от начала данного такта работы устройства управления до данной смены информации в данном такте. Этот же сигнал с элемента ИШ-1 26 через элемент 36 задерж1 и, обусловленной переходньми процесса- , ми в регистре 5, разрешает запись кодов временных интервалов из регистра 5 через блок 16 элемент-ов И в накапливающий сумма тор 3.

Перед началом работы устройства с входа 39 через блок 22 элементов ИЛИ в регистр 4 заносится код 55 операции, который соответствует определенному начальному адресу ПЗУ 1. Эта запись информации в регистр 4 синхронизируется импульсом с одно-

31

вибратора 32 через элемент ИЛИ 24. Каждому коду операции устройства управления соответствует свой начальный адрес ПЗУ 1.

Считывание информации с ПЗУ 1 происходит во втором полупериоде каждого рабочего такта устройства управления, когда единичный сигнал с выхода элемента НЕ-25 обнуляет счет- чик 6, подготавливая его к работе на следующем такте, и, поступая на син- хровход дешифратора 12, разрешает считывание информации по. начальному адресу с ПЗУ . Считьшаемая информация состоит из трех частей.По третьему выходу ПЗУ .1 считывается истинная сумма кодов чисел, соответствующая всем временным интервалам до каждой смены информации в данном такте, и поступает на второй вход блока 14 суммы по модулю два,- где складьюаетс я с действительной аналогичной суммой на данном такте работы устройства управления с выхода накапливающего сумматора 3.

По второму выходу ПЗУ Г считьша- ется истинная сумма кодов чисел, соответствующих всем сменам информации на данном такте, и поступает на второй вход блока 13 суммь по модулю два, где складьшается с действительной аналогичной суммой на данном такте работы устройства.управления с выхода накапливающего сумматора 2.

По первому выходу ПЗУ 1 считывается код адреса ячейки ПЗУ 1, в которой хранится аналогичная информация для следующего такта работы устройства управления, и записываетс я в регистр .4 через блок 22 элементов ИЖ по сигналу с выхода элемента НЕ. 25 через элемент ИЛИ 24, за- держанному на элементе 35 задержки на время переходных процессов дешифратора 12 и считьюания ПЗУ 1.

В случае воэникновения простой /или временной ошибки на выходах оответствующих блоков 13 и 14 сумы по модулю два появляются единичые сигналы, которые по импульсу с элемента НЕ 25, задержанному на элеенте 35 задержки на время переходых процессов дешифратора 12 и счиывания ПЗУ 1, записываются в соотетствующие D-триггеры 10 и 11. Коминации их выходный сигналов на элеентах И 17 - 19 и ИЛИ 28 дают четыре значения сигнала ошибки: на вы42962 4 .

ходе 41 устройства - сигнал простой ошибки при отсутствии временной, на выходе 43 устройства - сигнал временной ошибки при отсут-ствии 5 той ошибки, на выходе 42 устройства - сигналы простой и временной ошибок, на выходе 44 - сигнал либо простой, либо временной ошибки (общий сигнал ошибки).

10 Счетчик 7, обнуленньй при подач е кода операции на вход 39 устройства импульсом с одновибратора 32, инициализирует на: выходе код такта, в котором произошла ошибка, так как t5 до выдачи общего .сигнала ошибки на его счетный вход через элемент И 20 поступают тактовые импульсы устройства управления с входа 40. Единичный сигнал ошибки с выхода элемен0 та ИЛИ 28 через элемент ИЛИ 23 и

одновибратор 31 обнуляет регистр 4 и RS-триггер 9, прекращая тем самым работу устройства.

По информации на выходах 41 - 45

5 устройства можно судить о том, какого типа и на каком такте работы устройства управления произошла ошибка.

I .

Если -ошибка в работе устройства

„ управления отсутствует, то все по- тактные сравнения соответствующих сумм приводят к нулевым сигналам на выходах 41 - 44 устройства, а на выходе счетчика 7 инициализируется код номера последнего такта устройства управления на данный момент времени.

По окончании работы устройства управления сигнал с входа 38 через элемент ИЛИ 23 и одновибратор 31 обнуляет регистр 4 и RS-триггер 9, подготавливая устройство контроля к приему следующего кода операции.

5

45

t

Формула изобретения

Устройство для контроля блоков управления, содержащее первый счетчик, RS-триггер, первый сумматор по модулю два, первый элемент ИЛИ, пер вый элемент И и элемент НЕ, причем выход первого элемента И соединен со счетным входом первого счетчика, тактовый вход устройства соединен с входом элемента НЕ, отличаю55 щ е е с я тем, что, с целью повы- .шения достоверности контроля, оио содержит запоминающий- блок, первый .и второй регистры, второй счетчик,

первый, и второй накапливающие сумматоры, генератор тактовых импульсов группу Т триггеров, первый и второй D-триггеры, второй сумматор по мо- дулю два, дешифратор, группу элементов И, блок элементов И, группу элементов ИЛИ, блок элементов ИЛИ, вто- ,рой, третий, четвертый и пятый элементы ИЛИ, второй, третий и четвер-

тый элементы И, первую и вторую группы одновибраторов, первый и второй одновибраторы, три элемента задержки, причем i-й информационный вход устройства соединен через i-e одно- вибраторы первой и второй групп с входами i-ro элемента ИЛИ группы ,n), выходы элементов ИЛИ группы соединены с синхровходами Соответствующих Т-триггеров группы и соответ- ствующими входами второго элемента ИЛИ, выходы Т-триггеров группы соединены с первыми входами соответствующих элементов И группы, выходы которых подключены к соответствующим информационным входам первого накапливающего сумматора, вход обнуления которого соединен с выходом второго элемента задержки и входом обнуления

второго накапливающего сумматора.

прямой вход первого элемента И подключен к тактовому входу устройства группа входов первого элемента ИЛИ соединена с первой группой входов .блока элементов ИЛИ и является груп- пой входов кода операции устройства группа выходов блока элементов ИЛИ соединена с группой информационных входов первого регистра, синхровход которого соединен с выходом четвер- того элемента ИЛИ, вход обнуления первого регистра объединен с Н-вхо- дом RS-триггера и подключен через второй одновибратор к выходу третьего элемента ИЛИ, группа вьгкодов пер- вого регистра соединена через дешифратор с группой входов запоминающего блока, перйыя группа выходов ко- торого соединена с второй группой ходов блока элементов ИЛИ, вторая группа выходов запоминающего блока подключена к первой группе информационных входов первого сумматора по модулю два, третья группа выходов . запоминающего блока подключена к первой группе информационных входов второго сумматора по модулю два, группы выходов первого и второго на510

5

0

5 0 5 0

капливающих сумматоров соединены соответственно с вторыми группами информационных входов первого и второго слгмматоров по модулю два, вьгхо- ;чы которьп соединены с информационными входами первого и-второго D-григ- геров соответственно, вход признака Конца работы блока управления соединен с первым входом третьего элемента ИЛИ,, второй вход которого соеди- . нен с выходом элемента ИЛИ и инверс- . ным входом первого элемента И, вход обнуления второго счетчика объединен со стробирующим входом дешифратора и подключен к выходу элемента НЕ, синхровходы перЕюго и второго 1)-триг- геров, первый вход четвертого элемента ИЛИ и вход второго элемента задержки объединены и подключены через первый элемент задержки к выходу элемента НЕ, выход первого элемента ИЛИ через первый одновибратор соединен с S-входом К5 триггера, вторым входом четвертого элемента ИЛИ и входом обнуления первого счетчика, .выход которого является выходом ре- :зультата контроля устройства, выход, ES-триггера соединен с входом запуска генератора тактовых импульсов и информационными входами Т-триггеров группы, выход генератора тактовых импз льсов соединен со счетньгм 13ХОДОМ второго счетчика, группа выходов которого соединена с группой информационных входов второго регистра , синхровход которого соединен с выходом второго элемента ИЛИ и через . третий элемент задержки - с вторыми входами элементов И группы и входом блока элементов И. группа входов- ко- . торого подключена к группе выходов , второго регистра, группа выходов бло- ка элементов И соединена с группой -1нформационньгк: входов второго накапливающего сумматора 5 выход первого D-триггера соединен с пряг-гым входом j3Toporo элемента И, инверсным входом третьего элемента И, первым входом четвертого элемента И и первым входом пятого элемента ИЛИ, выход второго D-триггера соединен с инверсным входом второго элемента И, прямьм входом третьего элемента И и вторы- входами четвертого элемента-И и пятого элемента ИЛИ, выходы второго, третьего, четвертого элементов И и пятого элемента ИЛИ образуют группу зкскодов опмбки з стройства.

«/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропрограммного автомата | 1985 |

|

SU1277114A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Сигнатурный анализатор | 1984 |

|

SU1262501A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля временной, диаграммы работы различных блоков управления и контроллеров. Целью изобретения является повьшение достоверности контроля. Цель достигается тем, что в устройство, содержащее счетчик, триггер, сумматор по модулю два, элементы ИЛИ, И, НЕ, введены запоминающий блок, два регистра, второй счетчик, два накапливающих сумматора, генератор тактовых импульсов, группа Т-триггеров, два D-триг- гера, второй сумматор по модулю два, дешифратор, группа элементов И, блок элементов И, группа элементов ИЛИ, четыре элемента ИЛИ, три элемента И, две группы одновибраторов. 2 ил.

фие 2. .

Составитель И. Сафронова ;редактор 0 Юрковецкая Техред О.Гортвай Корректор А.Зимокосов

Заказ 3706/48 . Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля блока центрального управления | 1978 |

|

SU714398A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля блоков управления | 1981 |

|

SU1003088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-11-10—Подача