W

6

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Буферное запоминающее устройство для блоков отображения информации | 1986 |

|

SU1411830A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| УСТРОЙСТВО ДЕСКРЕМБЛИРОВАНИЯ | 2006 |

|

RU2310991C2 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

Изобретение касается запоминающих устройств и может быть использовано для построения подсистем ввода цифровых изображений, (цель изобретения) устройств предварительной обработки ЦИ, устройств преобразования координат элементов массивов с матричной организацией. Цель изобретения состоит в повышении надежности и быстродействия буферного запоминающего устройства за счет уменьшения емкости дополнительных блоков памяти и количества обращений к ним при переадресации элементов изображения. Устройство содержит блоки 1, 2, 3 памяти, счетчики 4, 5 адреса, мультиплексоры 6, 7, сумматоры 8, 9 блок 10 управления, регистры 11, 12, счетчики 13, 14, мультиплексоры 15, 16. Достижение цели обеспечивается использованием кусочно-линейной апроксимации кривых геометрического преобразования изображений и рекуррентных формул для вычисления преобразованного адреса, когда составляющие текущего преобразованного адреса находятся путем сложения составляющих предыдущего преобразованного адреса с соответствующими поправками, которые постоянны для каждого линейного участка апроксимирующей ломаной преобразования. Это позволяет уменьшить количество поправок до числа линейных участков ломаных преобразования, а обращение к дополнительным блокам памяти за поправками производится только при переходах с одного линейного участка на другой. 3 ил.

СП V4

сЈ

4 О

организацией. Цель изобретения - повышение надежности и быстродействия буферного запоминающего устройства за счет уменьшения емкости дополнительных блоков памяти и количества обращений к ним при переадресации элементов изображения. Устройство содержит блоки 1 - 3 памяти, счетчики 4 и 5 адреса, мультиплексоры 6 и 7, сумматоры 8 и 9, блок 10 управления, регистры 11 и 12, счетчики 13 и 14, мультиплексоры 15 и 16. Достижение цели обеспечивается использованием кусочно- линейной аппроксимации кривых геометрического преобразования изображений и

Изобретение относится к вычислительной технике и может быть применено для построения устройств ввода изображений в цифровом виде в системы обработки.

Цель изобретения - повышение надежности и быстродействия БЗУ.

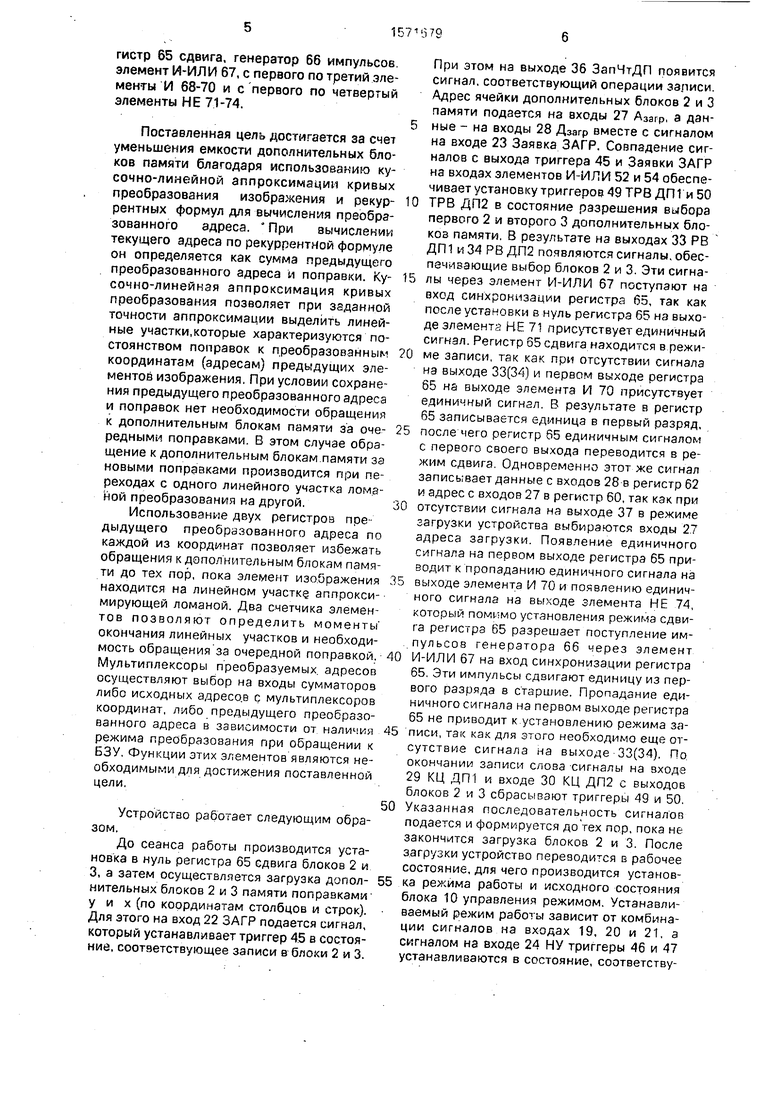

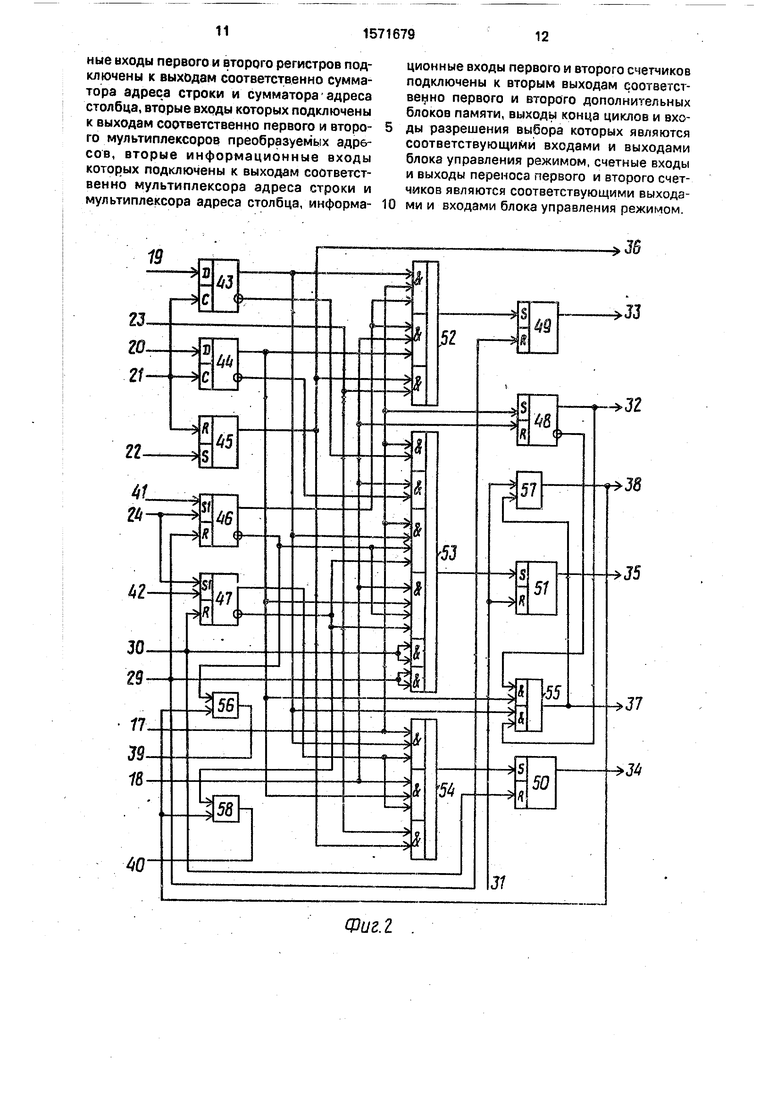

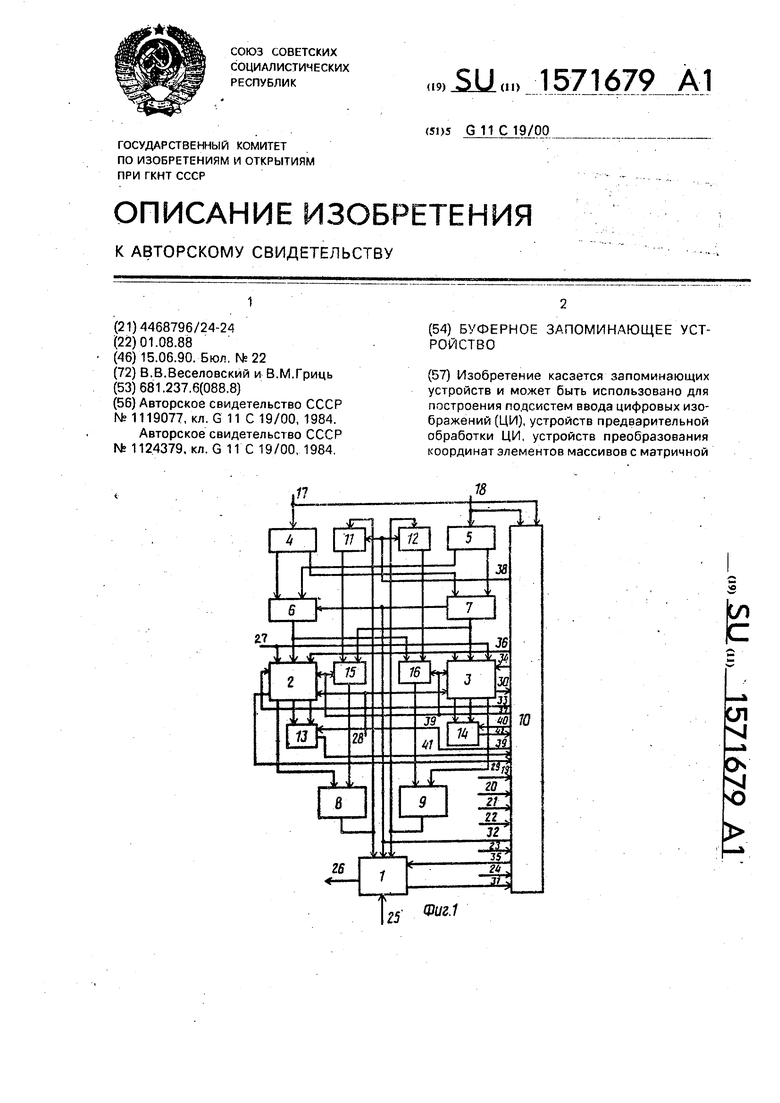

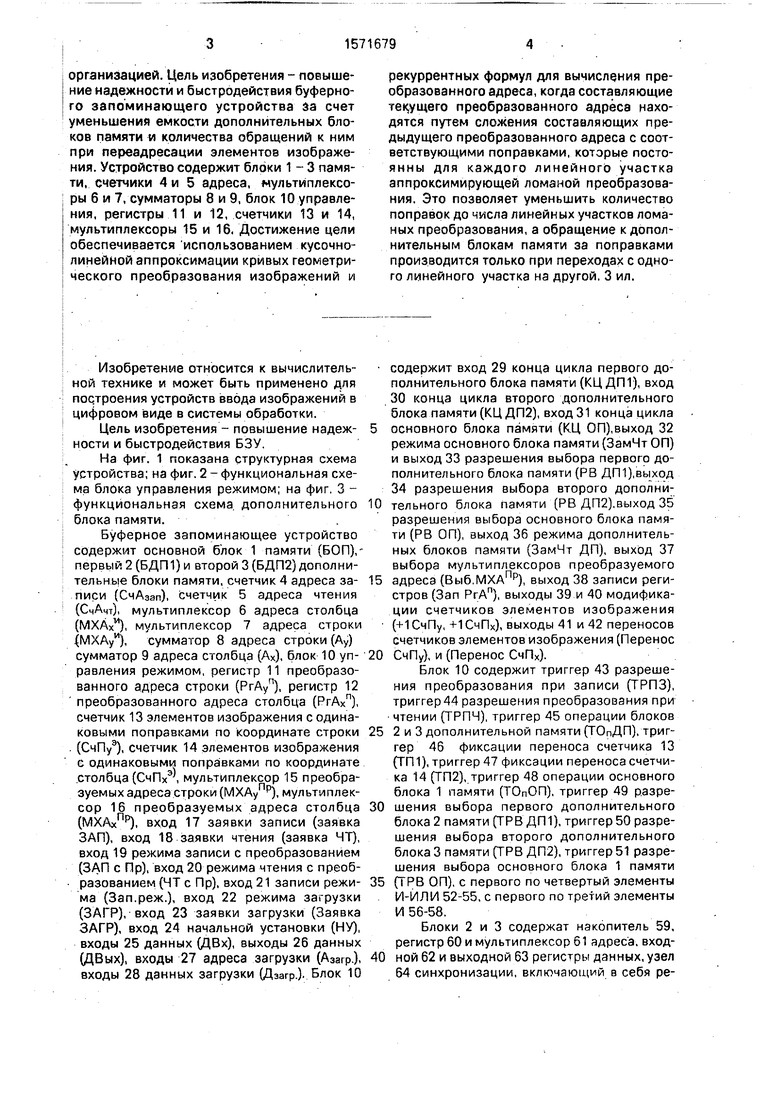

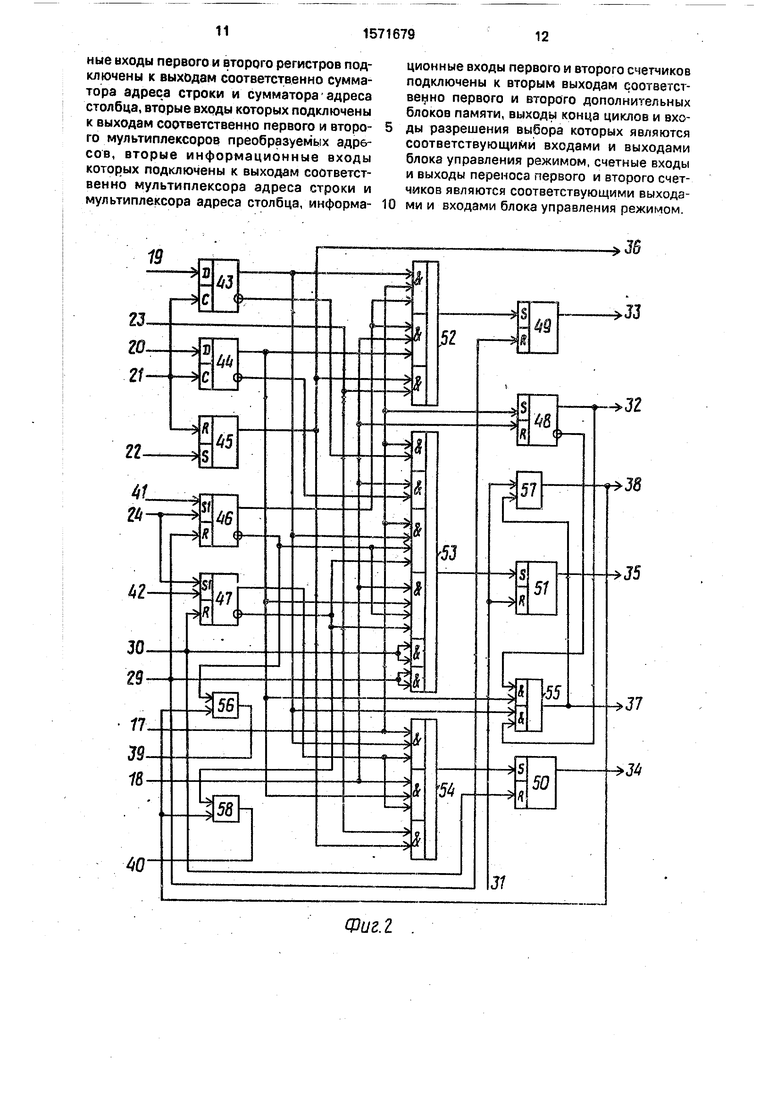

На фиг. 1 показана структурная схема устройства; на фиг. 2 - функциональная схема блока управления режимом; на фиг. 3 - функциональная схема дополнительного блока памяти.

Буферное запоминающее устройство содержит основной блок 1 памяти (БОП), - первый2(БДП1)и второй 3(БДП2) дополнительные блоки памяти, счетчик 4 адреса записи (СчАзап), счетчик 5 адреса чтения (СчАчт), мультиплексор 6 адреса столбца (МХАх11), мультиплексор 7 адреса строки {МХАу), сумматор 8 адреса строки (Ау) сумматор 9 адреса столбца (Ах), блок 10 управления режимом, регистр 11 преобразованного адреса строки (РгАуп), регистр 12 преобразованного адреса столбца (РгАхп), счетчик 13 элементов изображения с одинаковыми поправками по координате строки (СчПуэ), счетчик 14 элементов изображения с одинаковыми поправками по координате столбца (СчПх , мультиплексор 15 преобразуемых адреса строки (МХАуПр), мультиплексор 16 преобразуемых адреса столбца (), вход 17 заявки записи (заявка ЗАП), вход 18 заявки чтения (заявка ЧТ), вход 19 режима записи с преобразованием (ЗАП с Пр), вход 20 режима чтения с преобразованием (ЧТ с Пр), вход 21 записи режима (Зап.реж.), вход 22 режима загрузки (ЗАГР), вход 23 заявки загрузки (Заявка ЗАГР), вход 24 начальной установки (НУ), входы 25 данных (ДВх), выходы 26 данных (ДВых), входы 27 адреса загрузки (Азагр.). входы 28 данных загрузки (Дзагр.). Блок 10

рекуррентных формул для вычисления преобразованного адреса, когда составляющие текущего преобразованного адреса находятся путем сложения составляющих предыдущего преобразованного адреса с соответствующими поправками, которые постоянны для каждого линейного участка аппроксимирующей ломаной преобразования. Это позволяет уменьшить количество поправок до числа линейных участков ломаных преобразования, а обращение к дополнительным блокам памяти за поправками производится только при переходах с одного линейного участка на другой, 3 ил.

содержит вход 29 конца цикла первого дополнительного блока памяти (КЦДП1), вход 30 конца цикла второго дополнительного блока памяти (КЦ ДП2), вход 31 конца цикла

основного блока памяти (КЦ ОП),выход 32 режима основного блока памяти (ЗамЧт ОП) и выход 33 разрешения выбора первого дополнительного блока памяти (РВ ДП1),выход 34 разрешения выбора второго дополнительного блока памяти (РВ ДП2),выход 35 разрешения выбора основного блока памяти (РВ ОП), выход 36 режима дополнительных блоков памяти (ЗамЧт ДП), выход 37 выбора мультиплексоров преобразуемого

адреса (Выб.МХА р), выход 38 записи регистров (Зап РгАп), выходы 39 и 40 модификации счетчиков элементов изображения (+1 СчПу, +1 СчПх), выходы 41 и 42 переносов счетчиков элементов изображения (Перенос

СчПу), и (Перенос СчПх).

Блок 10 содержит триггер 43 разрешения преобразования при записи (ТРПЗ), триггер44 разрешения преобразования при чтении (ТРПЧ), триггер 45 операции блоков

2 и 3 дополнительной памяти (ТОпДП), триггер 46 фиксации переноса счетчика 13 (ТП1), триггер 47 фиксации переноса счетчика 14 (ТП2), триггер 48 операции основного блока 1 памяти (ТОпОП), триггер 49 разрешения выбора первого дополнительного блока 2 памяти (ТРВ ДП1), триггер 50 разрешения выбора второго дополнительного блока 3 памяти (ТРВ ДП2), триггер 51 разрешения выбора основного блока 1 памяти

(ТРВ ОП), с первого по четвертый элементы И-ИЛИ 52-55, с первого по элементы И 56-58.

Блоки 2 и 3 содержат накопитель 59, регистр 60 и мультиплексор 61 адреса, вход0 ной 62 и выходной 63 регистры данных, узел 64 синхронизации, включающий в себя регистр 65 сдвига, генератор 66 импульсов, элемент И-ИЛИ 67, с первого по третий элементы И 68-70 и с первого по четвертый элементы НЕ 71-74.

Поставленная цель достигается за счет уменьшения емкости дополнительных блоков памяти благодаря использованию кусочно-линейной аппроксимации кривых преобразования изображения и рекуррентных формул для вычисления преобразованного адреса. При вычислении текущего адреса по рекуррентной формуле он определяется как сумма предыдущего преобразованного адреса и поправки. Кусочно-линейная аппроксимация кривых преобразования позволяет при заданной точности аппроксимации выделить линейные участки,которые характеризуются постоянством поправок к преобразованным координатам (адресам) предыдущих элементов изображения. При условии сохранения предыдущего преобразованного адреса и поправок нет необходимости обращения к дополнительным блокам памяти за очередными поправками. В этом случае обращение к дополнительным блокам памяти за новыми поправками производится при переходах с одного линейного участка ломаной преобразования на другой.

Использование двух регистров предыдущего преобразованного адреса по каждой из координат позволяет избежать обращения к дополнительным блокам памяти до тех пор, пока элемент изображения находится на линейном участку аппроксимирующей ломаной. Два счетчика элементов позволяют определить моменты окончания линейных участков и необходимость обращения за очередной поправкой. Мультиплексоры преобразуемых адресов осуществляют выбор на входы сумматоров либо исходных адресо.в с мультиплексоров координат, либо предыдущего преобразованного адреса в зависимости от наличия режима преобразования при обращении к БЗУ. Функции этих элементов являются необходимыми для достижения поставленной цели.

Устройство работает следующим образом.

До сеанса работы производится установка в нуль регистра 65 сдвига блоков 2 и 3, а затем осуществляется загрузка дополнительных блоков 2 и 3 памяти поправками- у и х (по координатам столбцов и строк). Для этого на вход 22 ЗАГР подается сигнал, который устанавливает триггер 45 в состояние, соответствующее записи в блоки 2 и 3.

При этом на выходе 36 ЗапЧтДП появится сигнал, соответствующий операции ззлиси. Адрес ячейки дополнительных блоков 2 и 3 памяти подается на входы 27 Азагр, а дан- 5 ные - на входы 28 Дзагр вместе с сигналом на входе 23 Заявка ЗАГР. Совпадение сигналов с выхода триггера 45 и Заявки ЗАГР на входах элементов И-ИЛИ 52 и 54 обеспечивает установку триггеров 49 ТР8 ДП1 и 50 10 ТРВ ДП2 в состояние разрешения выбора первого 2 и второго 3 дополнительных бло- коз памяти. В результате на выходах 33 РВ ДП 1 и 34 РВ ДП2 появляются сигналы, обеспечивающие выбор блоков 2 и 3. Эти сигна- 15 лы через элемент И-ИЛИ 67 поступают на вход синхронизации регистра 65, так как после установки в нуль регистра 65 на выходе элемента НЕ 71 присутствует единичный сигнал. Регистр 65 сдвига находится в режи- 0 ме записи, так как при отсутствии сигнала нэ выходе 33(34) и первом выходе регистра 65 на выходе элемента И 70 присутствует единичный сигнал. В результате в регистр 65 записывается единица в первый разряд,

5 после чего регистр 65 единичным сигналом с первого своего выхода переводится в режим сдвига. Одновременно этот же сигнал записывает данные с входов 28 в регистр 62 и адрес с входов 27 в регистр 60, так как при

0 отсутствии сигнала на выходе 37 в режиме загрузки устройства выбираются входы 27 адреса загрузки. Появление единичного сигнала на первом выходе регистра 65 приводит к пропаданию единичного сигнала на

5 выходе элемента И 70 и появлению единичного сигнала на выходе элемента НЕ 74, который помимо установления режима сдвига регистра 65 разрешает поступление импульсов генератора 66 через элемент

0 И-ИЛИ 67 на вход синхронизации регистра 65. Эти импульсы сдвигают единицу из первого разряда в старшие. Пропадание единичного сигнала на первом выходе регистра 65 не приводит к установлению режима за5 писи, так как для этого необходимо еще отсутствие сигнала на выходе 33(34). По окончании записи слова сигналы на входе 29 КЦ ДП1 и входе 30 КЦ ДП2 с выходов блоков 2 и 3 сбрасывают триггеры 49 и 50.

0 Указанная последовательность сигналов подается и формируется до тех пор, пока не закончится загрузка блоков 2 и 3. После загрузки устройство переводится в рабочее состояние, для чего производится установ5 ка режима работы и исходного состояния блока 10 управления режимом. Устанавливаемый режим работы зависит от комбинации сигналов на входах 19, 20 и 21, а сигналом на входе 24 НУ триггеры 46 и 47 устанавливаются в состояние, соответствуощее наличию переносов счетчиков 13 и И.

Режим записи с преобразованием и чте- кия без преобразования.

Для установки этого режима на входы 19 и 21 подаются единичные сигналы, а на вход 20 - нулевой. При Этом триггер 43 ТРПЗ устанавливается в единичное состояние, триггер 44 ТРПЧ - в нулевое, а триггер 45 ТОпДП сбрасывается сигналом на входе 21 Зап.реж,, тем самым устанавливается операция чтения для блоков 2 и 3 дополнительной памяти,

Первая заявка ЗАП, поступившей на вход 17, устанавливает триггер 48 ТОпОП в состояние, соответствующее записи в основной блок 1 памяти, и, пройдя через первый 52 и третий 54 элементы И-ИЛИ, устанавливает триггеры 49 трв ДП1 и ЬО ТРВ ДП2 в состояния, ссответс1,вующие выбору блоков 2 и 3. Сигнал на выходе 32 обеспечивает выбор счетчика 4 Азап мультиплексорами 6 МХАХИ и 7 МХАуи. В результате в выходные регистры 63 блоков 2 и 3 из ячеек, определяемых координатами Ахи и Ауи, заносятся коды поправок координатам столбцов и строк и коды количества элементов изображения на пепвых линейных участках ломаной преобразования, которые затем заносятся в счетчики 13 и 14 по еигца лам конца циклов обращения на входах 2С КЦДП1 и 30 КЦДП2, также сбрасывающем триггеры 49 и 50 и устанавливающие (через второй элемент И-ИЛ И 53) триггер 51 ТРВ ОП. На выходе четвертого элемента /-ИЛИ 55 появляется сигнал 37 Выб.МХАПр, обеспечивающий выбор мультиплексорами 15 и 16 выходов регистров 11 Рг Ауп и 12 Рг Ах.В результате на выходах сумматоров 8 и 9 появляются значения преобразованных координат АХП1 и АуП образующих адрес записи данных на входах 25 в основной блок 1 памяти. В конце цикла обращения к блоку 1 сигналом на шине КЦ ОП сбрасывается триггер 51 ТРВ ОП и одновременно этот сигнал проходит через второй элемент И 57 формируя сигнал 38 Зап Рг Ап, котпоыи за- пусывает в регистры 11 и 12 коды с выходов сумматоров 8 и 9 соответственно. Гак как триггеры 46 и 47 сбрасываются сигналами на входах 29 и 30, то сигнал на выходе 38 проходит через первый 56 и третий 58 элементы А на выходы 39 и 40, модифицируя счетчики 13 и 14.

При записи следующего элемента изображения обращение к дополнительным блокам 2 и 3 памяти блокируются, так как триггеры 46 и 47 сброшены. В этом случае заявка ЗАП на шине 17 проходит чгрез пятую группу входов второго элемента И-ИЛИ

52, так как триггер 43 ТРПЗ установлен в единицу, а триггеры 46 и 47 - к -у/ь, и устанавливает триггер 51 ТРВ ОП а единицу, разрешая тем самым обращение косночному блоку 1 памяти. Адреи йчейки памяти блока 1 формируется су матирс л 8 и 9 из слагаемых, хранящихся в per/страх 11 и 12 и регистрах дополнит ильных блоков 2 и 3 памяти ъигчалич на входе 31 триггер 51

0 ТРВ ОП сбрасывается и одновременно фор

мируютич сигналы модификации счетчиков

13 и 14 на шинах 38 м 40. По окончании

линейного участка на одной из ломаных

преобразований соответствующий триггер

5 46 или 47 фиксации переноси устанавливаете а единицу, разрешая установку в единицу одного из триггеров 49 или 50, тем самым производится обращение к одному из блоков 2 или 3 при наличии сигнала на

0 иине 17

При чтении данных из блока 1 в этом режиме мультиплексоры 6 и 7 выбирают вы- счетчика 5 адреса чтения, мультиплексоры 15 и 16 подключают к входам

5 сумматоров 8 и 9 вместо выходов регистров 11 и 12 выходы мультиплексоров б и 7, т.е выходи счетчика 5 адреса чтения. Сигнал с еч да 18 проходит через входы второй группы зтооого элемента И-ИЛИ 53, так кактригO rep 44 ТРПЧ установлен в нуль, и устанавливает триггер 51 ТРВ ОП в единицу, сброс ксторого осуществляется в конце цикла обращения к блоку 1 сигналом на входе 31 КЦОП

5

Режим записи без преобразования и чтения с преобразованием

Для установки этого режима на входе 19 ЗАП с Пр подается нулевой сигнал а на

0 входах 20 и 21 - единичные При записи данных в блок 1 сигнал на входе 1 7 Заявка ЗАИ сразу же устанавливает в единицу триггер 51 ТРВ ОП, так как на входах первой группы входов второго элемента И-ИЛИ 53

5 совпадают единичные сигналы Заявка ЗАП v с нулевого выхода триггера 43 трпЗ, при этом обращение к дополнительным блокам 1 и 3 памяти блокируется нулевым сигналом с первого выхода триггера 43 ТРПЗ. На вы0 ходе 32 выб. МХАИ появляется единичный сигнал, а на выходе 37 Зыб МХА р - нулевой При такой комбинации сигналов мультиплексоры 6 и 7, 15 и 16 зыоираюг выходы счетчика 4 Азап. Код адреса записи суммиру5 ется с нулевыми кодами с выходов блоков 2 и 3, так как нулевой сигнал на выходе 37 блокирует выдачу содержимого выходных регистров блоков 2 и 3, т е на адресных входах основного блока 1 памяти присутствует код адреса записи с выходов счетчика 4

При чтении сигнал с входа 18 Заявка ЧТ при первом обращении за данными к блоку

Iпроходит через первый 52 и третий 54 элементы И-ИЛИ, так как триггеры 46 и 47 установлены в единичг- ое состояние сигналом с входа 24 НУ и -фиггер 49 ТРВ ДП1, а также триггер 50 ТРВ ДП2 устанавливаются в единичное состояние, разрешая чтение поправок из блоков 2 иЗ. На выходе 37 Выб. МХАПр появляется единичный сигнал из-за совпадения единичных сигналов с первого выхода триггера 44ТРПЧ и с второго выхода триггера 48 ТОпОП. Содержимое регистров

IIи 12 (при первом чтении - нулевое) суммируется с поправками с выходов блоков 2 иЗ насумматорах8 и 9. Сигналами на шинах 29 КЦ ДП1 и 30 КЦ ДП2 триггеры 49 и 50 сбрасываются, а триггер 51 ТРВ ОП через второй элемент И-ИЛИ 53 устанавливается в единицу, разрешая обращение к блоку 1 Одновременно в счетчики 13 и 14 записываются значения количества элементов изображения на текущих линейных участках ломаной преобразования, а триггеры 46 и 47 сбрасываются. При последующих обращениях к устройству за дачными чтение поправок блокируется и используется старое содержимое выходных регистров блоков 2 и 3 до тех пор, пока не появится хотя бы один из сигналов на шинах 41 и 42. Содержимое счетчиков 13 и 14 каждый раз модифицируется по сиг налу на шине 31 КЦ ОП, который, проходя через второй элемент И 57 обеспечивает запись преобразованного адреса чтения в регистры 11 и 12, формируя сигнал на шине 38 Зал Рг Ап, а этот сигнал в свою очередь проходит через элементы И 56 и 58, формируя сигналы на выходах 39 и 40.

В режиме записи без преобразования устанавливаемого при нулевых сигналах на входах 19 и 20 и единичном на входе 21, запись производится аналогично записи в режиме без преобразования и чтения с преобразованием, чтение - аналогично чтению в режиме записи с преобразованием и чтения без преобразования.

Формула изобретения Буферное запоминающее устройство, содержащее основной блок памяти, информационные входы и выходы которого являются соответственно входами и выходами данных устройства, счетчик адреса записи и счетчик адреса чтения, счетные входы которых являются входами соответственно требования записи -и требования чтения устройства и подключены соответственно к входу сигнала записи и входу сигнала чтения блока управления режимом, мультиплексор адреса столбца и мультиплексор

адреса строки, первый и второй дополнительные блоки памяти, сумматор адреса строки и сумматор адреса столбца, первые информационные входы которых подключе- 5 ны к первым информационным выходам со- отвегственно первого и второго дополнительных блоков памяти, первые адресные входы и информационные входы которых объединены и являются 10 соответственно входами адреса загрузки входами данных загрузки устройства, вторые адресные входы первого и второго дополнительных блоков памяти подключены к выходам соответственно мультиплексора 15 адреса столбца и мультиплексора адреса строки, управляющие входы которых подключены к входу задания режима основного блока памяти и к соответствующему выходу блока управления режимом, входы задания

0 режима первого и второго дополнительных блоков памяти объединены и подключены к соответствующему выходу блока управления режимом,первые информационные входы мультиплексора адреса столбца и

5 мультиплексора адреса строки подключены к первым выходам соответственно счетчика адреса записи и счетчика адреса чтения, вторые выходы которых подключены к вторым информационным входам соответст0 веннс мультиплексора адреса строки и мультиплексора адреса столбца, выход конца цикла основного блока памяти, вход разрешения выбора основного блока памяти подктючены с соответствующим входу и вы5 ходу блока управления режимом, вход начальной установки, вход заявки загрузки, вход режима загрузки, вход режима записи, вход режима чтения с преобразованием и вход режима записи с преобразованием

0 блока управления режимом являются одноименными входами устройства, выходы сумматора адреса строки м сумматора адреса столбца подключены к первому и второму адресным входам основного блока памяти,

5 отличающееся тем, что, с целью повышения надежности и быстродействия, оно содержит первый и второй регистры, первый и второй счетчики, первый и второй мультиплексоры преобразуемых адресов,

0 управляющие входы которых подключены к входам выдачи данных первого и второго дополнительных блоков памяти и к соответствующему выходу блока управления режимом, первые информационные входы

5 первого и второго мультиплексоров преобразуемых адресов подключены к выходам соответсгвечно первого и второго регистров, входы записи которых объединены и подключены к соответствующему выходу блоха управления режимом, информациейные входы первого и второго регистров подключены к выходам соответственно сумматора адреса строки и сумматора адреса столбца, вторые входы которых подключены к выходам соответственно первого и второго мультиплексоров преобразуемых адресов, вторые информационные входы которых подключены к выходам соответственно мультиплексора адреса строки и мультиплексора адреса столбца, информа0

ционные входы первого и второго счетчиков подключены к вторым выходам соответственно первого и второго дополнительных блоков памяти, выходы конца циклов и входы разрешения выбора которых являются соответствующими входами и выходами блока управления режимом, счетные входы и выходы переноса первого и второго счетчиков являются соответствующими выходами и входами блока управления режимом.

Фиг.1 .

33(34)

Фиг.з

KB(9 KW)

I

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-06-15—Публикация

1988-08-01—Подача