12804

информационные выходы 24, управляю- Dpie входы 25-29, информационные входы 30 и информационные выходы 31. Поставленная цель достигается за

счет уменьшения емкости дополнительных блоков 2 и 3 памяти благодаря симметричности геометрических преобразований относительно некоторых

.1

Изобретение относится к вычислительной технике и может быть использовано при создании систем ввода и предварительной обработки цифровых изображений в вычислительные системы на основе буферных запоминающих устройств (БЗУ),

Целью изобретения является повышение надежности устройства,

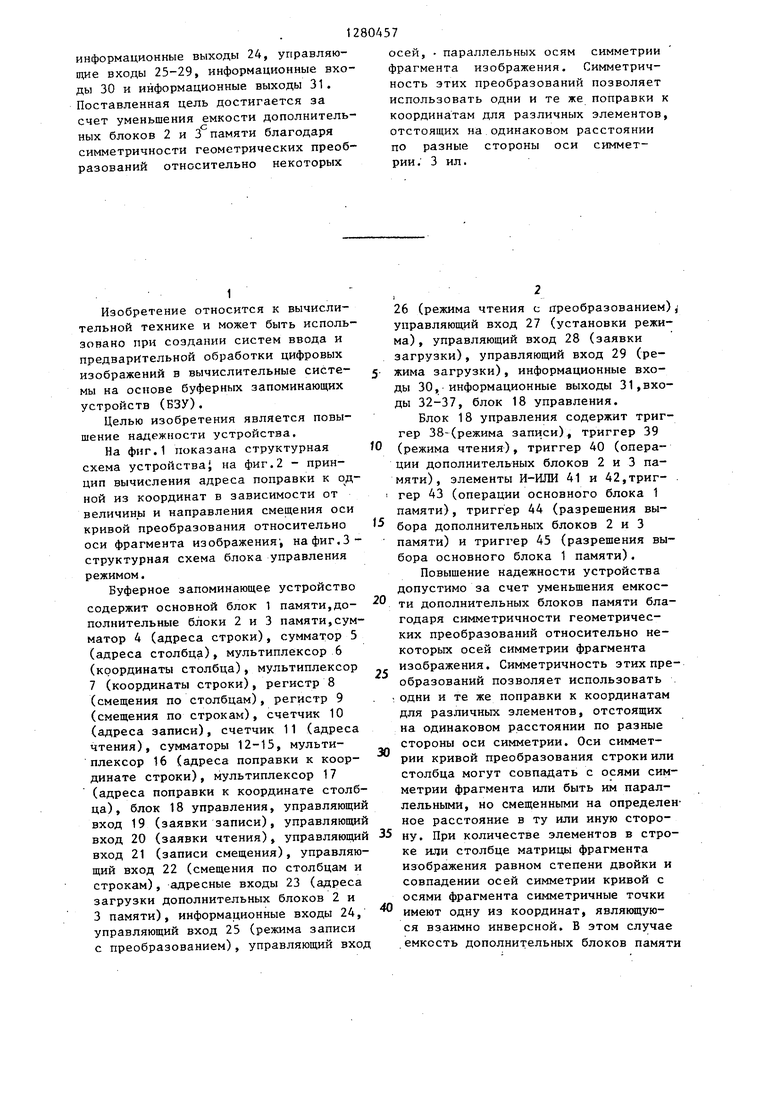

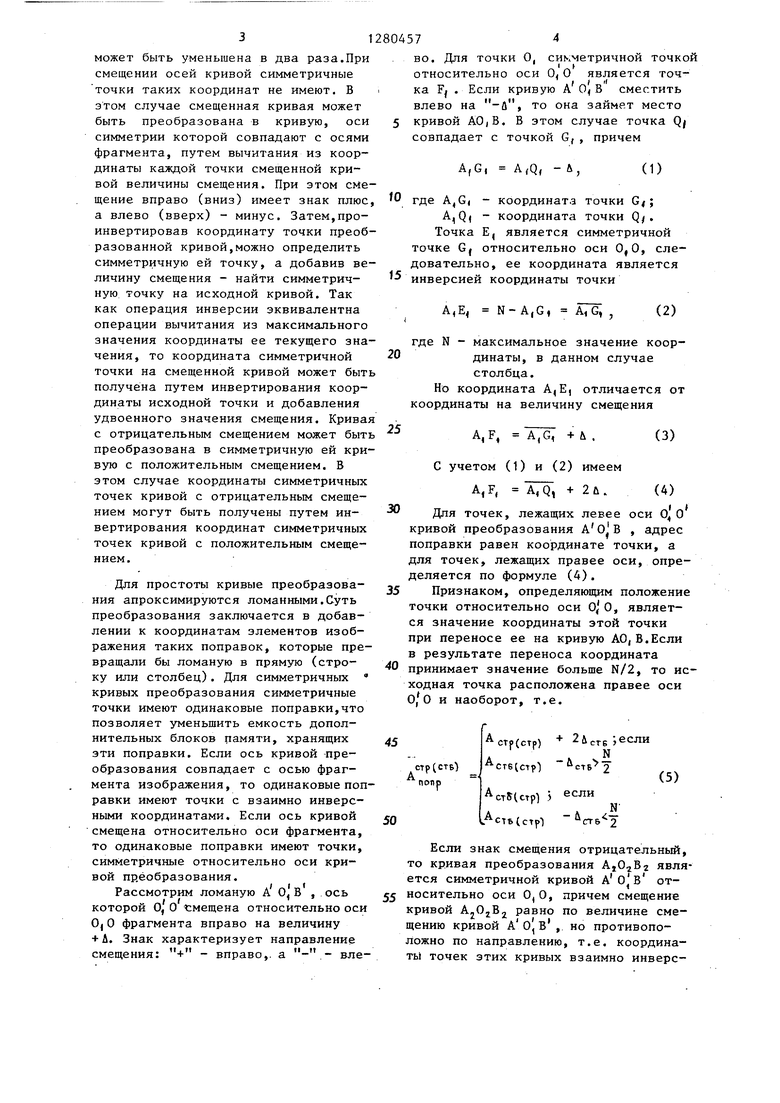

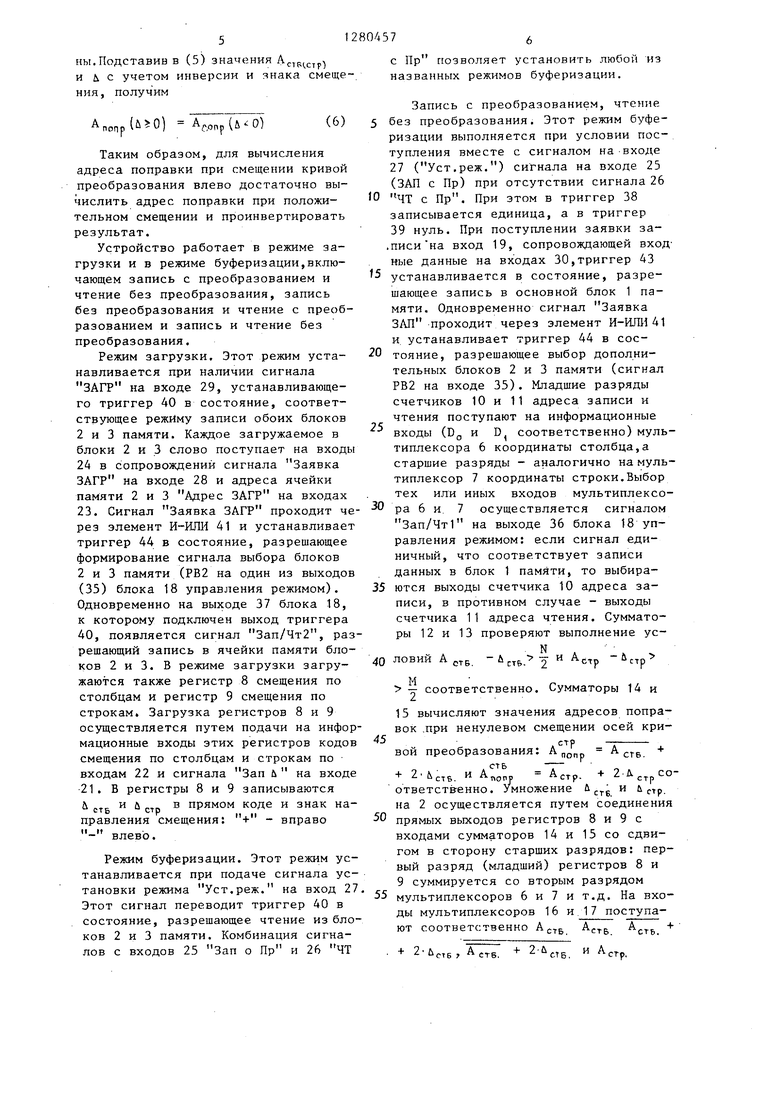

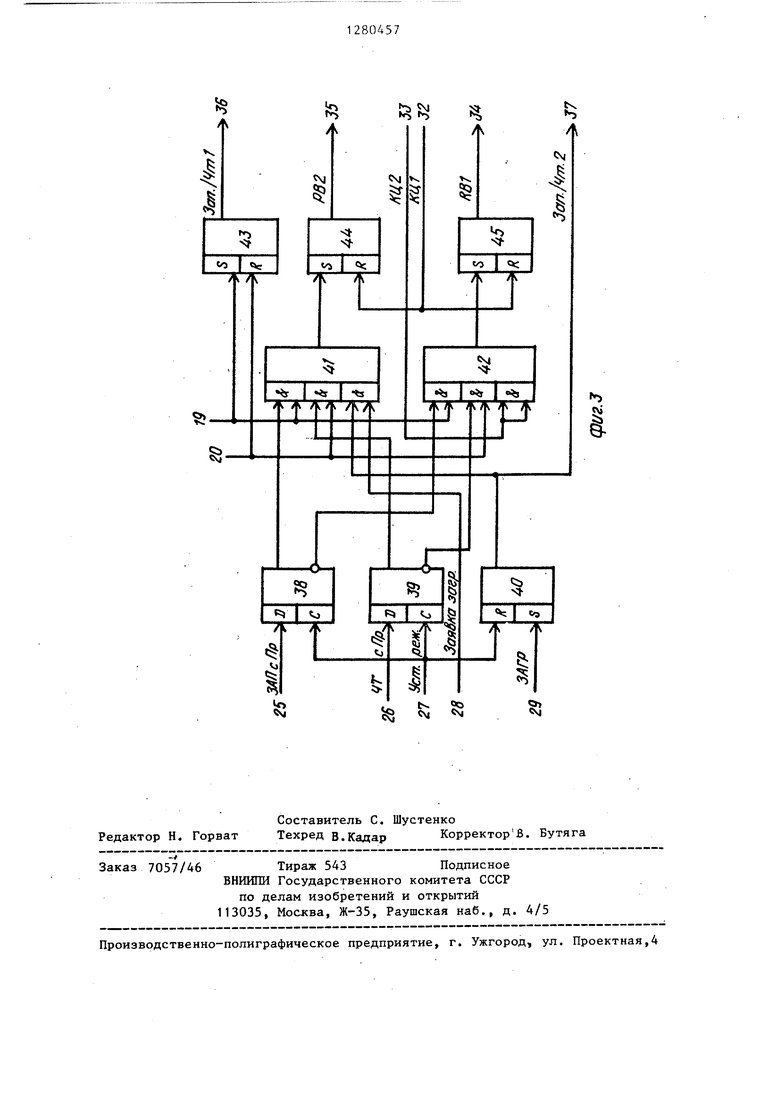

На фиг.1 показана структурная схема устройстваi на фиг.2 - принцип вычисления адреса поправки к одной из координат в зависимости от величины и направления смещения оси кривой преобразования относительно оси фрагмента изображения; нафиг.З- структурная схема блока управления режимом.

Буферное запоминающее устройство содержит основной блок 1 памяти,дополнительные блоки 2 и 3 памяти,сумматор 4 (адреса строки), сумматор 5 (адреса столбца), мультиплексор 6 (координаты столбца), мультиплексор 7 (координаты строки), регистр 8 (смещения по столбцам), регистр 9 (смещения по строкам), счетчик 10 (адреса записи), счетчик 11 (адреса чтения), сумматоры 12-15, мультиплексор 16 (адреса поправки к координате строки), мультиплексор 17 (адреса поправки к координате столбца), блок 18 управления, управляющи вход 19 (заявки записи), управляющи вход 20 (заявки чтения), управляющи вход 21 (записи смещения), управляющий вход 22 (смещения по столбцам и строкам), адресные входы 23 (адреса загрузки дополнительных блоков 2 и 3 памяти), информационные входы 24, управляющий вход 25 (режима записи с преобразованием), управляющий вхо

осей, параллельных осям симметрии фрагмента изображения. Симметричность этих преобразований позволяет использовать одни и те же поправки к координатам для различных элементов, отстоящих на одинаковом расстоянии по разные стороны оси симметрии . 3 ил.

5

5

0

5

0

0

26 (режима чтения с преобразованием) управляющий вход 27 (установки режима) , управляющий вход 28 (заявки загрузки), управляющий вход 29 (режима загрузки), информационные входы 30, информационные выходы 31,входы 32-37, блок 18 управления.

Блок 18 управления содержит триггер 38-(режима записи) триггер 39 (режима чтения), триггер 40 (операции дополнительных блоков 2 и 3 памяти) , элементы И-ИЛИ 41 и 42,триг- . гер 43 (операции основного блока 1 памяти), триггер 44 (разрешения выбора дополнительных блоков 2 и 3 памяти) и триггер 45 (разрешения выбора основного блока 1 памяти).

Повышение надежности устройства допустимо за счет уменьшения емкости дополнительных блоков памяти благодаря симметричности геометрических преобразований относительно некоторых осей симметрии фрагмента изображения. Симметричность этих преобразований позволяет использовать . одни и те же поправки к координатам для различных элементов, отстоящих на одинаковом расстоянии по разные стороны оси симметрии. Оси симметрии кривой преобразования строки или столбца могут совпадать с осями симметрии фрагмента или быть им параллельными, но смещенными на определенное расстояние в ту или иную сторону. При количестве элементов в строке или столбце матрицы фрагмента изображения равном степени двойки и совпадении осей симметрии кривой с осями фрагмента симметричные точки имеют одну из координат, являющуюся взаимно инверсной. В этом случае .емкость дополнительных блоков памяти

может быть уменьшена в два раза.При смещении осей кривой симметричные точки таких координат не имеют. В этом случае смещенная кривая может быть преобразована в кривую, оси симметрии которой совпадают с осями фрагмента, путем вычитания из координаты каждой точки смещенной кривой величины смещения. При этом смещение вправо (вниз) имеет знак плюс а влево (вверх) - минус. Затем,про- инвертировав координату точки преобразованной кривой,можно определить симметричную ей точку, а добавив величину смещения - найти симметричную точку на исходной кривой. Так как операция инверсии эквивалентна операции вычитания из максимального значения координаты ее текущего значения, то координата симметричной точки на смещенной кривой может быть получена путем инвертирования координаты исходной точки и добавления удвоенного значения смещения. Кривая с отрицательным смещением может быть преобразована в симметричную ей кривую с положительным смещением. В этом случае координаты симметричных точек кривой с отрицательным смещением могут быть получены путем инвертирования координат симметричных точек кривой с положительным смещением.

Для простоты кривые преобразования апроксимируются ломанными.Суть преобразования заключается в добавлении к координатам элементов изображения таких поправок, которые превращали бы ломаную в прямую (строку или столбец). Для симметричных кривых преобразования симметричные точки имеют одинаковые поправки,что позволяет уменьшить емкость дополнительных блоков памяти, хранящих эти поправки. Если ось кривой преобразования совпадает с осью фрагмента изображения, то одинаковые поправки имеют точки с взаимно инверсными координатами. Если ось кривой смещена относительно оси фрагмента, то одинаковые поправки имеют точки, симметричные относительно оси кривой преобразования.

Рассмотрим ломаную А О, В , ось которой О, О смещена относительно оси О,О фрагмента вправо на величину «Л. Знак характеризует направление смещения: + - вправо,, а -.- влево. Для точки О, симметричной точкой относительно оси 0 О является точка FJ . Если кривую А О, в сместить влево на -fl, то она займет место кривой АО,В. В этом случае точка Q/ совпадает с точкой G, , причем

A,G, A,Q, - &,

(1)

где A,G( - координата точки А,Q( - координата точки Q/. Точка Е, является симметричной точке GJ относительно оси 0,0, следовательно, ее координата является инверсией координаты точки

А, Е N - А, G, AI G, J

(2)

где N - максимальное значение коор- динаты, в данном случае

столбца.

Но координата А,Е, отличается от координаты на величину смещения

25

А, F, A,G, + Л . С учетом (1) и (2) имеем

(3)

A,F, A,Q, + 2й. (4)

Для точек, лежащих левее оси 0 О кривой преобразования , адрес поправки равен координате точки, а для точек, лежащих правее оси, определяется по формуле (4).

Признаком, определяющим положение точки относительно оси 0 О, является значение координаты этой точки при переносе ее на кривую АО, В.Если в результате переноса координата

принимает значение больше N/2, то исходная точка расположена правее оси о О и наоборот, т.е.

СТр(СТБ) ПОПр

AcTj)(cTp) - 2&етб ;если

СТ6(СТ1)

(5)

) ) если

А - Л (сТр1

Если знак смещения отрицательный, то кривая преобразования является симметричной кривой А 0 В от- носительно оси 0,0, причем смещение кривой AjOjBj равно по величине смещению кривой А О,В, но противоположно по направлению, т.е. координаты точек этих кривых взаимно инверсны.Подставив в (5) значения ,

и с учетом инверсии и знака смещения, получим

А„„,р() ,,()

(6)

СТБ стр

правления смещения:

Таким образом, для вычисления адреса поправки при смещении кривой преобразования влево достаточно вычислить адрес поправки при положительном смещении и проинвертировать результат.

Устройство работает в режиме загрузки и в режиме буферизации,включающем запись с преобразованием и чтение без преобразования, запись без преобразования и чтение с преобразованием и запись и чтение без преобразования.

Режим загрузки. Этот режим устанавливается при наличии сигнала ЗАГР на входе 29, устанавливающего триггер 40 в состояние, соответствующее режиму записи обоих блоков 2 и 3 памяти. Каждое загружаемое в блоки 2 и 3 слово поступает на входы 24 в сопровождений сигнала Заявка ЗАГР на входе 28 и адреса ячейки памяти 2 и 3 Адрес ЗАГР на входах 23. Сигнал Заявка ЗАГР проходит через элемент И-ИЛИ 41 и устанавливает триггер 44 в состояние, разрешающее формирование сигнала выбора блоков 2 и 3 памяти (РВ2 на один из выходов (35) блока 18 управления режимом). Одновременно на выходе 37 блока 18, к которому подключен выход триггера 40, появляется сигнал Зап/Чт2, разрешающий запись в ячейки памяти блоков 2 и 3. В режиме загрузки загружаются также регистр 8 смещения по столбцам и регистр 9 смещения по строкам. Загрузка регистров 8 и 9 осуществляется путем подачи на информационные входы этих регистров кодов смещения по столбцам и строкам по входам 22 и сигнала Зап и на входе 21, В регистры 8 и 9 записываются i и U ,„ в прямом коде и знак на - вправо

- влево.

Режим буферизации. Этот режим устанавливается при подаче сигнала установки режима Уст.реж. на вход 27. Этот сигнал переводит триггер 40 в состояние, разрешающее чтение из блоков 2 и 3 памяти. Комбинация сигналов с входов 25 Зап о Пр и 26 ЧТ

с Пр позволяет установить любоГ названных режимов буферизации.

из

5

0

5

0

5

0

Запись с преобразованием, чтение без преобразования. Этот режим буферизации выполняется при условии поступления вместе с сигналом на -входе 27 (Уст.реж.) сигнала на входе 25 (ЗАП с Пр) при отсутствии сигнала 26 ЧТ с Пр. При этом в триггер 38 записывается единица, а в триггер 39 нуль. При поступлении заявки записи на вход 19, сопровождающей входные данные на входах 30,триггер 43 устанавливается в состояние, разрешающее запись в основной блок 1 памяти. Одновременно сигнал Заявка ЗАП проходит через элемент И-ИЛН41 и устанавливает триггер 44 в состояние, разрешающее выбор дополнительных блоков 2 и 3 памяти (сигнал РВ2 на входе 35). Младшие разряды счетчиков 10 и 11 адреса записи и чтения поступают на информационные входы (Dg и D соответственно) мультиплексора 6 координаты столбца,а старшие разряды - аналогично на мультиплексор 7 координаты строки.Выбор тех или иных входов мультиплексора 6 и. 7 осуществляется сигналом Зап/Чт1 на выходе 36 блока 18 управления режимом: если сигнал единичный, что соответствует записи данных в блок 1 памяти, то выбираются выходы счетчика 10 адреса записи, в противном случае - выходы счетчика 11 адреса чтения. Сумматоры 12 и 13 проверяют выполнение усN

ловий А pTg - ЛСТБ. J и А.

-йстр

5

- соответственно. Сумматоры 14 и

15 вычисляют значения адресов поправок .при ненулевом смещении осей кристр

вой преобразования: А А.- -iСТБ

стр -

попр сге.

+ 2 . is .

и А,

А,

стб. попр стр. ответственно. Умножение и

на 2

ь

СГ6. стр. осуществляется путем соединения

0 прямых выходов регистров 8 и 9 с входами сумматоров 14 и 15 со сдвигом в сторону старших разрядов: первый разряд (младший) регистров 8 и 9 суммируется со вторым разрядом

5 мультиплексоров 6 и 7 и т.д. На входы мультиплексоров 16 и 17 поступа- А,

ют соответственно + 2-1,

СТБ.

СТБ Г CTS.

+ 2-й

СТБ.

СТБ. И А

СТБ,

стр.

А сТр- ) СТр

2-й,,

р стр

+ 2 й

стр.

Выбор информационных входов мультиплексоров 16 и 17 осуществляется выходными сигналами сумматоров 12 и 13 и разрядами регистров 8 и 9, содержащими признак направления смещения.

Если признак равен нулю (смещение вправо) и старший разряд сумматоров 12 и 13 нулевой, то выбираются A(,g и соответственно.

Если признак смещения нулевой,а старшие разряды сумматоров 12 и 13

единичные,то выбираются А. н-2-ь

СТр

Чтр

И А

СТБ

+ 2.Ь„БЕсли признак единичный,а старший разряд нулевой, то выбираются А +

и Лету. - ,2-Ь стр ЕСЛИ признак и старший разряд

единичные, то выбираются А

СГБ

и А,

После чтения поправок из блоков 2 и 3 сигналом КП2, проходящим через элемент И-ИЛИ 42, устанавливается триггер 45 в состояние, разрешающее выбор блока 1. Суммирование и AJ,, с соответствующими поправками на сумматорах 4 и 5 позволяет получить код адреса блока 1, что вместе с сигналами РВ1 и Зап/Чт1 обеспечивает запись входных данн ых в этот блок 1 по нужному адресу.При чтении из блока 1 нулевой сигнал триггера 39 блокирует установку сигналом 20 Заявка ЧТ триггера 44 в состояние выбора дополнительных блоков 2 и 3 памяти. В этом случае сигнал 20 устанавливает триггер 43 в состояние, разрешающее чтение из блока 1, и через второй элемент И-ИЛИ 42 триггер 45 в состояние выбора блока 1. Тем самым блокируется чтение поправок из дополнительных блоков 2 и 3 памяти и код адреса равен значению содержимого счетчика 11 адреса чтения, так как мультиплексоры 6 и 7 выбирают выходы этого счетчика 11. После окончания цикла обращения к блоку 1 сигнал на выходе 32 КЦ1 сбрасывает триггеры 44 и 45.

Запись без преобразования,чтение с преобразованием. Этот режим устанавливается при наличии сигналов на входах 26 (Чт с.Пр) и 27 (Уст. реж.) и отсутствии сигнала на входе 25 (ЗАП с ПР). При этом в триггер 38 за писывается нуль, а в триггер 39 - единица. При записи в

5

0

5

0

5

0

5

0

5

БЗУ триггер 38 блoкиpveт установку сигналом на входе 19 (Заявка ЗАП) триггера 35 в состояние, разрешающее выбор дополнительных блоков 2 и 3 памяти. Триггер 43 в этом случае выдает сигнал на вход 36 (Зап/Чт 1), разрешающий запись в блок 1, а триггер 45 - сигнал на входе 34 (FBI), так как сигнал 19 через элемент И-ИЛИ 42 устанавливает этот триггер 45 в соответствующее состояние.Старшие и младшие разряды адреса записи передаются без преобразований через мультиплексоры 7 и 6 и сумматоры 5 и 4 на адресные входы основного блока 1 памяти. Сигналом на входе 32 КЦ1 после окончания цикла записи в ячейку памяти триггер 45 возвращается в исходное состояние. При поступлении сигнала на вход 20 Заявка ЧТ триггер 43 устанавливается этим сигналом в состояние чтения из блока 1, а триггер 1, а триггер 44 - в состояние выбора дополнительных блоков 2 и 3 памяти. Формирование адресов поправок к координатам осуществляется аналогично режиму записи с преобразованием, а формирование адреса ячейки памяти блока 1 - как и в любом другом режиме буферизации.

Запись и чтение без преобразования. В триггер 38 и триггер 39 записываются нули, блокирующие установку триггера 44 в состояние выбора блоков 2 и 3. Триггер 45 устанавливается в состояние выбора блока 1 сигналами на входах 19 или 20, проходящими через элемент И-ИЛИ 42. Сброс триггера 45 осуществляется сигналом 32 (КЦ1). Адреса записи и чтения блока 1 формируются путем суммирования стр выходов мультиплексоров 6 и 7 соответственно с нулями с выходов блоков 2 и 3 на сумматорах 4 и 5.

Формула изобретения

Буферное запоминающее устройство, содержащее основной блок памяти, информационные входы и выходы которого являются соответственно первыми информационными входами и выходами устройства, первый и второй адресные входы основного блока памяти подключены к выходам соответственно первого и второго сумматоров, первые

91

входы которых подключены к информационным выходам cooTBerctBeHHO первого и второго дополнительных блоков памяти, первые адресные входы и информационные входы которых являются соответственно адресными и вторыми информационными входами устройства, вторые входы первого и второго сумматоров подключены к первым выходам соответственно второго и первого мультиплексоров, первые входы которых Подключены к первым выходам соответственно второго и первого счетчиков, вторые выходы которых подключены к вторым входам соответственно первого и второго мультиплексоров, третьи входы которых подключены к первому управляющему входу основного блока памяти и к первому выходу блока управления, второй и третий выходы которого подключены соответственно к первым и вторым управляющим входам первого и второго дополнительного блока памяти, четвертый выход блока управления подключен к второму управляющему входу основного блока памяти, управляющий выход которого подключен к первому входу блока управления, второй вход которого подключен к управляющему выходу первого дополнительного блок памяти, третий и четвертый входы блка управления подключены к входам соответственно первого и второго счетчиков и являются соответственно первым и вторым управляющими входа- ми устройства, входы группы блоОг

10

O

5

35

0

5

0

ка управления являются управляющими входами первой группы устройства, отличающееся тем, что, с целью повышения надежности, оно содержит третий и четвертый мультиплексоры, третий, четвертый, пятый и шестой сумматоры, первый и второй регистры, входы которых являются управляющими входами второй группы устройства, первые выходы первого и второго регистров подключены к первым входам соответственно третьего и четвертого сумматоров, вторые входы которых подключены к первым выходам соответственно первого и второго мультиплексоров и к первым входам соответственно третьего и четвертого мультиплексоров, вторые входы которых подключены к первым выходам соответственно пятого и шестого сумматоров, вторые выходы которых подключены к третьим входам соответственно, третьего и четвертого мультиплексоров, четвертые входы которых подключены к вторым выходам соответственно первого .и второго мультиплексоров и к первым входам соответственно пятого и шестого сумматоров, вторые входы которых подключены к вторым входам соответственно первого и второго регистров, третьи выходы которых подключены к пятым входам соответственно третьего и четвертого мультиплексоров, шестые входы которых подключены к выходам соответственно третьего и четвертого сумматоров.

Or о ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Буферное запоминающее устройство для блоков отображения информации | 1986 |

|

SU1411830A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании систем ввода и предварительной обработки цифровых изображений в вычислительные системы на основе буферных запоминающих устройств. Цель изобретения - повышение надежности буферного запоминающего устройства. Устройство содержит основной блок 1 памяти, дополнительные блоки 2 и 3 памяти,сумматоры 4 и 5, мультиплексоры 6 и 7, регистры 8 и 9, счетчики 10 и 11, сумматоры 12-15, мультиплексоры 16 и 17, блок 18 управления, управляющие входы 19-22, адресные входы 23, Залвна ,, У( ff 2) (Л с 1C 00 о 4 СП

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-30—Публикация

1985-09-11—Подача