.Изобретение относится к вычислительной технике и может быть исполь- при построении программируемы контроллеров, устройств и систем управления ЭВМ, АСУ технологическими пгтоцессами.

Цель изобретения - расширение функциональных возможностей устройства за счет репликации множества формируемых команд управления,

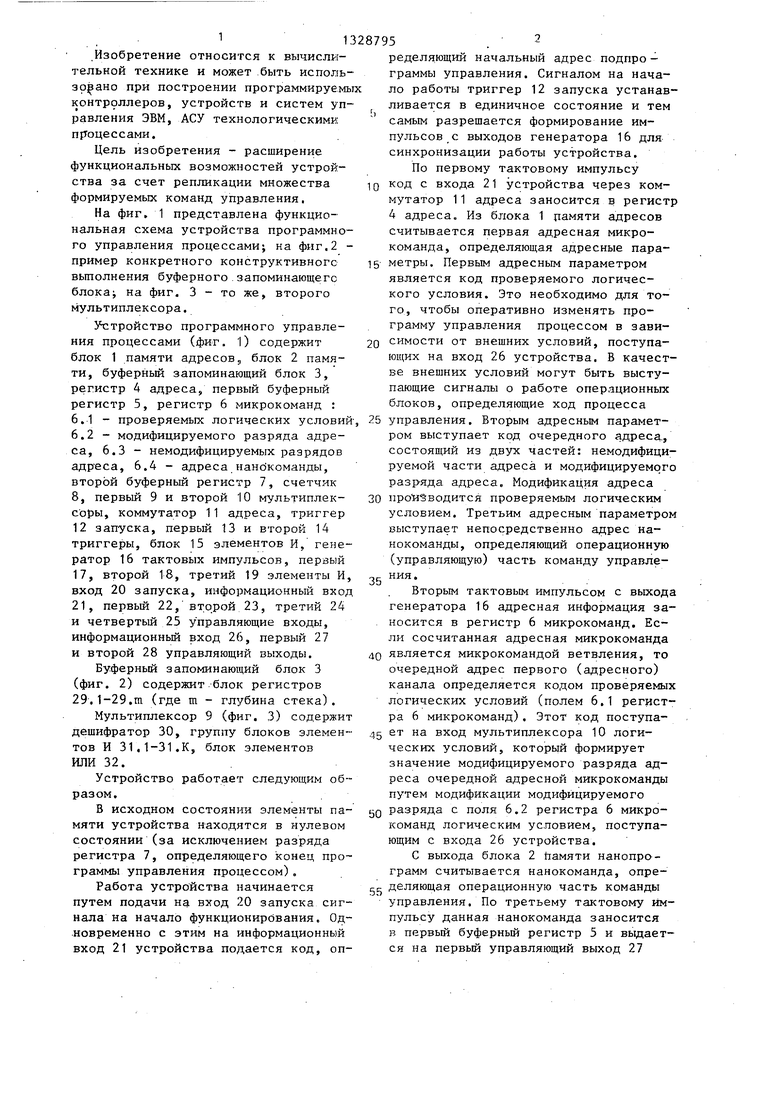

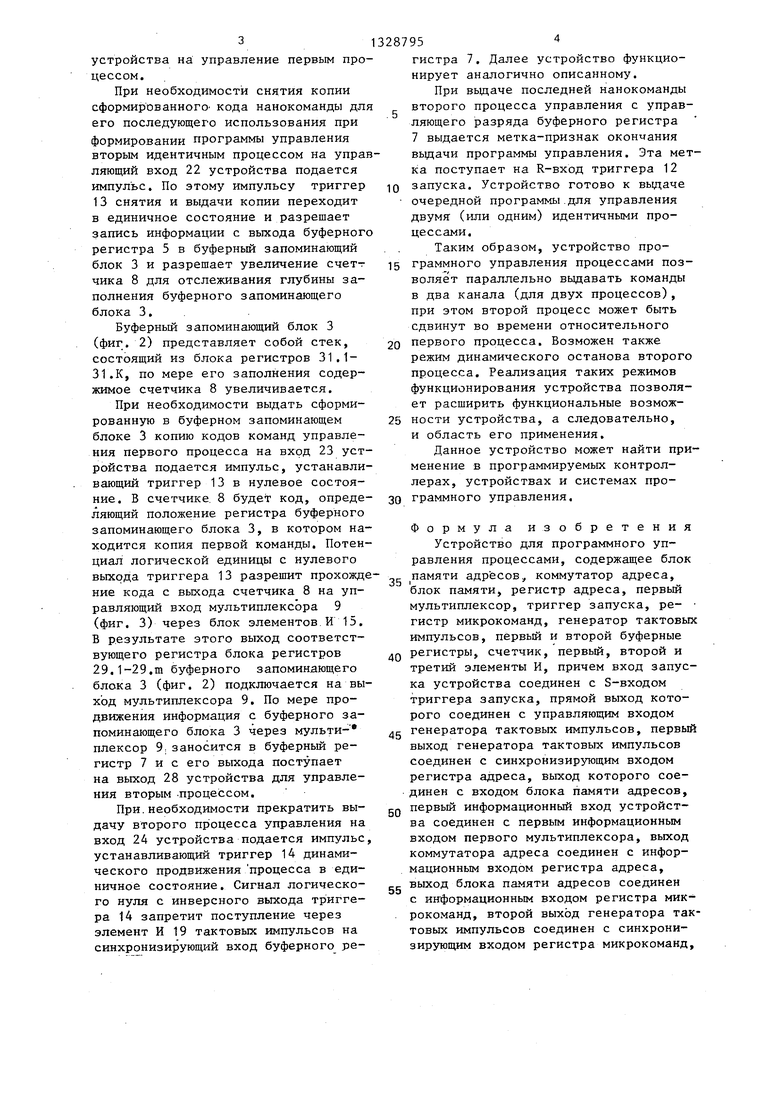

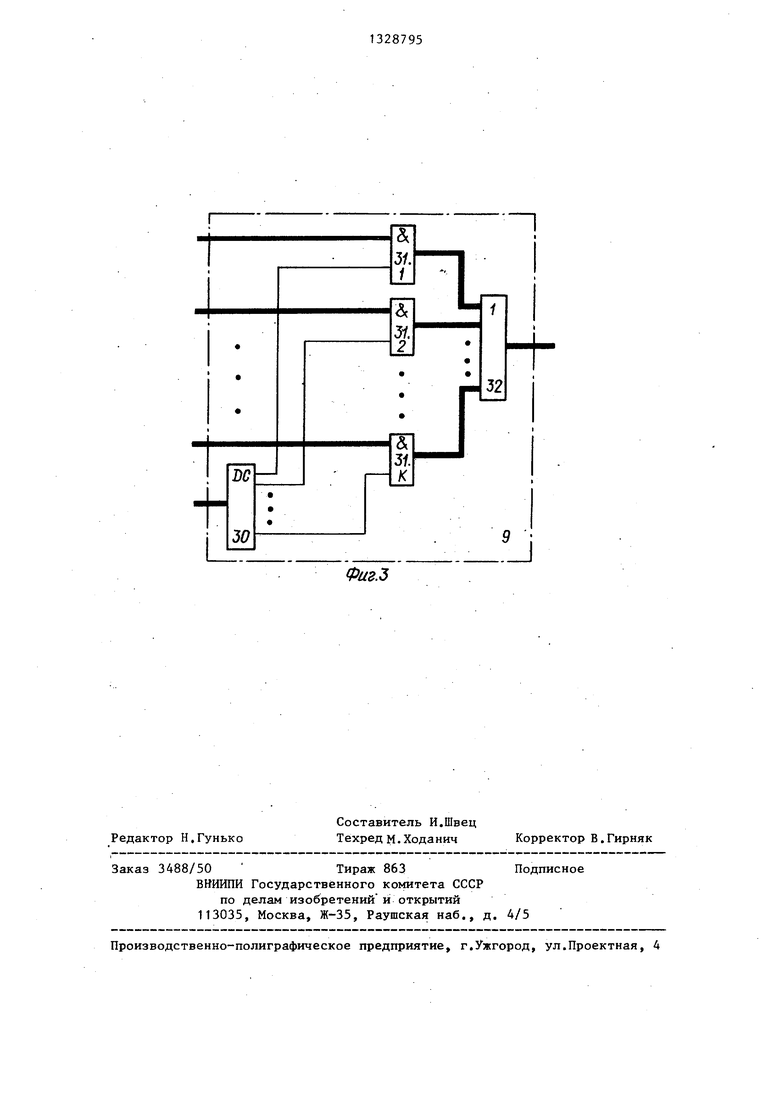

На фиг, 1 представлена функциональная схема устройства программного управления процессами; на фиг.2 - пример конкретного конструктивного вьшолнения буферного запоминающего блокад на фиг. 3 - то же, второго мультиплексора.

Устройство программного управления процессами (фиг. 1) содержит блок 1 памяти адресов, блок 2 памяти, буферный запоминающий блок 3, регистр 4 адреса, первый буферный регистр 5, регистр 6 микрокоманд :

6.1 - проверяемых логических условий, 25 управления. Вторым адресным парамет6.2 - модифицируемого разряда адреса, 6.3 - немодифицируемых разрядов адреса, 6.4 - адреса нано команды, второй буферный регистр 7, счетчик 8, первый 9 и второй 10 мультиплексоры, коммутатор 11 адреса, триггер 12 запуска, первый 13 и второй 14 триггеры, блок 15 элементов И, генератор 16 тактовых импульсов, первый 17, второй 18, третий 19 элементы И, вход 20 запуска, информационный вход 21, первый 22, второй 23, третий 24 и четвертый 25 Управляющие входы, информационный вход 26, первый 27 и второй 28 управляющий выходы.

Буферный запоминающий блок 3 (фиг. 2) содержит.блок регистров 29,1-29.m (где m - глубина стека).

Мультиплексор 9 (фиг. 3) содержит дешифратор 30, группу блоков элементов И 31.1-31.К, блок элементов ИЛИ 32.

Устройство работает следующим образом.

В исходном состоянии элементы памяти устройства находятся в нулевом состоянии (за исключением разряда регистра 7, определяющего конец программы управления процессом).

Работа устройства начинается путем подачи на вход 20 запуска сигнала на начало функционирования. Од- .новременно с этим на информационный вход 21 устройства подается код, определяющий начальный адрес подпрограммы управления. Сигналом на начало работы триггер 12 запуска устанав- ливает ся в единичное состояние и тем самым разрешается формирование импульсов с выходов генератора 16 для синхронизации работы устройства. По первому тактовому импульсу

код с входа 21 устройства через коммутатор 11 адреса заносится в регистр 4 адреса. Из блока 1 памяти адресов считывается первая адресная микрокоманда, определяющая адресные параметры. Первым адресным параметром является код проверяемого логического условия. Это необходимо для того, чтобы оперативно изменять программу управления процессом в зависимости от условий, поступающих на вход 26 устройства. В качестве внеиших условий могут быть выступающие сигналы о работе операционных блоков, определяющие ход процесса

ом выступает код очередного адреса., состоящий из двух частей: немодифицируемой части г1дрес.а и модифицируемого разряда адреса. Модификация адреса

ПРОИЗВОДИТСЯ проверяемым логическим условием. Третьим адресным параметром выступает непосредственно адрес на- нокоманды, определяющий операционную (управляющую) часть команду управления.

Вторым тактовым импульсом с выхода генератора 16 адресная информация заносится в регистр 6 микрокоманд. Если сосчитанная адресная микрокоманда

является микрокомандой ветвления, то очередной адрес первого (адресного) канала определяется кодом проверяемых логических условий (полем 6.1 регистра 6 микрокоманд). Этот код поступабт на вход мультиплексора 10 логических условий, который формирует значение модифицируемого разряда адреса очередной адресной микрокоманды путем модификации модифицируемого

разряда с поля 6.2 регистра 6 микрокоманд логическим ус.повием, поступающим с входа 26 устройства.

С выхода блока 2 памяти нанопро- грамм считывается нанокоманда, определяющая операционную часть команды управления. По третьему тактовому импульсу данная нанокоманда заносится в первый буферный регистр 5 и вьщает- ся на первый управляющий выход 27

3

устройства на управление первым процессом.

При необходимости снятия копии сформированного кода нанокоманды дл его последующего использования при формировании программы управления вторым идентичным процессом на упраляющий вход 22 устройства подается импульс. По этому импульсу триггер 13 снятия и выдачи копии переходит в единичное состояние и разрешает запись информации с выхода буферног регистра 5 в буферный запоминающий блок 3 и разрешает увеличение счетчика 8 для отслеживания глубины заполнения буферного запоминающего блока 3.

Буферный запоминающий блок 3 (фиг. 2) представляет собой стек, состоящий из блока регистров 31.1- 31.К, по мере его заполнения содержимое счетчика 8 увеличивается.

При необходимости выдать сформированную в буферном запоминающем блоке 3 копию кодов команд управления первого процесса на вход 23 устройства подается импульс, устанавливающий триггер 13 в нулевое состояние. В счетчике. 8 будет код, определяющий положение регистра буферного запоминающего блока 3, в котором находится копия первой команды. Потенциал логической единицы с нулевого выхода триггера 13 разрешит прохождение кода с выхода счетчика 8 на управляющий вход мультиплексора 9 (фиг. 3) через блок элементов И 15. В результате этого выход соответствующего регистра блока регистров 29.1-29.m буферного запоминающего блока 3 (фиг. 2) подключается на выход мультиплексора 9. По мере продвижения информация с буферного запоминающего блока 3 через мульти- плексор 9, заносится в буферный регистр 7 и с его выхода поступает на выход 28 устройства для управления вторым -процессом.

При.необходимости прекратить выдачу второго пр оцесса управления на вход 24 устройства подается импульс, устанавливающий триггер 14 динамического продвижения процесса в единичное состояние. Сигнал логического нуля с инверсного выхода триггера 14 запретит поступление через элемент И 19 тактовых импульсов на синхронизирующий вход буферного ре287954

гистра 7. Далее устройство функционирует аналогично описанному.

При выдаче последней нанокоманды второго процесса управления с управляющего разряда буферного регистра 7 выдается метка-признак окончания выдачи программы управления. Эта метка поступает на R-вход триггера 12

10 запуска. Устройство готово к выдаче очередной программы.для управления двумя (или одним) идентичными процессами.

. Таким образом, устройство про15 граммного управления процессами позволяет параллельно выдавать команды в два канала (для двух процессов), при этом второй процесс может быть сдвинут во времени относительного

20 первого процесса. Возможен также

режим динамического останова второго процесса. Реализация таких режимов функционирования устройства позволяет расширить функциональные возмож25 ности устройства, а следовательно, и область его применения.

Данное устройство может найти применение в программируемых контроллерах, устройствах и системах про30 граммного управления.

Формула изобретения

Устройство для программного управления процессами, содержащее блок

21- памяти адресов, коммутатор адреса, блок памяти, регистр адреса, первый мультиплексор, триггер запуска, ре- гистр микрокоманд, генератор тактовых импульсов, первый и второй буферные

дд регистры, счетчик, первый, второй и третий элементы И, причем вход запуска устройства соединен с S-входом триггера запуска, прямой выход которого соединен с управляющим входом

g генератора тактовых импульсов, первый выход генератора тактовых импульсов соединен с синхронизирующим входом регистра адреса, выход которого соединен с входом блока памяти адресов,

p первый информационный вход устройства соединен с первым информационным входом первого мультиплексора, выход коммутатора адреса соединен с информационным входом регистра адреса,

g выход блока памяти адресов соединен

с информационным входом регистра мик- . рокоманд, второй выход генератора тактовых импульсов соединен с синхронизирующим входом регистра микрокоманд.

первый выход которого соединен с управляющим входом первого мультиплексора, второй выход регистра микро- 1 оманд соединен с вторым информационным входом первого мультиплексора, адресный выход регистра микрокоманд соединен с входами адреса первого информационного входа коммутатора адреса, выход первого мультиплексора соединен с входом адреса первого информационного входа коммутатора адреса, второй информационный вход устройства соединен с вторым информационным входом коммутатора адреса,

выход адреса регистра микрокоманд coe-J5 тьего элемента И, выход которого соединен с входом блока памяти, выход которого соединен с информационным входом первого буферного регистра, синхронизирующий .вход которого соединен с третьим выходом генератора тактовых импульсов, выход второго буферного регистра соединен с прямым и инверсными входами коммутатора адреса и с R-входом триггера запуска

динен с синхронизирующим входом второго буферного регистра, первый управляющий- вход устройства соединен с S-входом первого триггера, прямой 20 выход которого соединен с вторым вхо дом второго элемента И, инверсный выход второго триггера соединен с вторым входом первого элемента И, второй управляющий вход устройства

выход первого буферного регистра сое- 25 соединен с R-входом первого тригге- динен с первым управляющим выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства

ра, инверсный выход которого соединен с вторым входом третьего элемента И, третий управляющий вход устройства соединен с S-входом второго

за счет репликации множества формиру- 30 триггера, единичный выход которого

емых команд управления, в него введены буферный запоминающий блок, второй мультиплексор, блок элементов И, первый триггер, второй триггер, причем выход первого буферного регистра 35 ментов И, четвертый управляющий вход

соединен с информационным входом буферного -запоминающего блока, выходы которого соединены с соответствующими информационными входами второго

мультиплексора, выход которого соеди- 40 ного регистра соединен с вторым упнен с информационным входом второго

КО

RG

D

г

С

23.2

буферного регистра, четвертый выход генератора тактовых импульсов соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с синхронизирующим входом буферного запоминающего блока, выход второго элемента И соединен с суммирующим входом счетчика, выход которого соединён с информационньш входом блока элементов И, выход блока элементов И соединен с управляющим входом второго мультиплексора, пятый выход генератора тактовых импульсов соединен с первым -входом трединен с синхронизирующим входом второго буферного регистра, первый управляющий- вход устройства соединен с S-входом первого триггера, прямой выход которого соединен с вторым входом второго элемента И, инверсный выход второго триггера соединен с вторым входом первого элемента И, второй управляющий вход устройства

соединен с R-входом первого тригге-

ра, инверсный выход которого соединен с вторым входом третьего элемента И, третий управляющий вход устройства соединен с S-входом второго

соединен с инверсным управляющим входом блока элементов И, инверсньй выход первого триггера соединен с прямым управляющим входом блока элеустройства соединен с R-входом второго триггера, инверсный выход которого соединен с третьим входом третьего элемента И, выход второго буферравляющим выходом устройства.

29.Ы

Фиг.

Редактор Н.Гунько

Составитель И.Швец Техред м. Ходанич

Заказ 3488/50 Тираж 863Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор В.Гирняк

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении программируемых контроллеров устройств и систем программного управления, в средствах автоматизации технологическими процессами. Целью изобретения является расширение функциональных возможностей устройства за счет репликации множества формируемых команд управления. Устройство для программного управления процессами содержит блок 1 памяти адресов, блок 2 памяти, буферный запоминающий блок 3, регистр 4 адреса, первый буферный регистр 5, регистр 6 микрокоманд, счетчик 8, первый 9 и второй 10 мультиплексоры, коммутатор 11 адреса, триггер 12 запуска, триггеры 13 и 14, блок 15 элементов И, генератор 16 тактовых импульсов, элементы И 17, 18 и 19. Цель достигается тем, что в устройство введены буферный запоминающий блок, второй мультиплексор 10, блок 15 элементов И, первый триггер 13, второй триггер 14, Данное устройство обеспечивает возможность осуществления параллельного управления процессами, например процессами приема и обработки в программируемых контроллерах. 3 ил. с (Л

| Микропрограммное устройство управления | 1977 |

|

SU666984A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство микропрограммного управления | 1980 |

|

SU903877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-07—Публикация

1986-02-25—Подача