Изобретение относитсяк вычислительной технике и предназначено для использования в быстродействующих вычислительных устройствах конвейерного типа, осуществляющих обработку числовой информации в непозиционном коде с контролем ощибок.

Известно устройство для декодирования, содержащее операционный и запоминающий регистры, блоки памяти констант нулевизации, дещифраторы, блоки памяти констант нулевизации ощибок, сумматор, переключатели и логические элементы 1.

Недостатком устройства является его низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для обнаружения и исправления ощибок в непозиционном коде, которое содержит входной регистр, входы которого являются входами устройства, блок свертки по контрольным модулям, входы которого подключены к первому выходу входного регистра, сумматоры по контрольным модулям, по входам подключенные к второму и третьему выходам входного регистра и выходам блока модульной свертки по контрольным 1модулям, блок памяти ощибок, входы которого соединены с выходами сумматоров по контрольным модулям, и блок сумматоров коррекции по модулям системы счисления, первый вход которого подключен к выходу блока памяти ощибок, второй, третий и четвертый входы - соответственно к первому, второму и третьему выходам входного регистра, а выход является выходом устройства. Устройство обнаруживает и исправляет любую однократную ошибку, происщедщую по информационному или контрольному модулям 2.

Недостаток известного устройства заключается в том, что реализуемый в нём способ формирования контрольных разрядов затрудняет применение устройства для контроля арифметических операций. Кроме того, оно не может работать в конвейерном режиме.

Цель изобретения - повыи;ение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для исправления ощибок в непозиционном коде, содержащее группу входных регистров, блок п-амяти ощибок, группу сумматоров коррекции, причем входы входных регистров группы являются входами устройства, введены управляющий регистр, коммутатор, группа узлов задержки, группа выходных регистров и два сумматора по первому и второму контрольным модулям, причем выходы входных регистров группы через соответствующие узлы задержки группы соединены с первыми информационными входами соответствующих сумматоров коррекции группы, выходы которых соединены с входами соответствующих выходных регистров группы, выходы которых являются выходами устройства, входы.сумматора по первому контрольному модулю соединены соответственно с выходами всех входных регистров группы, кроме (К + 2)-го (где (K-i-2) - число входных регистров в группе), входы сумматора по второму контрольному модулю соединены соответственно с выходами всех входных регистров группы, кроме (К-Ь 1)-го, выходы сумматоров по первому и второму контрольным модулям соединены с соответствующими входами группы адресных входов блока памяти ощибок, выходы которого соединены с соответствующими входами управляющего регистра, выходы разрядов признаков коррекции которого соединены с информационными входами коммутатора, управляющий вход которого соединен с выходами разрядов признаков адреса управляющего регистра, выходы коммутатора

0 соединены с вторыми входами соответствующих сумматоров коррекции.

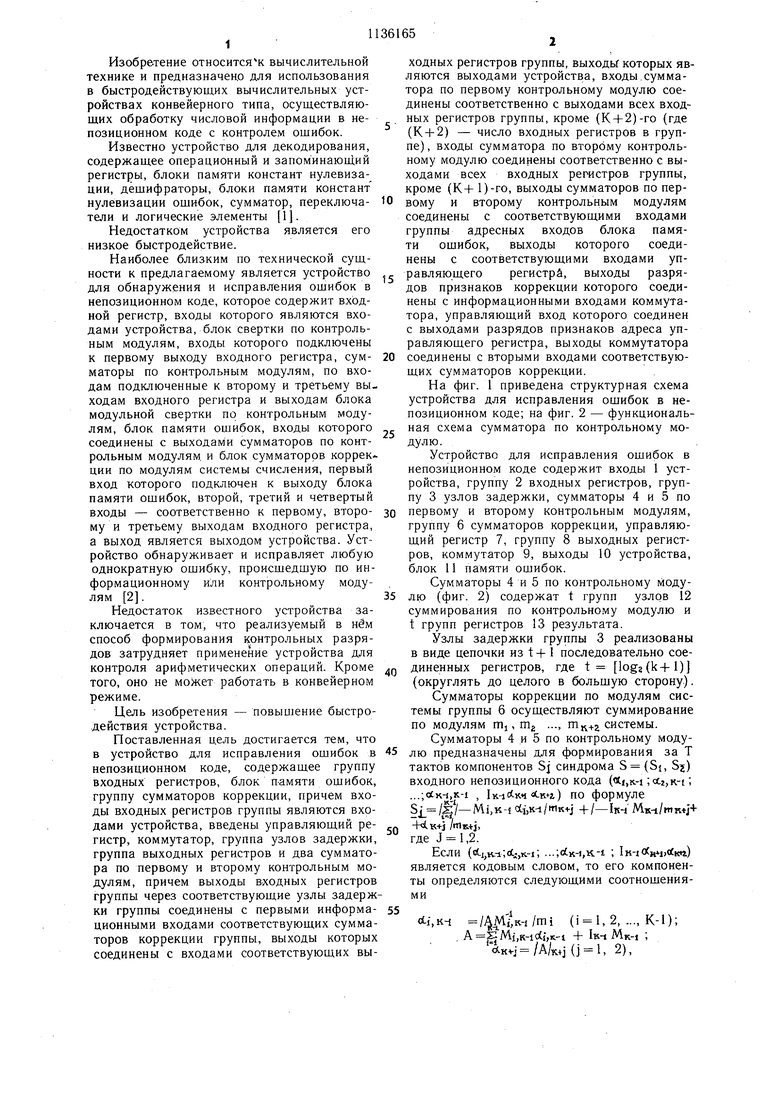

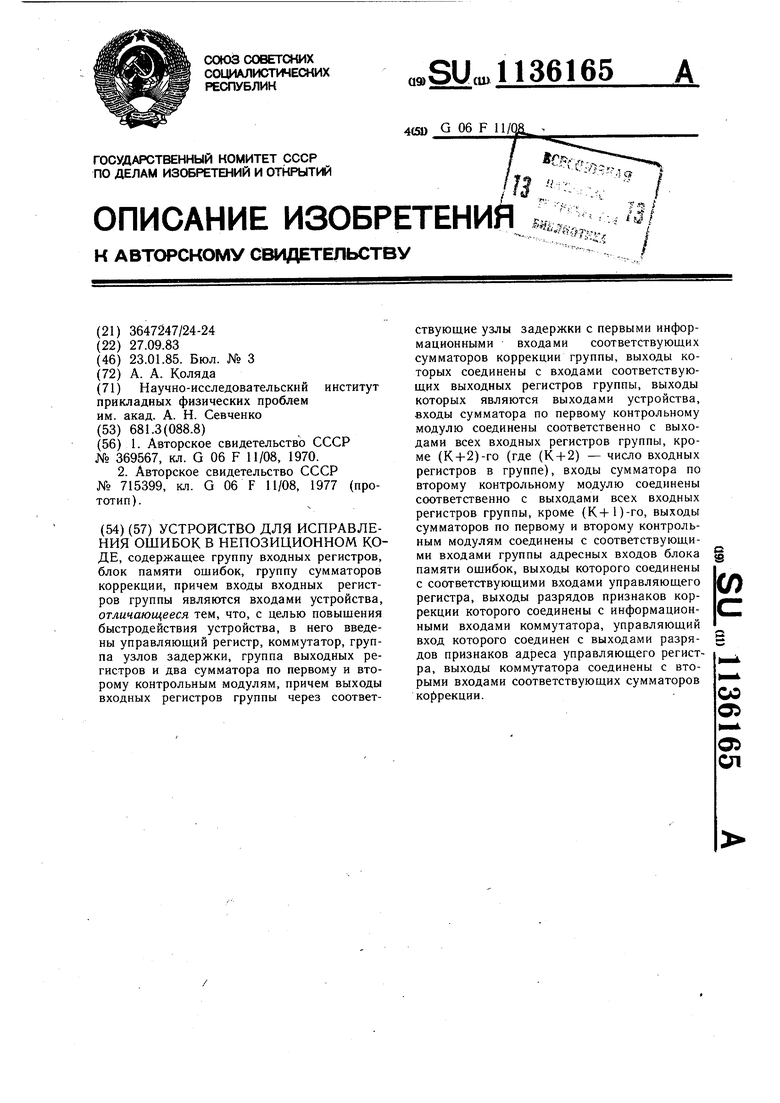

На фиг. 1 приведена структурная схема устройства для исправления ошибок в непозиционном коде; на фиг. 2 - функциональчая схема сумматора по контрольному модулю.

Устройство для исправления ощибок в непозиционном коде содержит входы 1 устройства, группу 2 входных регистров, группу 3 узлов задержки, сумматоры 4 и 5 по

0 первому и второму контрольным модулям, группу 6 сумматоров коррекции, управляющий регистр 7, группу 8 выходных регистров, коммутатор 9, выходы 10 устройства, блок 11 памяти ошибок.

Сумматоры 4 и 5 по контрольному модулю (фиг. 2) содержат t групп узлов 12 суммирования по контрольному модулю и t групп регистров 13 результата.

Узлы задержки группы 3 реализованы в виде цепочки из t-f 1 последовательно соеQ диненных регистров, где t logs(k-}-l) (округлять до целого в большую сторону). Сумматоры коррекции по модулям системы группы 6 осуществляют суммирование

т

по модулям mj,т

системы.

к+г

Сумматоры 4 и 5 по контрольному модулю предназначены для формирования за Т тактов компонентов Sj синдрома S (Sj, Sj) входного непозиционного кода (Xi,t-i;ос,R-I ; ...;оСк-1,к-1 , o(-Rtj,) по формуле Sj /g/-Mi,K-i oCiKi/iTiK+j -Ь/-IK-I Mn-i/mKtJ- -WK+J /n1l«j,

где J l,2.

Если (A.i,K.-i:;di::,Ti-t ...;c(.K-i,«.-i ; 1к-1«кЧ)ОС|с.г) является кодовым словом, то его компоненты определяются следующими соотнощениями

d-i,к-1 /4MtK-i /mi (i 1, 2, ..., К-1); ,K-idj,K-t + ЫМк- ;

.J(J I, 2),

гдеМ1,.,%1 (i l, 2, .... К-1); Мк-1

А - число из рабочего диапазона системы счисления;

mt, Шг упорядоченный по возрастанию набор модулей системы, причем + К-2 (р- фиксированное натуральное число).

Устройство работает следующим образом.

Непозиционный код (ii,K-i;«i,K-i; ...;а.л-1,.-1, 1к-1,к+,«1к4г), подлежащий контролю, поступает через входы 1 устройства на входные регистры группы 2, с выходов которых он поступает на входы соответствующих узлов задержки группы 3 и на входы сумматоров 4 и 5 по первому и второму контрольным модулям. Сумматоры 4 и 5 по первому и второму контрольным модулям через t тактов сформируют синдром S (Si, 5г) кода.

На (t + l)-M такте компоненты Sj, S синдрома поступают на входы группы адресных входов блока 11 памяти ошибок, с выхода которого считывается на управляющий регистр 7 код коррекции Д и код номера i) искаженной цифры.

На (t + 2)-M такте работы устройства на первые входы сумматоров коррекции по модулям системы группы 6 поступает входной код с выходов узлов задержки группы 3, а на вторые входы - код коррекции с выхода коммутатора 9.

С выхода коммутатора 9 поступает код коррекции Av ..на второй вход сумматора группы 6, соответствующий номеру ) искаженной Цифры, и нули на все остальные сумматоры группы 6. В результате исправленный код поступает на группу 8 выходных регистров.

Таким образом, предлагаемое устройство по заполнении узлов задержки группы 3 позволяет осуществлять контроль и исправление входных кодов за один такт работы

устройства благодаря конвейерному принципу обработки кодов, что приводит к повышению быстродействия устройства.

ii j

/5

/Z

13

I...

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1979 |

|

SU862143A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| УСТРОЙСТВО СПЕКТРАЛЬНОГО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК В КОДАХ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ | 2005 |

|

RU2301441C2 |

| Устройство для формирования позиционных признаков непозиционного кода | 1980 |

|

SU968800A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В НЕПОЗИЦИОННОМ КОДЕ, содержащее группу входных регистров, блок памяти ошибок, группу сумматоров коррекции, причем входы входных регистров группы являются входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены управляющий регистр, коммутатор, группа узлов задержки, группа выходных регистров и два сумматора по первому и второму контрольным модулям, причем выходы входных регистров группы через соответствующие узлы задержки с первыми информационными входами соответствующих сумматоров коррекции группы, выходы которых соединены с входами соответствующих выходных регистров группы, выходы которых являются выходами устройства, входы сумматора по первому контрольному модулю соединены соответственно с выходами всех входных регистров группы, кроме (К4-2)-го (где (К+ 2) - число входных регистров в группе), входы сумматора по второму контрольному модулю соединены соответственно с выходами всех входных регистров группы, кроме (К+1)-го, выходы сумматоров по первому и второму контрольным модулям соединены с соответствующиi ми входами группы адресных входов блока памяти ошибок, выходы которого соединены (Л с соответствующими входами управляющего регистра, выходы разрядов признаков корС рекции которого соединены с информационными входами коммутатора, управляющий вход которого соединен с выходами разрядов признаков адреса управляющего регистра, выходы коммутатора соединены с вторыми входами соответствующих сумматоров со о коррекции. 05 сд

fZ

/5

и

/Z

12

/J

и

/z

j

ф4/г.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 0 |

|

SU369567A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для перемещения транспортных средств | 1977 |

|

SU715399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1983-09-27—Подача