Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах, работающих в Р-ичных системах счисления (где Р - целое положительное число, причем ).

Цель изобретения - расширение области применения устройства путем алгебраического суммирования чисел.

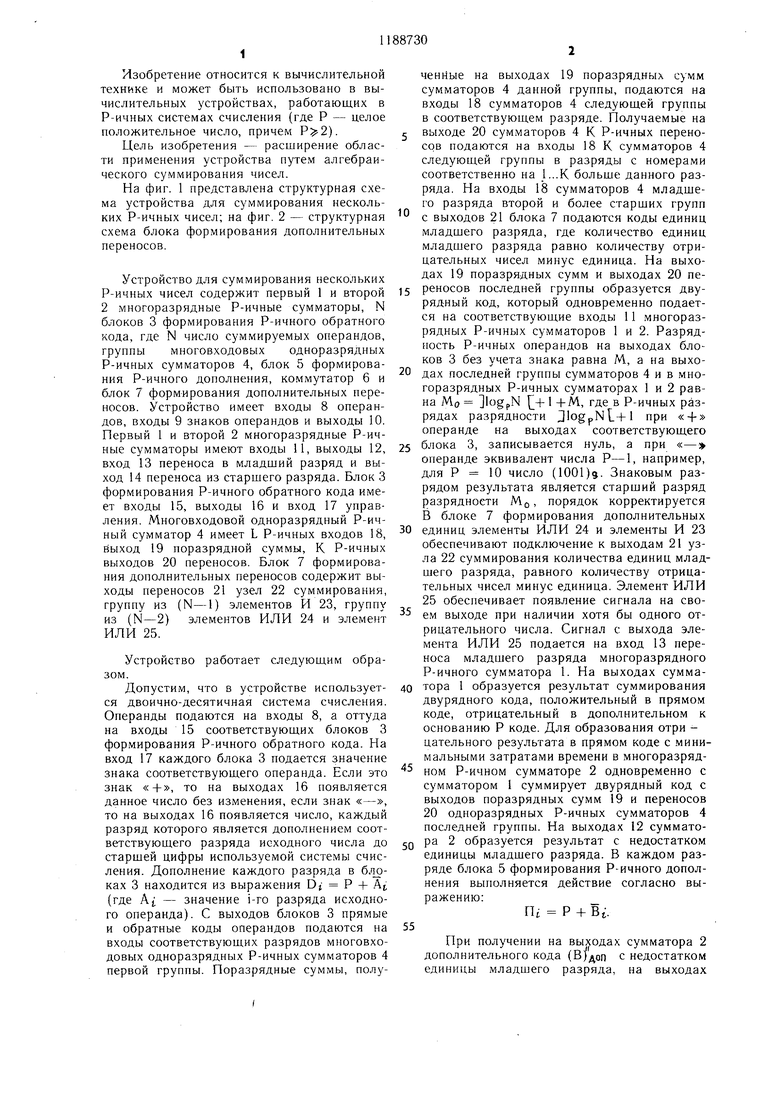

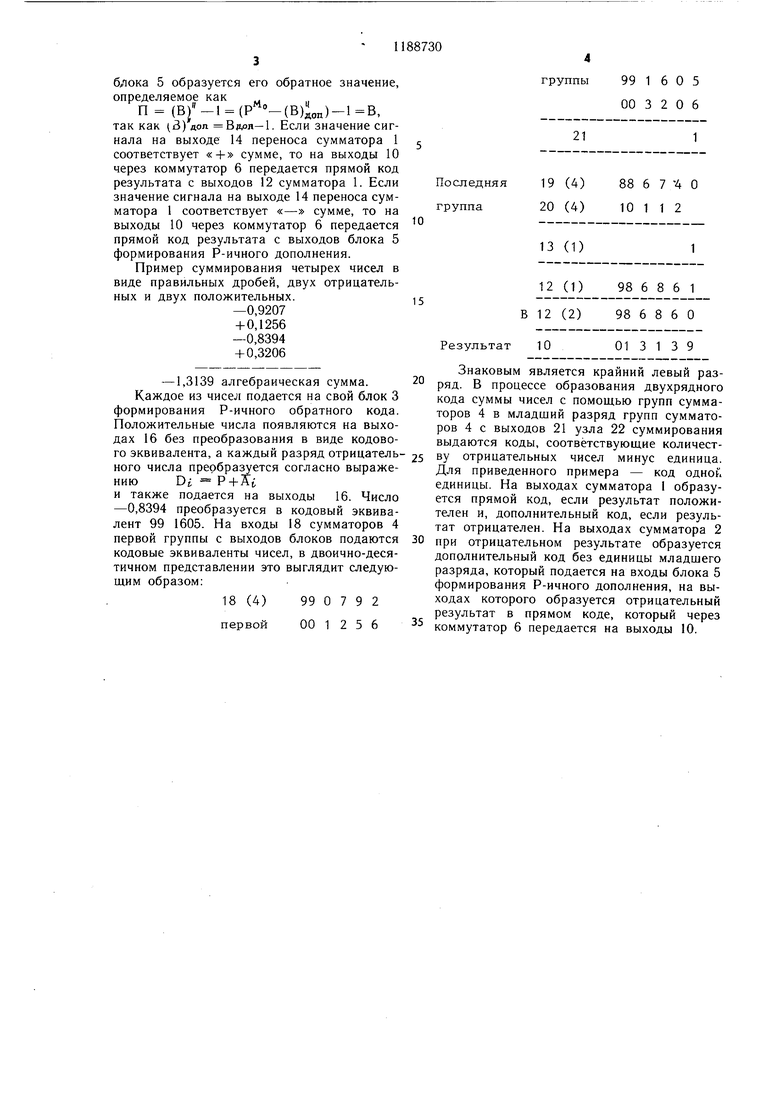

На фиг. 1 представлена структурная схема устройства для суммирования нескольких Р-ичных чисел; на фиг. 2 - структурная схема блока формирования дополнительных переносов.

Устройство для суммирования нескольких Р-ичных чисел содержит первый 1 и второй 2 .многоразрядные Р-ичные сумматоры, N блоков 3 формирования Р-ичного обратного кода, где N число суммируемых операндов, группы многовходовых одноразрядных Р-ичных сумматоров 4, блок 5 формирования Р-ичного дополнения, коммутатор 6 и блок 7 формирования дополнительных переносов. Устройство имеет входы 8 операндов, входы 9 знаков операндов и выходы 10. Первый 1 и второй 2 многоразрядные Р-ичные сумматоры имеют входы 11, выходы 12, вход 13 переноса в младший разряд и выход 14 переноса из старшего разряда. Блок 3 формирования Р-ичного обратного кода имеет входы 15, выходы 16 и вход 17 управления. Многовходовой одноразрядный Р-ичный сумматор 4 имеет L Р-ичных входов 18, выход 19 поразрядной суммы, К Р-ичных выходов 20 переносов. Блок 7 формирования дополнительных переносов содержит выходы переносов 21 узел 22 суммирования, группу из (N-1) элементов И 23, группу из (N-2) элементов ИЛИ 24 и элемент ИЛИ 25.

Устройство работает следуюпдим образом.

Допустим, что в устройстве используется двоично-десятичная система счисления. Операнды подаются на входы 8, а оттуда на входы 15 соответствующих блоков 3 формирования Р-ичного обратного кода. На вход 17 каждого блока 3 подается значение знака соответствующего операнда. Если это знак «+, то на выходах 16 появляется данное число без изменения, если знак «-, то на выходах 16 появляется число, каждый разряд которого является дополнением соответствующего разряда исходного числа до старшей цифры используемой системы счисления. Дополнение каждого разряда в б.токах 3 находится из выражения О Р + .i (где AI - значение i-ro разряда исходного операнда). С выходов блоков 3 прямые и обратные коды операндов подаются на входы соответствующих разрядов многовходовых одноразрядных Р-ичных сумматоров 4 первой группы. Поразрядные суммы, полученные на выходах 19 поразрядных сумм сумматоров 4 данной группы, подаются на входы 18 сумматоров 4 следующей группы в соответствующем разряде. Получаемые на

выходе 20 сумматоров 4 К Р-ичных переносов подаются на входы 18 К сумматоров 4 следующей группы в разряды с номерами соответственно на 1...К больше данного разряда. На входы 18 сумматоров 4 младшего разряда второй и более старщих групп с выходов 21 блока 7 подаются коды единиц младшего разряда, где количество единиц младшего разряда равно количеству отрицательных чисел минус единица. На выходах 19 поразрядных сумм и выходах 20 переносов последней группы образуется двурядный код, который одновременно подается на соответствующие входы 11 многоразрядных Р-ичных сумматоров 1 и 2. Разрядность Р-ичных операндов на выходах блоков 3 без учета знака равна М, а на выходах последней группы сумматоров 4 и в многоразрядных Р-ичных сумматорах 1 и 2 равна MO logpN + 1 +М, где в Р-ичных разрядах разрядности JlogpNL-1-l при «-f операнде на выходах соответствующего

блока 3, записывается нуль, а при «- операнде эквивалент числа Р-1, например, для Р 10 число (1001)з. Знаковым разрядом результата является старщий разряд разрядности MO, порядок корректируется В блоке 7 формирования дополнительных

единиц элементы ИЛИ 24 и элементы И 23 обеспечивают подключение к выходам 21 узла 22 суммирования количества единиц младшего разряда, равного количеству отрицательных чисел минус единица. Элемент ИЛИ 25 обеспечивает появление сигнала на своем выходе при наличии хотя бы одного отрицательного числа. Сигнал с выхода элемента ИЛИ 25 подается на вход 13 переноса младшего разряда многоразрядного Р-ичного сумматора 1. На выходах сумматора 1 образуется результат суммирования двурядного кода, положительный в прямом коде, отрицательный в дополнительном к основанию Р коде. Для образования отри цательного результата в прямом коде с минимальными затратами времени в многоразрядном Р-ичном сумматоре 2 одновременно с сумматором 1 суммирует двурядный код с выходов поразрядных сумм 19 и переносов 20 одноразрядных Р-ичных сумматоров 4 последней группы. На выходах 12 сумматоpa 2 образуется результат с недостатком единицы младшего разряда. В каждом разряде блока 5 формирования Р-ичного дополнения выполняется действие согласно выражению:

П P + Bi.

При получении на выходах сумматора 2 дополнительного кода (В/доп с недостатком единицы младшего разряда, на выходах б/1ока 5 образуется его обратное значение, определяемое как П (В)-1 (Р-(В)о„), так как 3) доп Вдоп-1. Если значение сигнала на выходе 14 переноса сумматора 1 соответствует «+ сумме, то на выходы 10 через коммутатор 6 передается прямой код результата с выходов 12 сумматора 1. Если значение сигнала на выходе 14 переноса сумматора 1 соответствует «- сумме, то на выходы 10 через коммутатор 6 передается прямой код результата с выходов блока 5 формирования Р-ичного дополнения. Пример суммирования четырех чисел в виде правильных дробей, двух отрицательных и двух положительных. -0,9207 -Ь 0,1256 -0,8394 + 0,3206 -1,3139 алгебраическая сумма. Каждое из чисел подается на свой блок 3 формирования Р-ичного обратного кода. Положительные числа появляются на выходах 16 без преобразования в виде кодового эквивалента, а каждый разряд отрицательного числа преобразуется согласно выражениюDi P+Ai и также подается на выходы 16. Число -0,8394 преобразуется в кодовый эквивалент 99 1605. На входы 18 сумматоров 4 первой группы с выходов блоков подаются кодовые эквиваленты чисел, в двоично-десятичном представлении это выглядит следующим образом: 18 (4)99 О 7 9 2 00 1 2 5 6 первой 99 1 6 о 5 группы 00 3 2 О 6 13 (1) 98 6 8 6 1 В 12 (2) 98 6 8 6 О 01 3 1 3 9 Результат Знаковым является крайний левый разряд. В процессе образования двухрядного кода суммы чисел с помощью групп сумматоров 4 в младший разряд групп сумматоров 4 с выходов 21 узла 22 суммирования выдаются коды, соответствующие количеству отрицательных чисел минус единица. Для приведенного примера - код одно, единицы. На выходах сумматора 1 образуется прямой код, если результат положителен и, дополнительный код, если результат отрицателен. На выходах сумматора 2 при отрицательном результате образуется дополнительный код без единицы младщего разряда, который подается на входы блока 5 формирования Р-ичного дополнения, на выходах которого образуется отрицательный результат в прямом коде, который через коммутатор 6 передается на выходы 10.

1 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Многоразрядный сумматор по модулю | 2024 |

|

RU2831626C1 |

| Многовходовой сумматор | 1989 |

|

SU1679483A1 |

| Устройство для умножения по модулю М=2 @ -1 | 1986 |

|

SU1383339A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Сумматор п-разрядных комплексныхчиСЕл | 1979 |

|

SU817699A1 |

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ НЕСКОЛЬКИХ Р-ИЧНЫХ ЧИСЕЛ, содержащее первый и второй многоразрядные Р-ичные сумматоры, отличающееся тем, что, с целью расширения области применения путем алгебраического суммирования чисел, оно содержит N блоков формирования Р-ичного обратного кода (где N - число суммируемых операндов), группы многовходовых одноразрядных Р-ичных сумматоров, блок формирования Р-ичного дополнения, коммутатор и блок формирования дополнительных переносов, содержащий узел суммирования, группу элементов И, группу элементов ИЛИ и элемент ИЛИ, входы каждого многовходового одноразрядного Р-ичного сумматора первой группы соединены с одноименными разрядами выходов соответствующих блоков формирования Р-ичного обратного кода, входы которых соединены с входами устройства, выход поразрядной суммы многовходового одноразрядного Р-ичного сумматора i-ro разряда каждой группы соединен с входом многовходового одноразрядного Р-ичного сумматора того же разряда следулощей группы, а выходы переносов с первого по 11-й где ii log pL х(Р-1) -1 (где L - число входов данного многовходового одноразрядного Р-ичного сумматора), соединены с входами многовходовых одноразрядных Р-ичных сумматоров с (i + l)-ro по (i-f k)-ii разряд следующей группы, входы переносов многовходовых од « этлкдя /3 «HBjficv-eiOi норазрядных Р-и.чных сумматоров младщих разрядов всех групп, кроме первой, соединены с соответствующими выходами узла суммирования, а выходы поразрядной суммы и переноса многовходовых одноразрядных Р-ичных сумматоров последней группы соединены соответственно с первым и вторым входами соответствующих разрядов первого и второго многоразрядных Р-ичных сумматоров, вход переноса младщего разряда первого многоразрядного Р-ичного сумматора соединен с выходом элемента ИЛИ, а выход переноса старщего разряда соединен с управляющим входом коммутатора, информационные входы которого соединены соответственно с выходом первого многоразрядного Р-ичного сумматора и выходом бло ка формирования Р-ичного дополнения, вход которого соединен с выходом второго многоразрядного Р-ичного сумматора, а выход соединен с выходом устройства, управляющие входы блоков формирования Р-ичного обратного кода соединены с входами знаков операндов устройства, первые входы элементов И группы с первого по (N-1)-й соединены с управляющими входами соответствующих блоков формирования Р-ичного обратного кода, второй вход (N-1)-го элемен00 та И группы соединен с управляющим вхо00 дом N-ro блока формирования Р-ичного обратного кода, первый и второй входы элеменоо та ИЛИ соединены соответственно с первым и вторым входами первого элемента И группы, вторые входы элементов И группы с первого по (N-2)-и соединены с выходами соответствующих элементов ИЛИ группы, первые входы всех элементов ИЛИ группы соединены с вторым входом (N-1)-го элемента И группы, остальные входы каждого j-ro элемента ИЛИ группы (где j 1,..., N-2), соединены с первыми входами элементов И группы с N-ro по ( + 1)-й.

JO

| Oberman R | |||

| М | |||

| Digital circuits for binary arithmetic | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Способ закалки пил | 1915 |

|

SU140A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для вычисления суммы п к-разрядных р-ичных чисел | 1976 |

|

SU652559A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-30—Публикация

1983-08-19—Подача