Изобретение относится к цифровой вычислительной технике и может быть использовано пр отладке программ задач специализированньрс ЦВМ, содержащих в своем составе штатные блоки памяти (ВП) с рабочими программами.

Известило устройство для отладки программ, содержащее генератор тактовых импульсов, рабочие регистры, счетчик командj блок памяти программ блок формирования адресов, блок коьт мутации и блок управления, который после исполнения каждой вьшолняемой команды основной программы с помощью блока коммутации осуществляет вставку и исполнение нескольких вспомога- тельных служебньк команд, распечатывающих содержимое основных регистров и счетчика команд ЦВМ. После распечатки блоком управления производится формирование адреса следующей команды l.

Недостатком этого устройства является отсутствие оперативного контрол правильности прохождения программы по намеченной трассе адресов и в реальном масштабе времени.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее блок памяти программ, адресный, информационный входы и вход считывания которого соединены соответственно с адресным, информационным входами и входом считывания устройства, оперативный запоминающий блок, блок анализа, кода команды, вход которого подключен к выходу блока памяти программ, блок организации переписи информации, входы которого связаны соответствен.но с адресным входом блока памяти программ и с выходом блока анализа кода команды. Выход блока организации переписи соединен с входом оперативного запоминающего блока.

Известное устройство, при наличии в коде команды условного перехода, осуществляет запись адреса этой команды в соответствукнцую ячейку 6пера тивного запоминающего, блока. По завершении прохождения программы или ее части производится отображение хода вычислительного процесса, зафиксированного в оперативном зйпомкнающем блоке 2J .

Недостатком устройства-прототипа является невозможность оперативно/

контролировать правильность прохождения программы.

Цель изобретения - повышение быстродействия при Отладке программ.

Поставленная цель достигается тем что в устройство для отладки программ, содержащее блок памяти, первый элемент задержки и триггер, причем информационный, адресный входы и вход считывания устройства, соединены соответственно с адресным, информационным входами и входом считывания блока памяти, введены шифратор команды Останов, группа элементов И, группа элементов НИИ, второй элемент задержки, а в блок памяти введен дополнительный разряд, причем информационные выходы блока памяти и выход дополнительного разряда блока памяти соединены соответственно с первыми входами элементов И группы и с единичным входом триггера, единичный и нулевой выходы которого соединены с первыми входами первого и второго элементов И соответственно, выход первого элемента И соединен с вторыми входами элементов И группы, выходы которых соединены с первыми входами элементов ИЛИ группы, выход-второго элемента И соединен с входом шифратора команды Останов , выходы которого соединены с вторыми входами соответствующих элементов ИЛИ группы, вход считывания устройства через первый элемент задержки соединен с вто.рыми входами первого и второго элементов И, выход второго элемента задержки соединен с нулевым входом триггера, вход второго элемента задержки подключен ко входу второго элемента И, выходы элементов ИЛИ группы образуют группу информационных выходов устройства. .

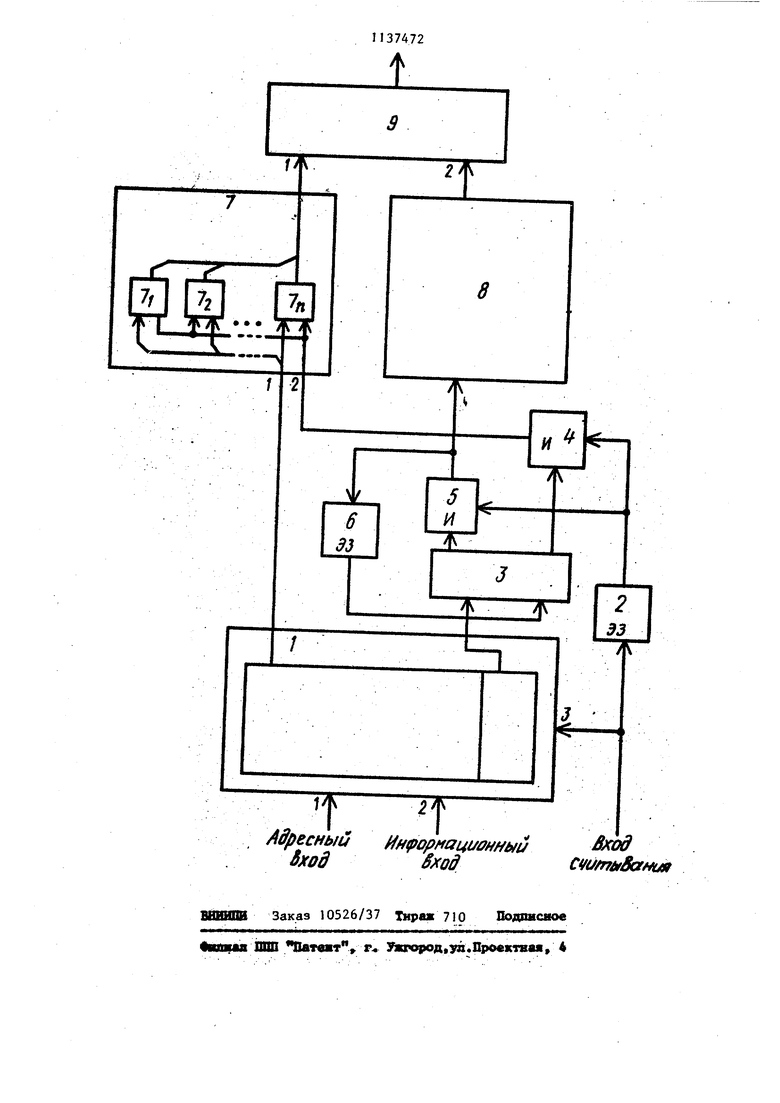

На чертеже приведена структурная схема устройства.

Устройство содержит блок 1 памяти цервый элемент 2 задержки, триггер 3, единичный вход которого -соединен с выходом дополнительного разряда блока 1 памяти, первый и второй элементы И 4 и 5, первые входы которых подключены соответственно к нулевому и единичному выходам триггера 3, вторые входы объединены и связаны с выходом элемента 2 задержки, второй элемент 6 задержки, выход которого подключен к нулевому входу тг иггера 3, группу элементов И 7, шифра-

тор 8 команды Останов и группу элементов ИЛИ, выход которой является выходом устройства, причем адресный, информационный входы и вход считывания устройства соединены соответственно с адресным, информационным входами и входом считывания блока 1 памяти. Вход считывания блока 1 памяти связан с входом первого элемента 2 задержки. Вход второго элемента 6 задержки объединен с входом шифратора 8 и подключен к выходу элемента И 5.

Информационные выходы блока 1 памяти и выход элемента И 4 соединены соответственно с первыми и вторым входами группы элементов И 7. Выход группы элементов И 7 подключен к первому входу группыэлементов ИЛИ .9, второй вход которого связан с выхо- .дом шифратора 8 команды Останов.

Устройство работает следующим образом.

Через информационный вход устройства производится загрузка блока 1 памяти исходным вариантом программы, подлежащей отладке. Одновременно по . этим же адресам осуществляется запись информации в дополнительный разряд блока 1 памяти. Значение информации, записанной в дополнительном разряде, определяется трассой ориентированным графом) адресов, используемых в процессе отладки. При этом под вершинами трассы понимаются адреса условных переходов. Затем, в процессе считывания на адресный вход устройства подается код адреса выбираемой ячейки блока 1 памяти, а на вход считывания - сигнал опроса.

При наличии на входах блока 1 памяти кода адреса и сигнала опроса из блока производится считывание информации, которая поступает на первые входы группы элементов И 7 информационная часть) и на единичный вход триггера 3 (информационная считанная из дополнительного разряда).

Сигнал опроса, поступающий на соответствующий вход блока 1 памяти, одновременно подается на вход первого элемента 2 задержки. Далее, этот сигнал, задержанный элементом 2 задержки на время работы блока 1 памяти и установки триггера 3, поступает на второй вход элементов И 4 и 5.

В зависимости от состояния триггера 3 сигнал пройдет через элемент И 4 или 5.

Первый случай соответствует ходу программы по намеченному пути выбираемых адресов. Bq втором случае оперативно устанавливается факт несоответствия в ходе трассы программы

С выхода элемента И 4 сигнал пост тупает на второй вход группы элементов И 7 и подсвечивает информацию, находящуюся на первом входе этой группы. В результате информационное слово, считанное из блока 1 памяти, появляется на выходе группы элементов И 7 и проходит ,через группу элементов ИЛИ 9 на выход устройства. Если сигнал появляется .на выходе элемента И 5, то он, во-первых, пройдя через второй элемент 6 задержки, устанавливает триггер 3 в исходное сос тояние, во-вторых, поступает на вход шифратора 8 команды Останов, которая передается через группу элементов ШШ 9 на выход устройства.

Техническим преимуществом предлагаемого устройстйа является простота осуществления кбнтроля правильности прохождения программы в процессе ее отладки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

| Устройство для отладки программ | 1990 |

|

SU1709320A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для отладки программ | 1986 |

|

SU1383372A1 |

| Устройство для откладки программ | 1987 |

|

SU1474656A1 |

| Устройство для отладки программ | 1982 |

|

SU1030805A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ, содержащее блок памяти, первый элемент задержки и триггер, . причем адресный, информационный входы и .вход считывания устройства соединены соответственно с адресным, информационным входами и входом считывания блока памяти, о т л и ч а ю щ е е ся тем, что, с целью повьшения быстродействия при отладке программ, в устройство введены шифратор команды Останов, группа элементов И, группа элементов ИЛИ, второй элемент задержки, а в блок памяти введен дополнительный разряд, причем информационные вьЬсоды блока памяти и выход дополнительного разряда блока памяти соединены соответственно с первыми входами элементов И группы и с единичным входом триггера, единичный и нулевой выходы которого соединены с первыми входами первого и второго элементов И соответственно, выход первого элемента И соединен со вторыми входами элементов И группы, выходы которых соединены с первь ми входами элементов ИЛИ группы, выход второго элемента И соединен со входом шифратора команды Останов, выходы которого соединены со вторыми входами соответствующих элементов ИЛИ группы, вход считывания устройстСП ва через первый элемент задержки соединен со вторыми входами первого и второго элементов И, выход второго элемента задержки соединен с нулевым входом триггера, вход второго элемента задержки подкщ)чен ко входу второго элемента И, выходы элементов ИЛИ оо ю группы образуют группу информационных выходов устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3935563, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР 754419, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-30—Публикация

1983-07-11—Подача