2

00

оо

со

со

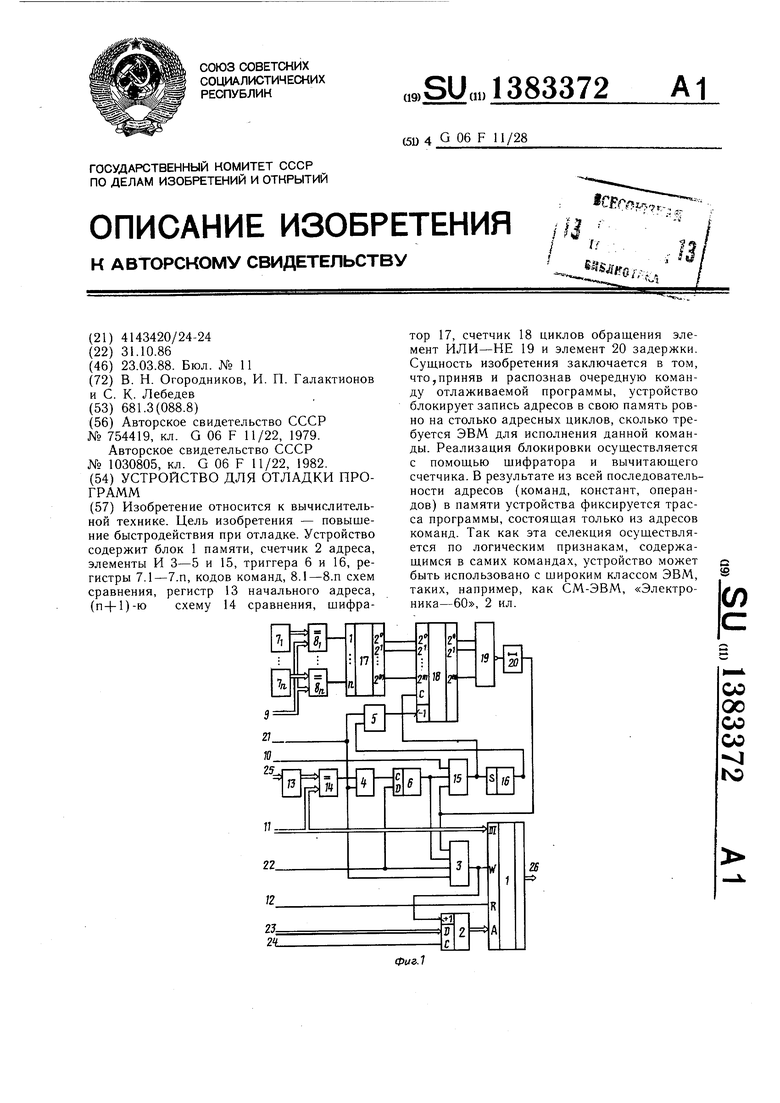

Изобретение относится к вычислительной технике и может быть использовано для отладки программ управляющих вычислительных машин и микропроцессорных систем.

Целью изобретения является повышение быстродействия при отладке за счет сокращения объема записываемой инофрмации по трассе програм-мы.

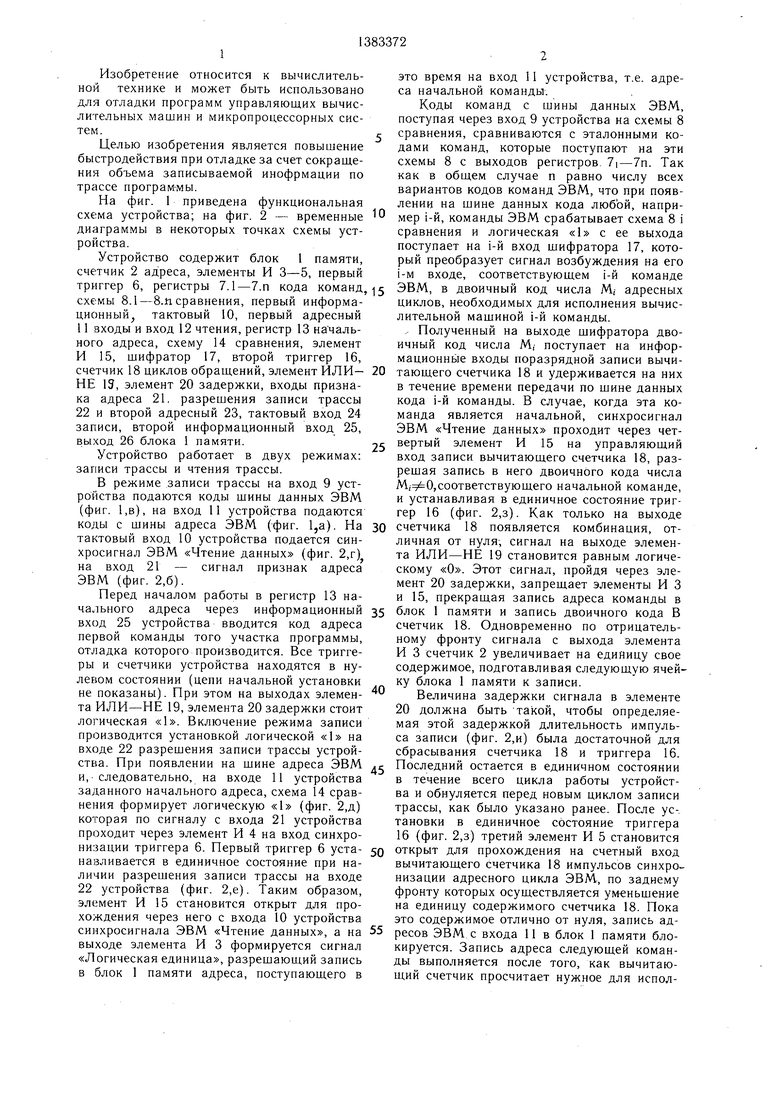

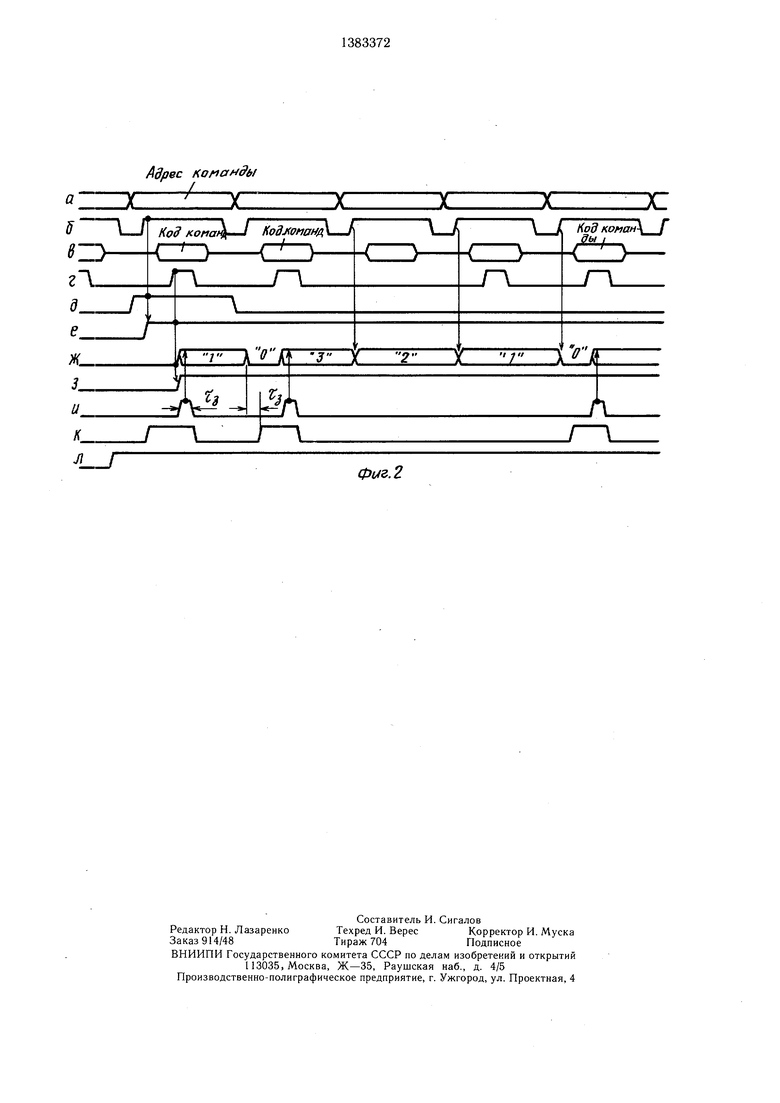

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы в некоторых точках схемы устройства.

Устройство содержит блок 1 памяти, счетчик 2 адреса, элементы И 3-5, первый триггер 6, регистры 7.1-7.п кода команд, схемы 8.1-8.11 сравнения, первый информа- ционный тактовый 10, первый адресный 11 входы и вход 12 чтения, регистр 13 начального адреса, схему 14 сравнения, элемент И 15, шифратор 17, второй триггер 16, счетчик 18 циклов обращений, элемент ИЛИ- НЕ 13, элемент 20 задержки, входы признака адреса 21. разрешения записи трассы 22 и второй адресный 23, тактовый вход 24 записи, второй информационный вход 25, выход 26 блока 1 памяти.

Устройство работает в двух режимах: записи трассы и чтения трассы.

В режиме записи трассы на вход 9 устройства подаются коды щины данных ЭВМ (фиг. 1,в), на вход 11 устройства подаются коды с шины адреса ЭВМ (фиг. 1,а). На тактовый вход 10 устройства подается синхросигнал ЭВМ «Чтение данных (фиг. 2,г) на вход 21 - сигнал признак адреса ЭВМ (фиг. 2,6).

Перед началом работы в регистр 13 начального адреса через информационный вход 25 устройства вводится код адреса первой команды того участка программы, отладка которого производится. Все триггеры и счетчики устройства находятся в нулевом состоянии (цепи начальной установки не показаны). При этом на выходах элемен- та ИЛИ-НЕ 19, элемента 20 задержки стоит логическая «1. Включение режима записи производится установкой логической «1 на входе 22 разрешения записи трассы устройства. При появлении на щине адреса ЭВМ и,- следовательно, на входе 11 устройства заданного начального адреса, схема 14 сравнения формирует логическую «1 (фиг. 2,д) которая по сигналу с входа 21 устройства проходит через элемент И 4 на вход синхронизации триггера 6. Первый триггер 6 уста- навливается в единичное состояние при наличии разрешения записи трассы на входе 22 устройства (фиг. 2,е). Таким образом, элемент И 15 становится открыт для прохождения через него с входа 10 устройства синхросигнала ЭВМ «Чтение данных, а на выходе элемента И 3 формируется сигнал «Логическая единица, разрешающий запись в блок 1 памяти адреса, поступающего в

0

0 5

ЗО

з5 ,c 50 55

это время на вход 11 устройства, т.е. адреса начальной команды.

Коды команд с шины данных ЭВМ, поступая через вход 9 устройства на схемы 8 сравнения, сравниваются с эталонными кодами команд, которые поступают на эти схемы 8 с выходов регистров. . Так как в общем случае п равно числу всех вариантов кодов команд ЭВМ, что при появлении на шине данных кода любой, например i-й, команды ЭВМ срабатывает схема 8 i сравнения и логическая «1 с ее выхода поступает на i-й вход шифратора 17, который преобразует сигнал возбуждения на его i-M входе, соответствующем i-й команде ЭВМ, в двоичный код числа Mi адресных циклов, необходимых для исполнения вычислительной машиной i-й команды.

, Полученный на выходе щифратора двоичный код числа М, поступает на инфор- мационнь1е входы поразрядной записи вычитающего счетчика 18 и удерживается на них в течение времени передачи по шине данных кода i-й команды. В случае, когда эта команда является начальной, синхросигнал ЭВМ «Чтение данных проходит через четвертый элемент И 15 на управляющий вход записи вычитающего счетчика 18, разрешая запись в него двоичного кода числа М,:/:0,соответствующего начальной команде, и устанавливая в единичное состояние триггер 16 (фиг. 2,з). Как только на выходе счетчика 18 появляется комбинация, отличная от нуля-, сигнал на выходе элемента ИЛИ-НЕ 19 становится равным логическому «О. Этот сигнал, пройдя через элемент 20 задержки, запрещает элементы И 3 и 15, прекращая запись адреса команды в блок 1 памяти и запись двоичного кода В счетчик 18. Одновременно по отрицательному фронту сигнала с выхода элемента И 3 счетчик 2 увеличивает на единицу свое содержимое, подготавливая следующую ячейку блока 1 памяти к записи.

Величина задержки сигнала в элементе 20 должна быть такой, чтобы определяемая этой задержкой длительность импульса записи (фиг. 2,и) была достаточной для сбрасывания счетчика 18 и триггера 16. Последний остается в единичном состоянии в течение всего цикла работы устройства и обнуляется перед новым циклом записи трассы, как было указано ранее. После установки в единичное состояние триггера

16 (фиг. 2,з) третий элемент И 5 становится открыт для прохождения на счетный вход вычитающего счетчика 18 импульсов синхронизации адресного цикла ЭВМ., по заднему фронту которых осуществляется ум-еньшение на единицу содержимого счетчика 18. Пока это содержимое отлично от нуля, запись адресов ЭВМ с входа 11 в блок 1 памяти блокируется. Запись адреса следующей команды выполняется после того, как вычитающий счетчик просчитает нужное для исполнения текущей i-й команды число N,- адресных циклов циклов ЭВМ, и его содержимое станет равным нулю.

Для перевода в режим чтения трассы на входе 22 разрешения записи трассы устройства подается уровень логического «О, при этом запирается первый логический элемент И, блокируя запись в блок 1 памяти и счет в счетчике 2. Для прочтения записанной трассы адрес ячейки блока памяти

и счетным входом счетчика адреса, группа разрядных выходов которого соединена с группой адресных входов блока памяти, выход первого триггера соединен с первым входом первого элемента И, отличающееся тем, что, с целью повышения быстродействия, в него введены регистр начального адреса, (п+1)-я схема сравнения, четвертый элемент И, второй триггер, шифратор, счетчик циклов обращений, элемент ИЛИ-

устанавливается на адресном входе 23 уст- Ю НЕ, элемент задержки, причем выходы п схем ройства, подается сигнал записи адреса сравнения соединены с соответствующими

входами шифратора, выходы которого соединены с информационными входами счетна вход 24 устройства, по которому адрес ячейки фиксируется в счетчике и выдается на его выход.

По сигналу на входе 12 чтения трассы устройства записанная в ячейке блока 1 памяти информация появляется на информационном выходе 26 устройства. Таким же образом считывается информация из других ячеек блока 1 памяти, причем порядок счичика циклов обращений, выходы которого jr соединены с входами элемента ИЛИ- НЕ, вход признака адреса устройства соединен с вторым входом первого элемента И и первыми входами второго и третьего элементов И, выходы второго и третьего элементов И соединены соответственно с тактывания произвольный, что обеспечивает сво- 20 товым входом первого триггера и вычитаю- боду в построении программы обработкищим входом счетчика циклов обращений,

при

записанной информации, например, считывании, начиная с нулевого адреса блока памяти, устройство выдает адреса команд исполненной ЭВМ программы (трассу) в их 25 естественной последовательности, что при их отображении на индикаторе облегчает оператору восприятие отладочной информации.

выход элемента ИЛИ-НЕ через элемент задержки соединен с третьим входом первого элемента И и первым входом четвертого элемента И, тактовый вход устройства соединен с вторым входом четвертого элемента И, выход которого соединен с единичным входом второго триггера и входом записи счетчика циклов, выходы второго и первого триггеров соединены соответственно с вторым входом третьего элемента И и третьим входом четвертого элемента И, вход разрещения записи трассы соединен с четвертым входом первого элемента И и информационным входом первого триггера, вход признака чтения, второй адресный вход и тактовый вход записи устройства соединены соответственно с входом чтения блока памяти, с информационным входом счетчика адреса и с входом записи счетчика адреса, второй информационный вход устройства соединен с входом регистра начального адреса, выход которого соединен с первым входом (п+1)-й схемы сравнения, выход которой соединен с вторым входом второго элемента И, первый адресный вход устройства соединен с вторым входом ()-й схемы сравнения.

Формула изобретения

Устройство для отладки программ, содержащее блок памяти, счетчик адреса, первый, второй и третий элементы И, п регистров кода команды (где п - количество команд, реализуемых в отлаживаемой ЭВМ), п схем сравнения и первый триггер, причем первый информационный вход устройства соединен с первыми входами п схем сравнения, выход каж,дого i-ro регистра кода команд (где , п) соединен с вторым входом соответствующей i-й схемы сравнения, первый адресный вход устройства соединен с информационным входом блока памяти, выход которого является информационным выходом устройства, выход первого элемента И соединен с входом записи блока памяти

и счетным входом счетчика адреса, группа разрядных выходов которого соединена с группой адресных входов блока памяти, выход первого триггера соединен с первым входом первого элемента И, отличающееся тем, что, с целью повышения быстродействия, в него введены регистр начального адреса, (п+1)-я схема сравнения, четвертый элемент И, второй триггер, шифратор, счетчик циклов обращений, элемент ИЛИ-

НЕ, элемент задержки, причем выходы п схем сравнения соединены с соответствующими

чика циклов обращений, выходы которого соединены с входами элемента ИЛИ- НЕ, вход признака адреса устройства соединен с вторым входом первого элемента И и первыми входами второго и третьего элементов И, выходы второго и третьего элементов И соединены соответственно с так0 товым входом первого триггера и вычитаю- щим входом счетчика циклов обращений,

5

0

5

0

выход элемента ИЛИ-НЕ через элемент задержки соединен с третьим входом первого элемента И и первым входом четвертого элемента И, тактовый вход устройства соединен с вторым входом четвертого элемента И, выход которого соединен с единичным входом второго триггера и входом записи счетчика циклов, выходы второго и первого триггеров соединены соответственно с вторым входом третьего элемента И и третьим входом четвертого элемента И, вход разрещения записи трассы соединен с четвертым входом первого элемента И и информационным входом первого триггера, вход признака чтения, второй адресный вход и тактовый вход записи устройства соединены соответственно с входом чтения блока памяти, с информационным входом счетчика адреса и с входом записи счетчика адреса, второй информационный вход устройства соединен с входом регистра начального адреса, выход которого соединен с первым входом (п+1)-й схемы сравнения, выход которой соединен с вторым входом второго элемента И, первый адресный вход устройства соединен с вторым входом ()-й схемы сравнения.

Адрес

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1988 |

|

SU1654827A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для отладки программ | 1988 |

|

SU1608673A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для контроля операций ввода-вывода | 1989 |

|

SU1686450A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия при отладке. Устройство содержит блок 1 памяти, счетчик 2 адреса, элементы И 3-5 и 15, триггера 6 и 16, регистры 7.1-7.П, кодов команд, 8.1-8.п схем сравнения, регистр 13 начального адреса, (п+1) Ю схему 14 сравнения, шифратор 17, счетчик 18 циклов обращения элемент ИЛИ-НЕ 19 и элемент 20 задержки. Сущность изобретения заключается в том, что,приняв и распознав очередную команду отлаживаемой программы, устройство блокирует запись адресов в свою память ровно на столько адресных циклов, сколько требуется ЭВМ для исполнения данной команды. Реализация блокировки осуществляется с помощью щифратора и вычитающего счетчика. В результате из всей последовательности адресов (команд, констант, операндов) в памяти устройства фиксируется трасса программы, состоящая только из адресов команд. Так как эта селекция осуществляется по логическим признакам, содержащимся в самих командах, устройство может быть использовано с широким классом ЭВМ, таких, например, как CM-ЭВМ, «Электроника-60, 2 ил. (О (Л

/

.2

| Авторское свидетельство СССР № 754419, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1982 |

|

SU1030805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-31—Подача