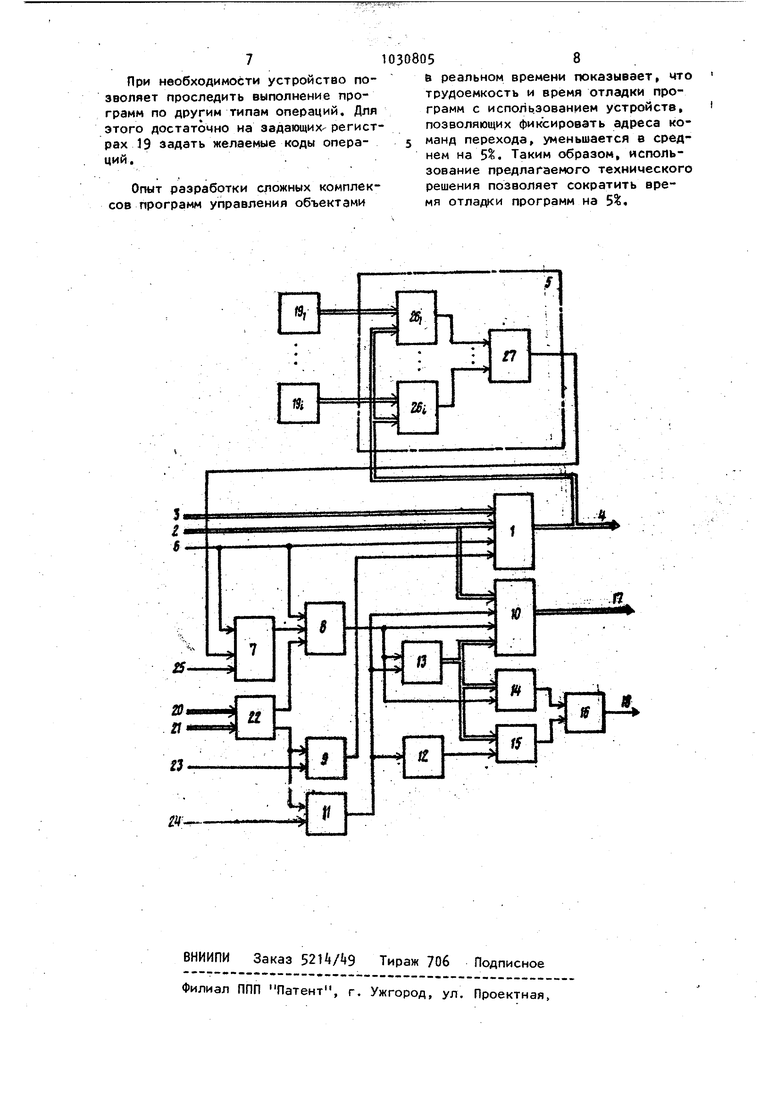

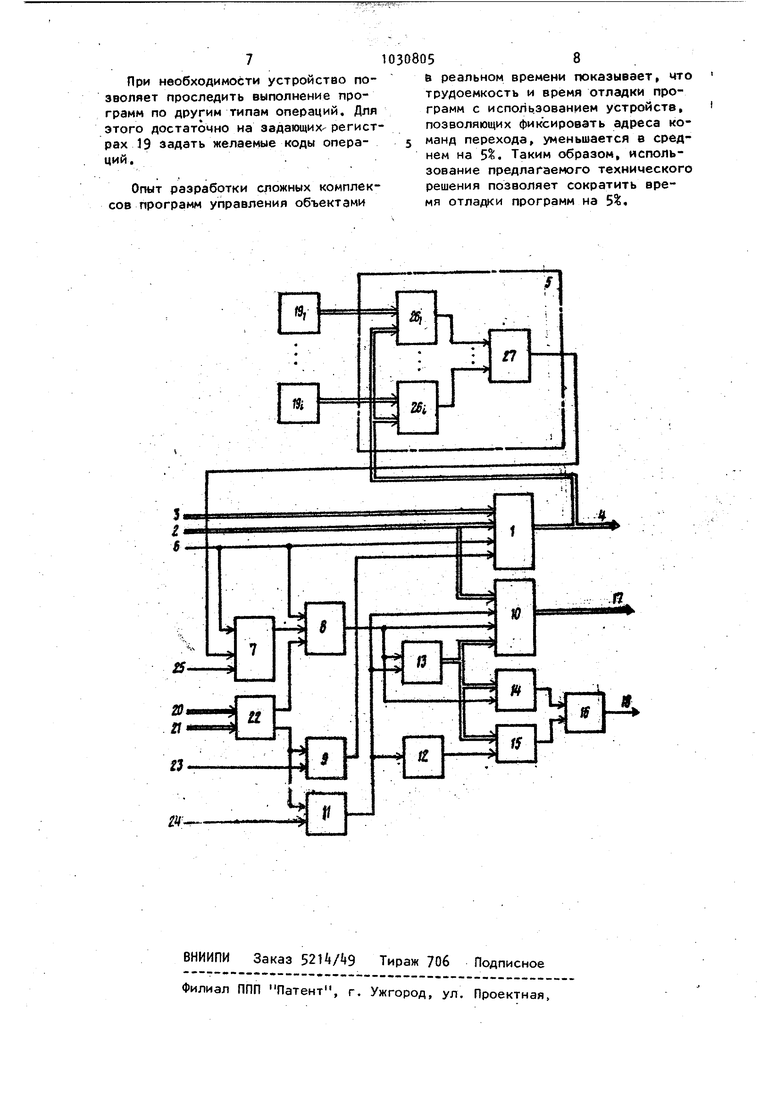

Изобретение относится к вычисли тельной технике и может быть испол зовано для автоматизированной отлад ки программ. Известно устройство для отладки программ, содержащее блок управления и наладочный запоминающий блок Однако это устройство не позволя ет прослеживать ход выполнения отлаживаемых программ в реальном времени. Известно устройство для отладки программ, содержащее наладочный запоминающий блок, адресным входом подключенный к адресному входу устройства и соединенный информационным входом и выходом с первыми входом и выходом устройства, второй вход которого подключен к первому управляющему входу наладочного запоминающего блока, второй управляющий вход которого соединен с выходом элемента И, первым.входом подключенного к первому выходу регистра режима, первый и второй входы ко торого соединены соответственно с третьим и четвертым входами устройства, пятый вход которого подключен к второму входу элемента И, входящему в блок управления . Это устройство также не позволяет проследить ход выполняемых в реальном времени отлаживаемых програм что увеличивает трудоемкость и время отладки программ. Наиболее близким техническим решением к изобретению является устройство для отладки программ, содер жащее вспомогательный блок памяти, три элемента И, триггер, элемент ИЛИ и счетчик 3 . Известное устройство может фикси ровать трассу программы только по командам перехода, что значительно сужает функциональные возможности программы. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности оперативного управления фиксацией трассы программы по любый командам системы команд. Поставленная цель достигается те что в устройство для отладки программ, содержащее вспомогательный блок памяти, сметчик, триггер, элемент ИЛИ, первый, второй и третий элементы И, причем выходы вспомога ельного блона памяти образуют первый информационный аыход устройства, выходы счетчика соединены с адресными входами вспомогательного блока памяти, выход первого элемента И соединен с входом сложения счетчика,.в устройство введены блок сравнения, регистр режима, четвертый элемент И, элемент НЕ, наладочный блок памяти, элемент ИЛИ-НЕ и группа задающих регистров, причем первый, второй и третий информационные входы устройства соединены соответственно с информационным входом наладочного блока памяти, с первым и вторым входами регистра режима, первый вход которого соединен.с первым входом первого элемента И, тактовый вход устройства соединен с сиихровходом триггера , с вторым входом первого элемента И и с управляющим входом считывания наладочного блока памяти, информационный выход которого соединен с первой группой входов блока сравнения и является BTopbfM информационным выходом устройства, единичный выход триггера соединен с третьим входом первого элемента И, выход которого соединен с управляющим аховом записи вспомогательного блока памяти, с первым входом четвертого элемента И, второй выход регистра режима соединен с первыми входами второго и третьего элементов И, выход которого соединен с управляющим входом считывания вспомогательного блока памяти со счетным входом вычитания сметчика, через элемент НЕ с первым входом элемента ИЛИ-НЕ, управляющие входы считывания и записи устройства соединены с вторыми входами соответгственно третьего и второго элементов И, выход которого соединен с управляющим входрм записи наладочного блока памяти, информационный выход счетчика соединен с вторыми входа ми элементов И и ИЛИ-НЕ, выходы которых через элемент ИЛИ соединены с управляющим выходом устройства, адресный вход устройства соединен с адресным входом и информационными входами наладочного и вспомогательного блоков памяти, управляющий вход признак константы устройства соединен с нулевым входом триггера, ин(}юрмационные выходы группы задающих регистров соединены с второй группой входов блока сравнения, выход которого соединен с инАормационнын входом триггера. На чертеже представлена схема устройства для отладки программ. Устройство содержит наладочный блок 1 памяти, адресным входом подключенный к адресному входу 2 устройства и соединенный информационным входом с входом 3 устройства. Информационный выход блока 1 подключен к выходу i устройства и первому входу блока 5 сравнения. Вход 6 устройства соединен с первым управляющим входом блока 1« синхровходом триггера 7 и первым входом элемента 8 И. Вторрй упра.вляю(аий вход блока 1 подключен к выходу элемента 9 И. Информационный вход вспомогательного блока 10 памяти соединен с адресным входом 2 устройства. Выход элемента 11 И подключен к первому управляюи ему входу блока 10 памяти, к входу инвертора 12 и первому входу реверсивного счетчика 13. Выход элемента 8 И соединен с вторым управляющим входом блока tO, с вторым входо счетчика 13 и первым входом элемента 1 И. Выходы счетчика 13 подключены к адресными входамблока 10, к вторым входам элемента 1 И и первым входам- элемента 15 ИЛИ-НЕ. Второй вход элемента 15 ИЛИ-НЕ соединен с выходом инвертора 12. Выходы элеме тов. I и 15 подключены к входам элемента 16 ИЛИ. Выход блока 10 соединен с выходом 17 устройства, выход блока 18 которого подключен к выходу элемента 16 ИЛИ. Выходы задающих регистров 19 и 19 соединены с вторыми входами блока 5 сравнения, выхо которого подключен к информационному .входу триггера 7. Выход триггера 7 соединен с вторым входом элемента 8 И. Информационные входы 20 и 21 устройства подключены к входам регистра 22 режима. Первый выход регистра 22 режима соединен с первыми входами элементов И 9 и 11. Второй ход элемента И 9 подключен к входу 23 записи устройства, а второй вход элемента И 11 соединен с входом 2 считывания устройства. Второй выход регистра 22 подключен к третьему входу элемента 8 И. Вход 25 устройст ва соединен с входом установки в О триггера 7. Блок 5 сравнения содержит, сумматоры 26 и 26 по модулю {два первыми входами подключённые к выходу блока 1, а вторыми входа15 и подключенные к выходам задающих егистров 19 и 19 соответственно. ыходы блоков 26 и 261 сравнения оединены с входами элемента 27 ИЛИ, ыход которого является выходом блоа 5 сравнения. Наладочный запоминающий блок 1 составе ycтpoйctвa для отладки прорамм заменяет на время отладки рабо-. чих программ постоянное запоминающее устройство ( ПЭУ команд и констант вычислительной машины Блок 1, в отличие от ПЗУ, обеспечивает оперативную многократную перезапись и корректировку рабочих программ в процессе отладки. По результатам отладки рабочих программ изготавлива- ется ПЗУ вычислительной маиины. В исходном состоянии устройства триггер 7 и счетчик 13 находятся в нулевом состоянии (цепи установки в исходное состояние не показаны) . В процессе отладки в блоке 1 размещается основная рабочая программа, подлежащэя отладке. В режиме выполнения основной программы в реальном времени разрешается только считывание команд и констант программь из блока 1, В служебном режиме разрешается запись в блок 1 для перезаписи и коррекции основной программы. В этом режиме разрешается также считывание информации с бло ка 10. Если соответствующий разряд регистра 22 режимов установлен в единицу, то в ходе выполнения программ разрешается запись в блок 10 кодов адресов команд, следующих за командами перехода (разрешается трассировка программ), Код режима заносится в регистр 22 по входу 20 от вычислительной машины или по входу 21 с пульта оператора. Для перехода в режим выполнения основной программы первый выход регистра. 22 устанавливается в нулевое состояние. Элементы 9 и 11 И закрыты. Импульсный сигнал считывания с входа 6 поступает на вход блока 1. По этому сигналу в блоке 1 производится обращение по адресу, код которого поступает по входу 2. Считанный код с выхода блока 1 поступает на выход i устройства. Признаки операции и переходов занимают в кодах команд определенные разряды. Данные разряды поступают с выхода блока 1 на входы блоков 2б.

На другие входы блоков 2б сравнения с выходов задающих регистров 19 поступают коды команд переходов. Количество команд переходоа и их коды определяются системой команд вычислительной машины. Коды команд переходов устанавливаются Е регист рэх 19f которые могут быть выполнены на тумблерах или с жесткой распайкой. Количество регистров 19 и блоков 26 определяется количеством кодов команд переходов, по которым необходимо oбecпeч вaть трассиров ку программ.

Если считанный код на выходе блока 1 окажется кодом операции перйхода то на выходе одной из блоков 26 cDa8иeн,я появится сигнал логической 1, злемеит27 ИЛИ этот сигкал попадает на имформаци окИ1- й вход триггера 7. По заднему фронту сигнала сч пывания., проходящего по входу 6, триггер 7 устанавливается 8 единичное состояние. Триггер 7 устанавливается в единичное

состояние в-сзгда,, когда в определенных разряд;,:;, считанного из блока коДЭ окажется код команды перехода Обращение к блоку 1 за константой сопровон-л.р. сигналом признака ксьстан-г:.4, гоступающему по входу 25 устройства на аход Установки в О триггере. 7 и удерживающему триггер 7 в HViieEOM состоянии. Если второй выход регистра 22 установлен в единич ное сог.-ояний то при выполнении программ осуществляется их трассировка. При этом, при считывании команду следующей за командой перехода, сиг нал считывания с входа 6 через откры тый элемент И 8 пройдет на управляющий аход вспомогательного запоминающего блока 10, В блок 10 запишется код адреса, поступающий на информационный вход блока 10 с адресного входа 2 устройства. Адрес обращения к б;юку 10 содержится в реверсивном счетчике 13- Но заднему фронту сигнала, поступающего с выхода злемен- та 8 Hj содержимое счетчика 13 уве™

лидивае1Сй на единицу. При записи в блок 10 по адресу, код которого содержит все ед -;иицы {признак запалив НИИ г.п:-.яги блока 10), сигнал с выхо да элемента 8 И через элементы 1 И и 16 пПЯ Го;;7упит на выход 18 устрой;: rsa. Сигнал на выходе 18 устрой- сТВ а яаляетсн сигналом прерывания

)зь чмслительной машины. При выполнение оскоаной Гlpoгpa лмы наличие этого сигнала свидеельствует о переполнение йсг.омогательной памяти. По (зхсдам 20 или 21 устройства можно устансзить кторой выход регистра 22 в нулевое -состоякиэ и тем самым остановить гбоцесс трассировки програм «„ Вы;клне;-;ме основной рабочей программы )ю-ме происходить дальше. Таггим сбразо -; пр;1.йллелько с аыполHti-i-aieM основной программы устройств п.3:1чэ,пяа производить трассировку ;)той поогрэкмь:, Hps этом не нарушается ;;од выполнения основной рабочей Е.зогрзу.м.Ь,, что особенно важно npji отладке управляющих программ реального , Начало трассмровки програм |Ы задаемся устаечозкой в сди.чи-;но8 состояние первого выхода 22; окончакме трассирозки установкой этого выхода в нулевое состояние по входам 2О,или 2 уст .1Ойс.таа,

Для перехода а слу «ебный режим перзый выход регистра 22 устанавлиБэется в единичное состоя;- иел З.пемеT 3 « П - О г;.;, рытые Имп: тьснь й (:иг:-(ал записи с входа 23 через элеf/:eHT Э И поступагт на управляющий вход блока 1, По этому сигналу происходит запись а блок Ккода посту пающего на его информационный вход с входа 3 устройства. Запись происходит по адресу, код которого поступает на адресный вход блока 1 с адpecHdro входа 2 устройства, В этом режиме также осуществляется считывание информации из блока 10, Импульсный сигнал считывания с входа 24 у тройстза через элемент 11 поступает на управляющий вход блока 10, По переднему фронту этого сигнала содержимое счетчика 3 уменьшается не единицу. Считанный из бло™ ка iO код поступает на выход 17 устрэйства,: При считывании из нулевой гчейни блока 10 (на выходе счетчика 13 и на первых входах элемента 15 НЛИ-ИЕ в этом случае окажутся все нули) сигнал с выхода элемента II И через инвертор 12, элемент 15 ИЛИ-НЕ и элемент 1б ИЛИ посту- , пэет на выход 18 устройства. Когда устройство находится в служебном режиме, наличие данного сигнала.на выходе 18 свидетельствует о токц что ася информация из блока 10 сосчитэиа.

при необходимости устройство позволяет проследить выполнение программ по другим типам операций. Для этого достаточно на задающих регистрах 19 задать желаемые коды операций..

Опыт разработки сложных комплексов программ управления объектами

0308058

& реальном времени показывает, что трудоемкость и время отладки программ с исполь.зованием устройств, позволяющих фиксировать адреса команд перехода, уменьшается в среднем на 5. Таким образом, использование предлагаемого технического решения позволяет сократить время отладки программ на 5%,

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программ | 1988 |

|

SU1608673A1 |

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1348839A1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1991 |

|

RU2012035C1 |

| Устройство для формирования сигнала прерывания при отладке программ | 1985 |

|

SU1339569A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ,ПРОГРАММ, содержащее вспрмогательный блок памяти, счетчик, триггер, элемент ИЛИ, первый, второй и третий злементы И, причем выходы вспомогательного блока памяти образуют первый информационный выход устройства, выходы счетчика соединены с адресными входами вспомогательного блока памяти, выход первого элемента И соединен с входом сложения счетчика, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности оперативного управления фиксацией трассы программы по любым командам системы команд, в него введены блок сравнения, регистр режима, четвертый элемент И, элемент НЕ, наладочный блок памяти, элемент ИПИ-НЕ и группа задающих регистров, причем первый, второй и третий информационные входы устройства соединены соответственно с информационным входом наладочного блока памяти, с первым и вторым входами регистра режима, первый вход которого соединен с niepвым входом первого элемента И, тактовый вход устройства соединен с синхровходрм триггера, вторым входом первого элемента И иуправляющим вХО дом считывания наладочного блока памяти , информационный выход которого соединен с первой группой входов блока сравнения и является вторым, информационным выходом устройства, единичный выход триггера соединен с третьим входом первого элемента И, выход которого соединен с управляющим входом записи вспомогательного блока памяти, с первым входом четвертого элемента И, второй выход регистра режима соединен с первыми входами второго и третьего элементов И, g выход которого соединен с управляющим входом считывания .вспомогательного блока памяти, со счетным входом вычитания счетчика, через элемент НЕ с первым входом элемента ИЛИ-НЕ, управляющие входы считывания и записи устройства соединены с вторыми входами соответственно третьего и второго элементов И, выход которого Осоединен с управляющим входом записи .. наладочного блока памяти, информао ционный выход счетчика соединен с X) вторыми входами элементов И и ИЛИ-НЕ, о ел выходы которых через элемент ИЛИ соединены с управляющим выходом устройства , адресный вход устройства соединен с адресным входом и информационными входами наладочного и вспомогательного блоков памяти, управляющий вход признак константы устройства соединен с нулевым входом триггера, информационные выходы группы задающих регистров соединены с второй группой входов блока сравнения, выход которого соединен с информационным входом триггера.

т

1 6

П

IV

ZBi

п.

п

.

LT

15

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР К , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-07-23—Публикация

1982-04-23—Подача