f

Изобретение относится к автоматик.е и вычислительной технике и может бь1ть использовано в устройствах программного контроля.

По основному авт,св № 920729

известно устройство, которое содержит блок .программного управления дешифратор синхросигналов, /сешийратор кода операций, генератор s-мпульcoBs дешифратор микрокоманд, -туппу формирователей амплитуд,, регистр, группу формирователей фронта выходного сигнала, группу формирователей спада выходного сигнала, группу триггеров, генератор кодов и элемент задержки. При STOt rpyima входов кода операций блока программного управления подключена к группе в: одов дешифратора кода операций, группа выходов дешифратора кода операций - к первой группе входов деошфратора микрокоманд, вторая группа входов которого подключена к группе синхронизирующих выходов блока программного управления, первьп выход дешифратора микрокоманд - к установочному входу регистра, первая группа информационных вькодов блока программного управления соединена с группой информационных входов регистра, группа синхронизирующих входов блока программного управления прдключена к группе вь:ходов дешифратора синхросигналов S вьгход генератора импуотьсов - к входу импульсной последовательности блока программного управления, группы форггирователей амг литуды являются выходами устройства, вьгход генератора импульсов соединен со счетным входом генератора кодов и входом элемента задержки, группа выходов элемента задержки подключена к соответствующим входам формирователей спада сигналов группь и форг-п1рователей фронта выходного сигнала группы, группа выходов генератора кодов к группе входов дешифратора синхросигна,лов и к соответствующим кодовым входам формирователей спада выход-наго сигнала группы и формирователей фронта выходного сигнала группы и соединена с второй группой информационных выходов блока программного управления, первая и вторая группы установочных входов дешифратора микрокоманд подключены соответственко к группе установочных входов форми388032

рователей фронта выходного сигнала,, выход каждого формирователя фронта выходного сигнала группы соединен с единичным входом соответствующего 5 триггера группы, выход каждого формирователя спада выходного сигнала группы - с нулевым входом соответствующего триггера группы, управляюш,ие входы ка,цого триггера группы подключены к соответствующим входам формирователей амплитуд группы, выходы которых являются выходами устройства, второй выход дешифратора микрокоманд соединен с установочным

5 входом генератора кодов.

Блок программного управления содержит дешифраторы, узел памяти, узел сравнения, узел пуска-останова, регистр команд, регистр адреса, группы .элементов И, элементы ИЛИ, счетчик команд, элемент НЕ, наборное поле, при этом первый вход наборного поля подключен к первому входу узла пуска-останова, второй вход которого соединен с выходом первого элемента И, первьй вход которого объединен с первым входом второго элемента И и подключен к выходу узла сравнений, первьй вход которогс подключен к второму выходу наборного поля, третий выход которого объединен с третьим входом первого эле.-;гита И и подключен к первому выходу узла пуска-останова, второй вьосод которого соединен с входом

элемента НЕ и вторым входом первого элемента И, выход элемента НЕ подключен к второму входу второго элемента И, третрш вход которого

объединен с третьим входом первого элемента И и подключен к первому выходу узла пуска-останова, второй выход которого соединен со счетньгм входом счетчика команд, выход которого подключен к второму входу узла сравнения и к первому входу узла памяти, выход которого соединен с первым входом регистра команд, группа ижрормационных входов которого

является информационной группой выходов блока, которые объединены с группой входов первой группы элементов И к подключены к группе разрядных входов регистра адреса, выход

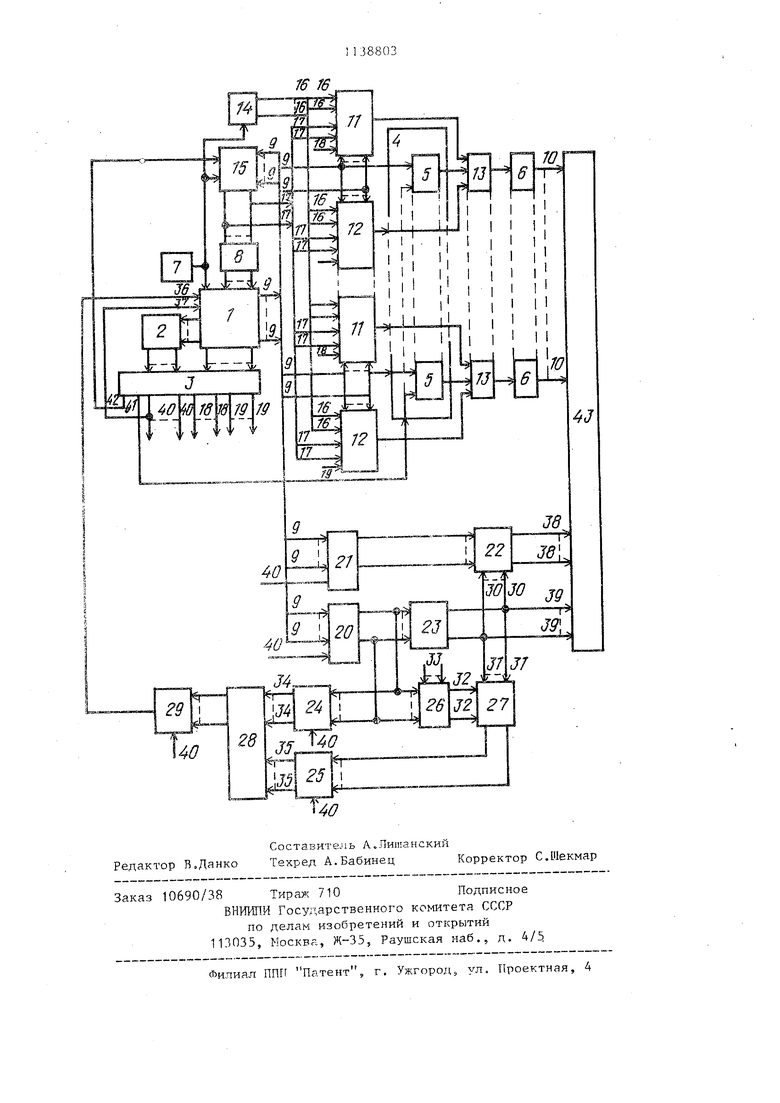

которого подрслючен к первому входу второй группы элементов И, чатвертьш и пятый выходы наборного поля соответственно с первому входу эле- - мента ИЛИ и первому входу третьеГ группы элементов И, выходы каждой группы элементов И - к соответствую щему входу счетчика команд, первый вход первой группы элементов И, вто рой вход второй группы элементов И и вход регистра адреса - к соответствующим выходам первого дешифратор первая группа входов которого соединена с первой группой выходов узла пуска-останова, которые являются первой группой выходов синхро.низационных выходов блока,группа выходов узла пуска-останова является группой синхронизационных входов блока, третий выход узла пуска-оста нова подключен к второму входу узла памяти, четвертый выход узла пус ка-останова к управляющему входу регистра команд, вторая группа выхо дов регистра команд является группо выходов кода операций блока и подключ на к группе входов второго дешифратора, группа выходов которого под ключена к второй группе входов первого дешифратора, выход второго элемента И - к второму входу элемен та КГТИ, выход которого соединен с вторым входом третьей группы элемен тов и 1 . Недостатком известрюго устройства является отсутствие возможности подачи специальных стимулируюрщх воздействий по цепям питания, что затрудняет контроль резервированньк устройств с мажоритарными элементами. В случае раздельного резервирования устройства его контроль на обычной аппаратуре приводит к пропуску даже некоторых многократных неисправностей, находящихся в разных узлах о Целью изобретения является расши рение области применения. Поставленная цель достигается тем, что в устройство введены пер-, вый, второй и третий регистры, управляемый источник напряжений, первый и второй коммутаторы, блок компараторов, первые, вторые и третий элементы И, подключенные выходом к пусковому входу узла пуска-останова блока программного управления, соединенного информационными выходами с разрядными входами первого регистра и второго регистра, связан ного выходами с первыми входами пер вых элементов И, с входами первого коммутатора и с входами управляемого источника напряжений, подключенного выходами к измерительным входам блока компараторов, к вторым вькодам устройства и информационным входам второго коммутатора, соединенного управляющими входами с выходами пер вого регистра, подключенного управляющим входом к пятым выходам дешифратора микрокоманд, соединенным также с первыми, входами вторых элементов И, с управляющим входом второго регистра, с разрещающим входом третьего элемента И и с вторыми входами первых элементов И, подключённых входами к: S-входам третьего регистра, соединенного -выходами с информационными входами третьего элемента И, а R-входами - с выходами вторых элементов И, подключенных вторыми входами к выходу блока компараторов, соединенного входами опорных напряжений с выходами первого коммутатора, причем один из разрядов пятых . выходов дешифратора микрокоманд соединен с остановочным входом узла , Ттуска-остаиова блока программного управления, а выходы первого ксммутатора являются третьими выходами устройства. На чертеже приведена структурная схема предлагаемого устройства. Устройство содержит блок 1 программного управления, дешифратор 2 кода операции, дешифратор 3 микрокоманд, регистр 4 воздействия, состоящий из триггеров 5, формирователь 6 амплитуд, генератор 7 импульсов, дешифратор 8 синхросигналов, информационные выходы 9 блока 1 программного управления, первые выходы 10 устройства, формирователи 11 фронта выходного сигнала, формирователи 12 спада выходного сигнала, триггеры 13, элемент 14 задержки, генератор 15 кодов, выходы 16 элемента 14 задержки, разрядные выходы 17 генератора 15 кодов, третьи выходы 18, четвертые выходы 19 дешифратора 3 микрокоманд, второй регистр 20 номиналов напряжений питания, первый регистр 21 и второй коммутатор 22 контрольных напряжений,управляемьй многоканальный источник 23 напряже- . НИИ, элементы И 24 и 25, первый коммутатор 26 опорных напряжений, блок 27 компараторов, третий регистр 28 контроля включения напряжения питанияJ элемент И 29j входы 30 кoI Iмyтируемых величин коммутатора 2 контрольных напряжений, входы ижеряемых 31 и опорньк 32 напряжений блока 27 кр.мпаратороз, входы 33 опорных нД-пряжений. входы ЗА-S и 35-R регистра 28 контроля Бключени напряжения питания, вхсд -i5 пуска и вход 37 останова блока программно го управления, вторые 38 и третьи 39выходы устройства, пптые выходы ДО дешифратора микрокоманд. первый Д1 и BTopofi 42 выходы дешифратора 3,, объект 43 проверки. Управляемый мггогоканальный источ ник 23 напряжений содержит ряд стабилитронов. Блок 27 компараторов предназначе для фиксации момента появления на входах источника 23 заданных в команде величин напряжений питания и может быть реализован, например, на микросхемах 52iCA1. Коммутаторы 22 и 26 предназначены для подключения соответствующих источников и могут быть реализо вань па релейных элементах. Устройство работает следуюцим образом. Блок 1 програм ного управления исполняет команды программы контрол Если исполн.яемой командой окажетс команда задания стимулирующих воздействий по депям питания, то она расшифровывается дешифратором 2 ко да операдии и возбуж,дает дешифрато 3 микрокоманд на вькодах 40 котор го вырабатывается ряд микроопераци пьгА еигаалоз, первыйиз которых, по тупая на лход 37 останова блока пр pa iMHoro у правления 3 останавливает дальнейшую выборку комггнд программы контроля„ Вторым сигналом с выхода 40дешифратора 3 микрокоманд осутцес вляется ввод информадионной части коман.ды задания стимулирующих воздействий иоступгаюшей с выходов 9 блока 1 программного управления., а регистр 20 номиналов т апряжений пмтания и регистр 21 контрольных нап ряжений, которьй управляет срабатыванием коммутатора 22. подключающего соответствующие вьтходы много канального источнш а 23 напряжений зьтходам 38 устройства., По информаНИИ регистра 20 ос-ущестзляются вклю чение соответствующего источника напряжений и настройка его на задангное значение нот-данала, коммутатор 26 осуществляет подключение опорных напряжений к соответствующим компараторам блока 27 компараторов и возбуждаются соответствующие элементы И 24 группы. Третьим сигналом с выходов 40 дешифратора 3 осуществляется опрос элементов И группы и установка в единичное состояние трек триггеров регистра 28, которые соединены с вы. ходами возбужденнь х элементов И 24 группы. После того, как на соответствующих выходах управля,емого источника 23 напряжений появятся и достигнут заданных значений напряжения питания, срабатывают соответствующие компараторы 27 и по четвертому сигналу с выходов 40 дещифратора 3 микрокоманд через элементы И 25 группы устанавливают в нулевое состояние соответствуюгдие им триггеры регистра 28 контроля включения напряжений питания. Если в данньш .момент времени на каком-либо выходе управляемого источника 23 напряжений заданное в команда нагфяжение питания еще не достигло заданной величины то на выходе соответствующего компаратора блока 27 сигнал не вырабатывается, и соответствующий триггер регистра 28 останется в единичном состоянии,, После того как все заданные в команде напряжения питания появятся на выходах источников 23 напряжений, регистр 28 переходит в нулевое состояние и возбуждает соответствующие входы элемента И 29, Пятым сигналом с выходов 40 дешифратора 3 г икрокоманд осуществляется опрос элемента И 29 и появление на его выходе сигнала, который поступает на вход 36 пуска блока программного управления, в результате чего устройство продолжает реализацию следующих команд программы контроля. Предлагаемое устройство обеспечивает выдачу по программе стимулирующих воздействий по цепям питания объекта контроля. Это позволяет проверять устройства раздельно по каждому каналу путем подачи питания только на проверяемый канал и соответствующей настройки мажоритарных элементов. Настройка мажоритарного элемента состоит в подаче на его входы от соседних каналов постоянных значений уровней логических О и 1, что обеспечивается стиму лирующим воздействием по цепям питания на соответствующие элементы. Контроль начинается поцачей стимулирующих воздействий по цепям питан Затем реализуется собственно программа контроля i-ro канала, во вре мя которой блок формирования воздействий обеспечивает подачу на информационные входы i-ro канала объекта проверки сигналов тестовой последовательности. После окончания реализации программы контроля осуществляется настройка на контроль следующего канала путем подачи соот ветствующих стимулирующих воздейст вий по цепям питания и реализации программы контроля данного канала. Маскирование выходов не проверяемых в данный момент каналов позволяет использовать одну общую программу 3.8 контроля i-ro канала для проверки остальных каналов резервированного устройства, что приводит к существенному сокращению объема программы проверки. Положительный эффект изобретения заключается в расширении области применения устройства Это обстоятельство находит свое зьфажение в том, что с помощью предложенного устройства можно осуществлять контроль высоконадежных цифровых устройств с резервированием на уровне каналов, устройств и отдельных узлов, а также определять область устойчивой работы обычных цифровых устройств при различных значениях напряжения питанияо Кроме того, предложенное устройство повьшает качество контроля путем автоматизации процесса проверки при граничных значениях напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования входных воздействий в системе программного контроля | 1980 |

|

SU920729A1 |

| Устройство для централизованного управления вычислительной системой | 1987 |

|

SU1674146A1 |

| Микропрограммное устройство управления | 1977 |

|

SU746516A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Микропрограммное устройство управления | 1981 |

|

SU987623A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1319079A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

УСТРОЙСТВО ДЛЯ ФОРШРОВАНИЯ ВХОДНЫХ ВОЗДЕЙСТВИЙ В СИСТЕ1ЧЕ ПРОГРАММНОГО КОНТРОЛЯ по авт.св. № 920729, отличающееся тем, что, с целью расширения области применения устройства, в него введены первый, второй и третий регистры, управляемый источник напряжений, первый и второй коммутаторы, блок компараторов, первыеJ вторые и третий элементы И, подключенные выходом к пусковому входу узла пуска-останова блока программного управления, соединенного информационными выходами с разрядными входами первого регистра и второго регистра, связанного выходами с первыми входами первых элементов И, с входами первого комMi THTopa и с входами управляемого источника напряжений, подключенного выходами к измерительным входам блока компараторов, к вторым входам устройства и информационным входам второго коммутатора, соединенного управляющими входами с выходами первого регистра, подключенного управляющим входом к пятым выходам дешифратора микрокоманд, соединенным также с первыми входами вторых элементов И, с управляющим входом второго регистра, с разрешающим входом третьего элемента И и с вторыми входами первых элементов И, подключенных выходами к S-входам третьего регистра, соединенного выходами с информационными входами третьего (Л элемента И, а R-входами - с выходами вторых элементов И, подключенных вторыми входами к выходу блока компараторов, соединенного входами опорных напряжений с выходами первого коммутатора, причем один из разрядов пятых выходов дешифратора микрокоманд соединен с остановочнь со входом узла пуска-останова блока 00 программного управления, а выходы 00 о со первого коммутатора явлгпотся третьими выходами устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для формирования входных воздействий в системе программного контроля | 1980 |

|

SU920729A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-07—Публикация

1983-01-07—Подача