1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных устройств.

Известен асинхронный регистр сдвига на элементах И-НЕ, содержащий ячейки памяти, каждая из которых состоит из трехстабильного триггера на трех элементах и вспомогательного элемента, причем первые входы первых двух элементов трехстабильного триггера являются информационными входами ячейки, а первые входы его третьего и вспомогательного элементов объединены и являются управляющим входом Ячейки, выходы первых двух элементов трехстабильного триггера являются информационными выходами ячейки, а выход его третьего элемента соединен с вторым входом вспомсэгательного элемента, выход которого является управляющим выходом ячейки, информационные и управляюф ий входы 5-й ячейки соединены соответственно с информационными и управляющим входами (1-1)-й ячейки, два входа первых двух элементов трехстабильного триггера 1-й ячейки и третий вход ее вспомогательного элемента соединены соответственно с информационными и управляющим выходами (1+1)-й ячейки, а третий и пятый входы вспомогательного элемента i-й ячейки соединены с информационными выходами (1+2)-й ячейки. Регистр характеризуется высоким быстродействием: сдвиг информации на один разряд осуществляется в нем за не зависящее от числа ячеек памяти время, равное 61, где - задержка одного элемента И-НЕ ClJ.

Недостаток этого регистра - избыточность оборудования, необходимого для хранения одного бита информации

Наиболее близким к предлагаемому по технической сущности является регистр сдвига на элементах И-НЕ, состоящий из ячеек памяти, каждая из которых состоит из шести элементов, образующих две симметричные цепочки такие, что первые элементы обеих цепочек образуют основной, а вторые - вспомогательный RS-триггеры ячейки, причем первый, второй и третий входы первого элемента каждой цепочки являются ее информационным, первым и вторым управляющими входами, а выход соединен с первыми вхо

388342

дами второго и третьего элементов, второй вход которого соединен с выходом второго элемента, а выход является информационньм и управляющим 5 выходом цепочки, причем информационный выход и первый управляющий выход каждой цепочки |-й ячейки памяти соединены с информационным входом и управляющим выходом соответствующей О цепочки (in-1)-и ячейки регистра, а ее второй управляю1ций вход - с управляющим выходом противоположной цепочки (i-f1)-й ячейки регистра 2. Однако известный регистр характеризуется низким быстродействием: сдвиг на один разряд происходит за время, лежащее, в зависимости от записанной в регистр информации, в пределах 4 - бГп, где задержка одного элемента И-НЕ; п - число ячеек регистра.

Цель изобретения - повышение быстродействия регистра сдвига.

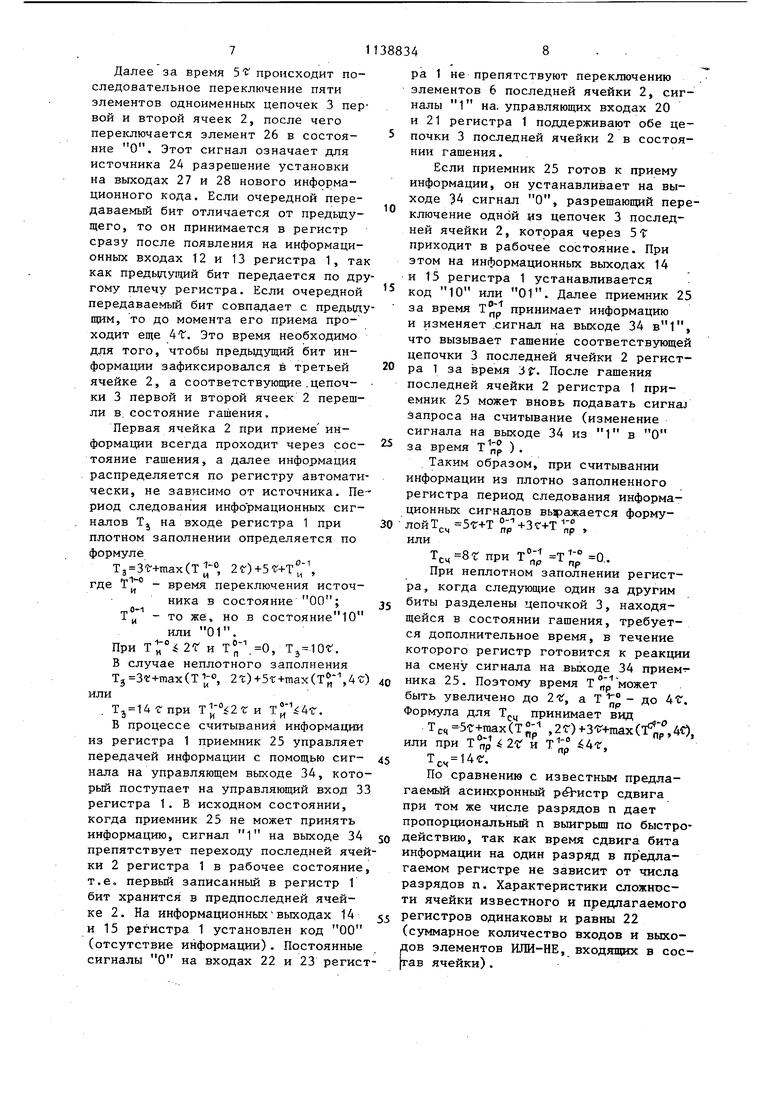

Указанная цель достигается тем, 5 что в асинхронном регистре сдвига, содержащем ячейки памяти из шести элементов ИЛИ-НЕ, образующих-две симметричные цепочки, причем в каждой цепочке выход первого элемен 0 та ИЛИ-НЕ соединен с первыми входами второго и третьего элементов ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ каждой цепочки соединен с вторым входом вто.рого элемента ИЛИ-НЕ другой цепочки j той же ячейки памяти, первый вход

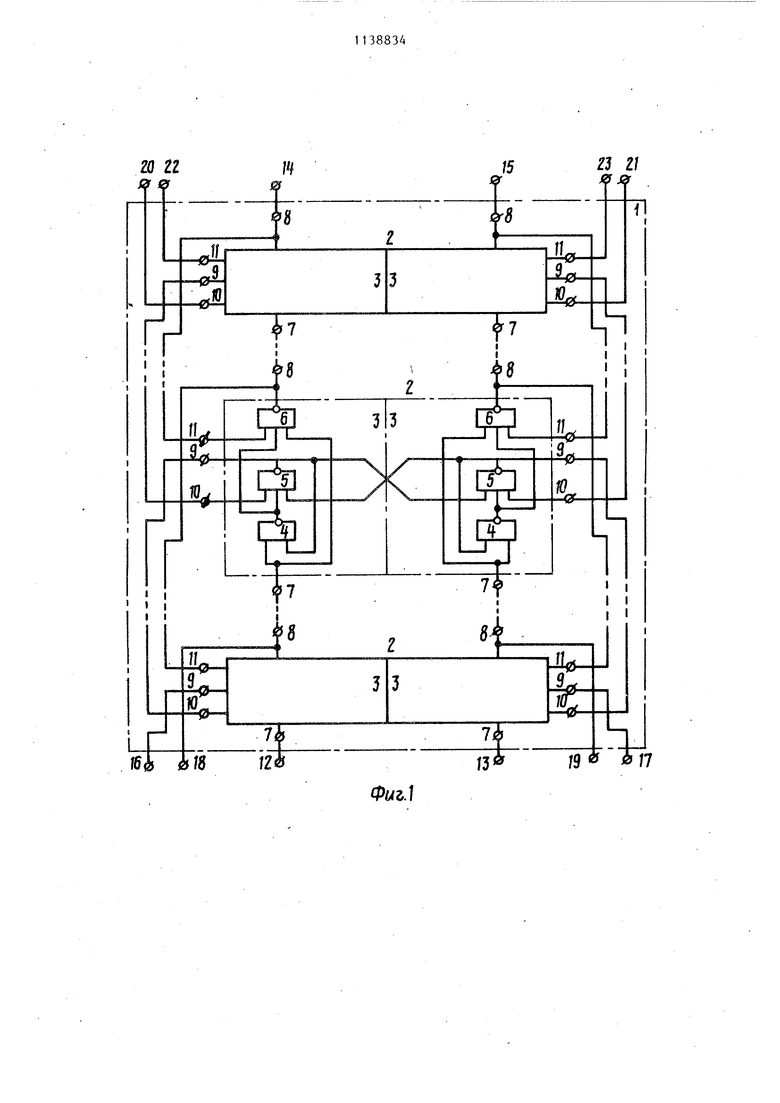

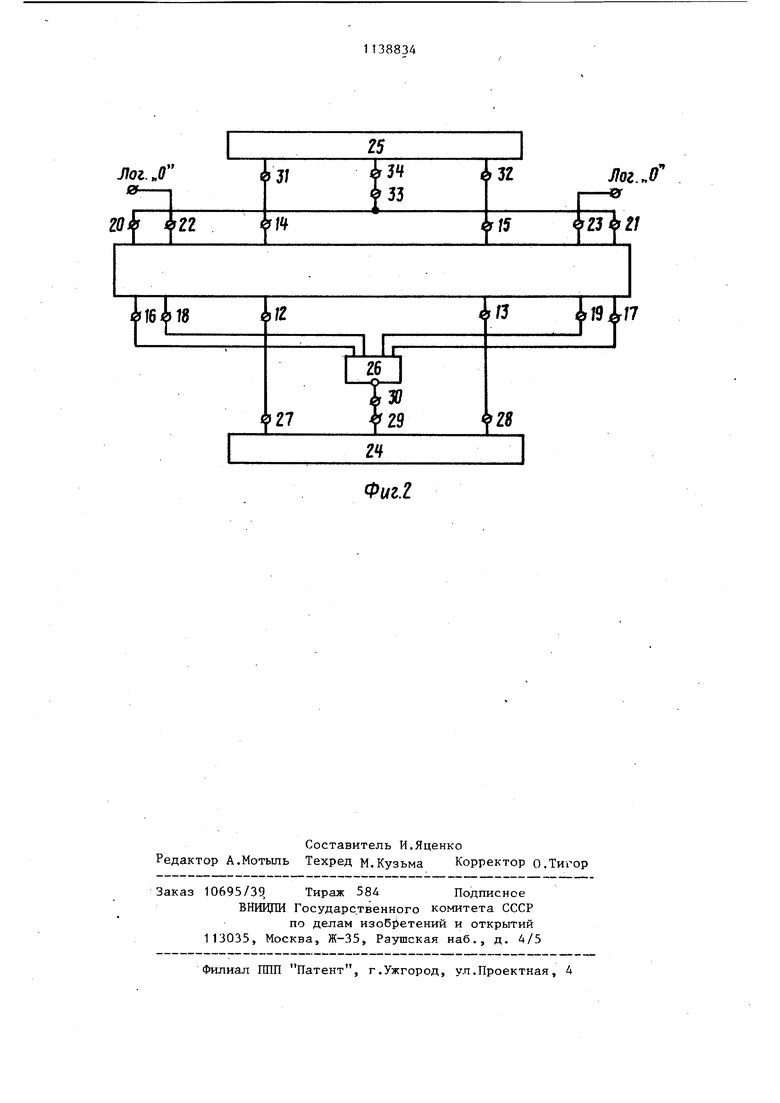

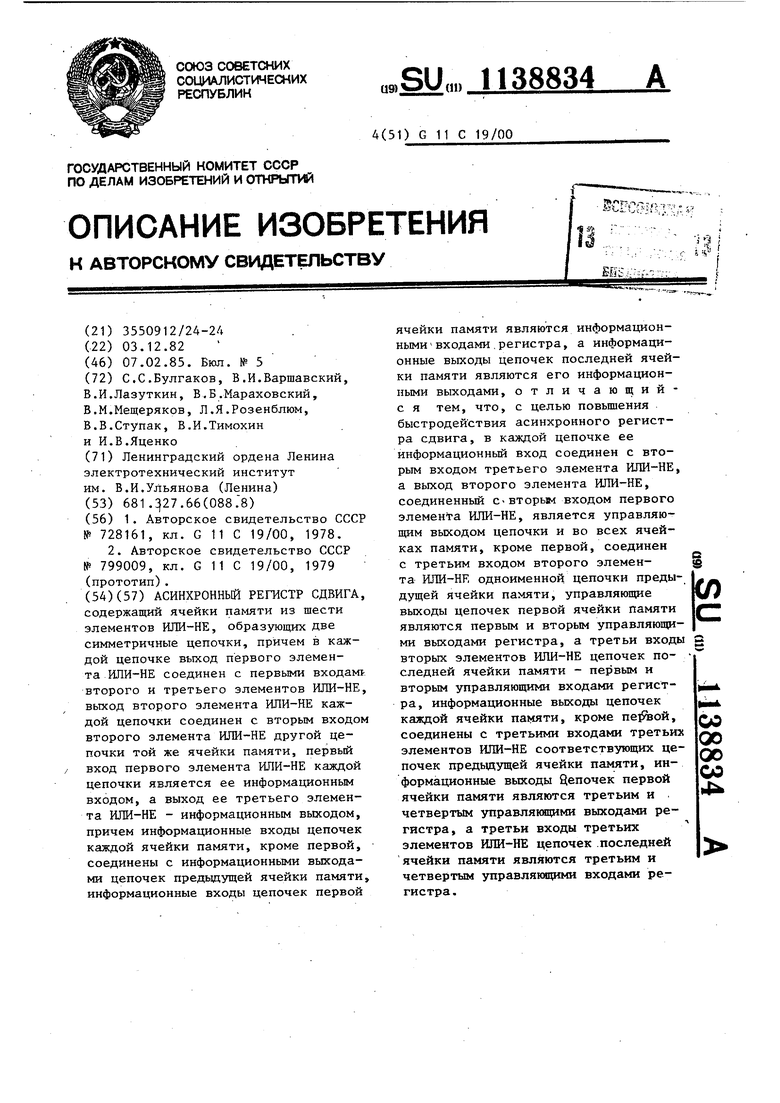

первого элемента ИЛИ-НЕ каждой цепочки является ее информационным входом, а выход ее третьего элемента ИЛИ-НЕ информационным выходом, причем инфорQ мационные входы цепочек каждой ячейки памяти, кроме первой, соединены с информационными выходами цепочек предыдущей ячейки памяти,, информационные входы цепочек первой ячейки 5 памяти являются информационными входами регистра, а информационные выходы цепочек последней ячейки памяти являются его информационными выходами, в каждой цепочке ее информацибнQ ный вход соединен с вторым входом третьего элемента , а выход второго элемента ИПИ-НЕ, соединенный с вторым входом первого элемента ИЛИ-НЕ, является управляющим выходом цепочки и во всех ячейках памяти, кроме первой, соединен с третьим входом второго элемента ИЛИ-НЕ одноименной цепочки предьвдущей ячейки памяти, управляющие выходы цепочек первой ячейки памяти являются первым и вторым управляющими выходами регистра, а третьи входы вторых элементов ИЛИ-НЕ цепочек последней ячейки памяти - первым и вторым управляющими входами регистра, информационные выходы цепочек каждой ячейки памяти,- кроме первой, соединены с третьими входами третьих элементов ИЛИ-НЕ соответствующих цепочек предыдущей ячейки памяти, информационные выходы цепочек первой ячейки памяти являются третьим и четвертым управляющими выходами регистра, а третьи входы третьих элементов ИЛИНЕ цепочек последней ячейки памяти являются третьим и четвертым управляющими входами регистра. На фиг. 1 изображена схема предлагаемого регистра сдвига; на фиг.2 схема подключения регистра к источнику и приемнику информации. Регистр 1 содержит ячейки 2 памя ти, каждая из которых состоит из двух симметричных цепочек 3, образо ванных тремя элементами ИЛИ-НЕ 4В каждой цепочке 3 выход элемента 4 соединен с первыми входами элементов 5 и 6, выход элемента 6 соедине с первым входом элемента 4. Второй вход элемента 4, соединенный с вторым входом элемента 6, является информационным входом 7 цепочки 3, а выход элемента 6 - ее информацион ным выходом 8. Между цепочками 3 каж дой ячейки 2 существует триггерная связь, образованная соединением вых да элемента 5 каждой цепочки 3 с вт рым входом элемента 5 другой цепочки 3. Выход элемента 5 каждой цепоч ки 3 является ее управляющим выходом 9, а третьи входы элементов 5 и 6 - первым 10 и вторым 11 управля щими входами. Информационные входы обеих цепочек 3 каждой ячейки 2, кр ме первой, соединены с информационными выходами 8 соответствующих цеп чек 3 предыдущей ячейки 2, а информ ционные выходы 8 обеих цепочек 3 ка дой ячейки 2, кроме последней, соед нены с информационными входами 7 со ответствуюпщх цепочек 3 предьщущей ячейки 2. Информационные входы 7 цепочек 3 первой ячейки-2 являются первым 12 и вторым 13 информационны входами регистра 1, а информационны выходы 8 цепочек 3 последней ячейки 2 - его первым 14 и вторым 15 информационными выходами. Управляющие выходы 9 цепочек 3 каждой ячейки 2, кроме первой, соединены с первыми управляющими входами 10 соответствующих цепочек 3 предыдущей ячейки 2, а управляющие входы 10 и 11 цепочек 3 каждой ячейки 2, кроме последней, соединены соответственно с управляющим 9 и информационным 8 выходами соответствующей цепочки 3 предыдущей ячейки 2. Управляющие выходы 9 цепочек 3 первой ячейки 2 являются первым 16 и вторым 17 управляющими выходами регистра 1, а информационные . выходы 8 - его третьим 18 и четвертым 19 управляющими выходами. Управляющие входы 10 цепочек 3 последней ячейки 2 являются первым 20 и вторым 21 управляющими входами регистра 1 , а управляющие входы 11 - его третьим 22 и четвертым 23 управляющими входами. В состав схемы (фиг. 2) входят регистр 1, источник 24 информации, приемник 25 информации и вспомогательный элемент ИЛИ-НЕ 26. Информационные выходы 27 и 28 источника 24 соединены соответственно с первмм 12 и вторым 13 информационными входами регистра 1. Управляющий вход 29 источника 24 соединен с выходом 30 вспомогательного элемента 26, первый, второй, третий и четвертый входы которого соединены соответственно с первым 16, вторым 17, третьим 18 и четвертым 19 управляющими выходами регистра 1. Информационные выходы 14 и 15 регистра 1 соединены соответственно с первым 31 и вторым 32 информационными входами приемника 25. Управляющие входы 20 и 21 регистра 1 объединены в один управляющий вход 33, соединенный с управляющим выходом 34 приемника 25. Управляющие входы 22 и 23 регистра 1 соединены с источником постоянного сигнала логического О. В устойчивом состоянии регистра 1 каждая из цепочек 3 ячейки 2 может находиться либо в рабочем состоянии, либо в состоянии гашения. Рабочее состояние соответствует наличию информации в цепочке 3 (комбинация 001 на выходах элементов 4-6), а состояние гашения - отсутствию информации (комбинация 100 31 на выходах элементов 4 - 6). Триггерная связь между элементами 5 двух цепочек 3 ячейки 2 предотвращает запись информации одновременно в обе цепочки 3 ячейки 2. Если цепоч ка 3 i-й ячейки 2 находится в рабочем состояйии, то сигналы на ее информационном 8 и управляющем 9 выходах запрещают запись информации в од ноименную цепочку 3 (1-1)-й ячейки 2 Поэтому следующие одна за другой информационные единицы (нули) не могут находиться в регистре 1 в цепочках 3 двух смежных ячеек 2, а обязательно разделяются цепочкой 3, находящейся в состоянии гашения, причем симметричная ей цепочка 3 той же ячейки 2 может находиться как в состоянии гашения, так и в рабочем соетоянии, т.е. хранить информацию. Таким образом, следующие одна за другой информационные единицы (нули) в регистре (в устойчивом его состоянии) через разряд (Неплотно), а че редующиеся 01010 - в соседних разрядах (Плотно) . При неплотном заполнении для хранения одного бита требуются две ячейки 2, при плотном заполнении - одна ячейка 2. Можно считать , что один бит информации занимает в среднем 1,5 ячейки 2, а способ хранения назвать полуплотным. Сдвиг информации в регистре проис ходит следующим образом. Единица, записанная в j-ю ячейку 2 регистра 1, перемещается в (; + 1)-ю ячейку 2, если .(1-И)-я ячейка 2 и соответствующая цепочка 3 (|+2)-й ячейки 2 находятся в состоянии гашения. При этом на информационном 8 и управляющем 9 выходах цепочки 3 (+1)-й ячейки 2 присутствуют сигналы разрешения записи информа ции. Информационный сигнал с выхода элемента 6 цепочки 3 i-й ячейки памя ти через шину 8 поступает на вход 7 одноименной цепочки 3 (f+1)-й ячейки 2, вызывая поочередное переключение элементов указанных цепочек 3 i-й и (1+1)-и ячеек 2 в следующей последовательности: 4 - - 5 j+i-5 4 -6 -6- (индекс у номера элемента обозначает номер ячейки 2, в состав которой этот элемент входит) .. В результате цепочка 3 (+1)-й ячейки устанавливается в рабочее сос тояние (011 на выходах элемен346уов 4. , 5j , 6,), а цепочка 3 i-й ячейки - в состояние гашения (100 на выходах элементов , 5, 60- Таким образом,, время сдвига информации на один разряд составляет в предлагаемом регистре 6f, где tсредняя задержка элемента ИЛИ-НЕ, и не зависит от числа ячеек регистра. Последовательное переключение элементов цепочек обеспечивает устойчивость процесса продвижения информации, так как делает его не зависящим от величин задержек элементов и их соотношения . При продвижении по регистру информации распределяется автоматически Плотно или Неплотно в зависимости от внутренних состояний ячеек и состояний их входов. . Взаимодействие первой ячейки 2 регистра 1 с источником 24 информации и приемником 25 информации осуществляется по принципу согласованного обмена или по принципу Запрос Ответ. При этом информационные и управляющие сигналы регистра 1, а также информационные сигналы источника 24 и приемника 25 информации представлены в парафазном коде. Парафазные сигналы на управляющих- выходах 16-19 преобразуются в однофазный сигнал на выходе 30 элемента 26, управляющий передачей информации из приемника в регистр. В исходном состоянии на информационных выходах 27 и 28 источника установлен парафазный код 00 (отсутствие информации) , регистр 1 пуст (все цепочки 3 находятся в состоянии гашения), сигнал О на выходе 30 элемента 26 означает для источника разрешение установки информационного, кода (01 или 10) на выходах 27 и 28. Информационный код поступает на входы 12 и 13 регистра 1 и через 3fфиксируется одной из цепочек 3 первой ячейки 2, о чем свидетельствует появление сигнала 1 на выходе 30 элемента 26. По этому сигналу источник 24 должен перевести информационные вы- ходы 27 и 28 в состояние гашения (00), которое означает разрешение продвижения информации во вторую . ячейку 2 регистра 1 . ПocJieдний способен отреагировать на этот переход через 2 (время переключения элементов 4 и 6,) . Далее за время 51 происходит последовательное переключение пяти элементов одноименных цепочек 3 первой и второй ячеек 2, после чего пере1а1ючается элемент 26 в состояние О. Этот сигнал означает для источника 24 разрешение установки на выходах 27 и 28 нового информационного кода. Если очередной передаваемьй бит отличается от предьщущего, то он принимается в регистр сразу после появления на информационных входах 12 и 13 регистра 1, так как предь1п;ущий бит передается по дру гому плечу регистра. Если очередной передаваемый бит совпадает с предыду щим, то до момента его приема проходит еще 4f. Это время необходимо для того, чтобы предыдущий бит информации зафиксировался в третьей ячейке 2, а соответствующие.цепочки 3 первой к второй ячеек 2 перешли в. состояние гашения. Первая ячейка 2 при приеме информации всегда проходит через соетояние гашения, а далее информация распределяется по регистру автомати чески, не зависимо от источника. Пе риод следования информационных сигналов Tj на входе регистра 1 при плотном заполнении определяется по формуле Тз ( 2v)+5V+i:l где - время переключения источника в состояние Т° - то же, но в состояниеМО или 01. При Т Ч2Ги , . В случае неплотного заполнения Тз Зг+тах(, 2t)-(-5t+max( или Тз 14Тпри Т ;° ;2гги . в процессе считывания информации из регистра 1 приемник 25 управляет передачей информации с помощью сигнала на управляющем выходе 34, кото рый поступает на управляющий вход 3 регистра 1. В исходном состоянии, когда приемник 25 не может принять информацию, сигнал 1 на выходе 34 препятствует переходу последней яче ки 2 регистра 1 в рабочее состояние т.во первый записанный в регистр 1 бит хранится в предпоследней ячейке 2. На информационныхвыходах 14 и 15 регистра 1 установлен код 00 (отсутствие информации). Постоянные сигналы О на входах 22 и 23 регис ра 1 не препятствуют переключению элементов 6 последней ячейки 2, сигналы 1 на, управляющих входах 20 и 21 регистра 1 поддерживают обе цепочки 3 последней ячейки 2 в состоянии гашения. Если приемник 25 готов к приему информации, он устанавливает на выходе 34 сигнал О, разрешающий переключение одной из цепочек 3 последней ячейки 2, которая через 5 Т приходит в рабочее состояние. При этом на информационных выходах 14 и 15 регистра 1 устанавливается код 10 или 01. Далее приемник 25 за время l принимает информацию и изменяет .сигнал на выходе 34 , что вызывает гашение соответствующей цепочки 3 последней ячейки 2 регистра 1 за время :Я:. После гашения последней ячейки 2 регистра 1 приемник 25 может вновь подавать сигнал запроса на считывание (изменение сигнала на выходе 34 из 1 в О за время ) Таким образом, при считывании информации из плотно заполненного регистра период следования информационных сигналов выражается формулойТ,5Ег+Т°-;+Зсч-т;-° , или т ЯХ ггт-iTj т т -П IC, при i fif, -i fjp -U. При неплотном заполнении регистра, когда следующие один за другим биты разделены цепочкой 3, находящейся в состоянии гашения, требуется дополнительное время, в течение которого регистр готовится к реакции на смену сигнала на выходе 34 приемника 25. Поэтому время ТJ pможет быть увеличено до 2V, а - до 4С. Формула для Т;;, принимает вид 5С-+тах(Т°- ,2Г) +3С+тах(), или при т ,рЧ2гг и 4т, Тсх сравнению с известным предлагаемый асинхронный сдвига при том же числе разрядов п дает пропорциональный п выигрьш по быстродействию, так как время сдвига бита информации на один разряд в предлагаемом регистре не зависит от числа разрядов п. Характеристики сложности ячейки известного и предлагаемого регистров одинаковы и равны 22 (суммарное количество входов и выходов элементов ИЛИ-НЕ, входящих в сос|тав ячейки) .

20 22

Щ

23 2f

/5 jgf

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1410103A1 |

| Устройство для моделирования графов | 1984 |

|

SU1231509A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| МОЛЕКУЛЯРНО-ЭЛЕКТРОННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2068586C1 |

| Устройство синтаксически управляемого перевода | 1989 |

|

SU1651298A1 |

АСИНХРОННЫЙ РЕГИСТР СДВИГА, содержащий ячейки памяти из шести элементов ИЛИ-НЕ, образующих две симметричные цепочки, причем в каждой цепочке выход первого элемента ИЛИ-НЕ соединен с первыми входамь второго и третьего элементов ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ каждой цепочки соединен с вторым входом второго элемента ИЛИ-НЕ другой цепочки той же ячейки памяти, первый вход первого элемента ИЛИ-НЕ каждой цепочки является ее информационным входом, а выход ее третьего элемента ИЛИ-НЕ - информационным выходом, причем информационные входы цепочек каждой ячейки памяти, кроме первой, соединены с информационными выходами цепочек предыдущей ячейки памяти, информационные входы цепочек первой ячейки памяти являются информационными входами .регистра, а информационные выходы цепочек последней ячейки памяти являются его информационными выходами, отличаюп1;ийс я тем, что, с целью повышения быстродействия асинхронного регистра сдвига, в каждой цепочке ее информационный вход соединен с вторым входом третьего элемента ИЛИ-НЕ, а выход второго элемента ИЛИ-НЕ, соединенный с-вторьж входом первого элемента ИЛИ-НЕ, является управляющим выходом цепочки и во всех ячейках памяти, кроме первой, соединен с третьим входом второго элемента ИЛИ-НЕ одноименной цепочки преды(Л дущей ячейки памяти, управляющие выходы цепочек первой ячейки памяти являются первым и вторым управляющими выходами регистра, а третьи входы вторых элементов ШШ-НЕ цепочек последней ячейки памяти - первым и вторым управляющими входами регистра, информационные выходы цепочек каждой ячейки памяти, кроме , со соединены с третьими входами третьих 00 элементов ИЛИ-НЕ соответствующих цеоо 00 почек предыдущей ячейки памяти, информационные выходы Яепочек первой ячейки памяти являются третьим и . четвертым управлякицими выходами регистра, а третьи входы третьих элементов ИЛИ-НЕ цепочек .последней ячейки памяти являются третьим и четвертым управлякицими входами регистра.

Фмг.1

Фиг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Асинхронный регистр сдвига | 1978 |

|

SU728161A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Регистр сдвига | 1979 |

|

SU799009A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-02-07—Публикация

1982-12-03—Подача