Изобретение относится к автоматике и вычислительной технике и может быть использовано при иостроении асинхронных устройств приема и передачи информации.

Целью изобретения является упрощение регистра.

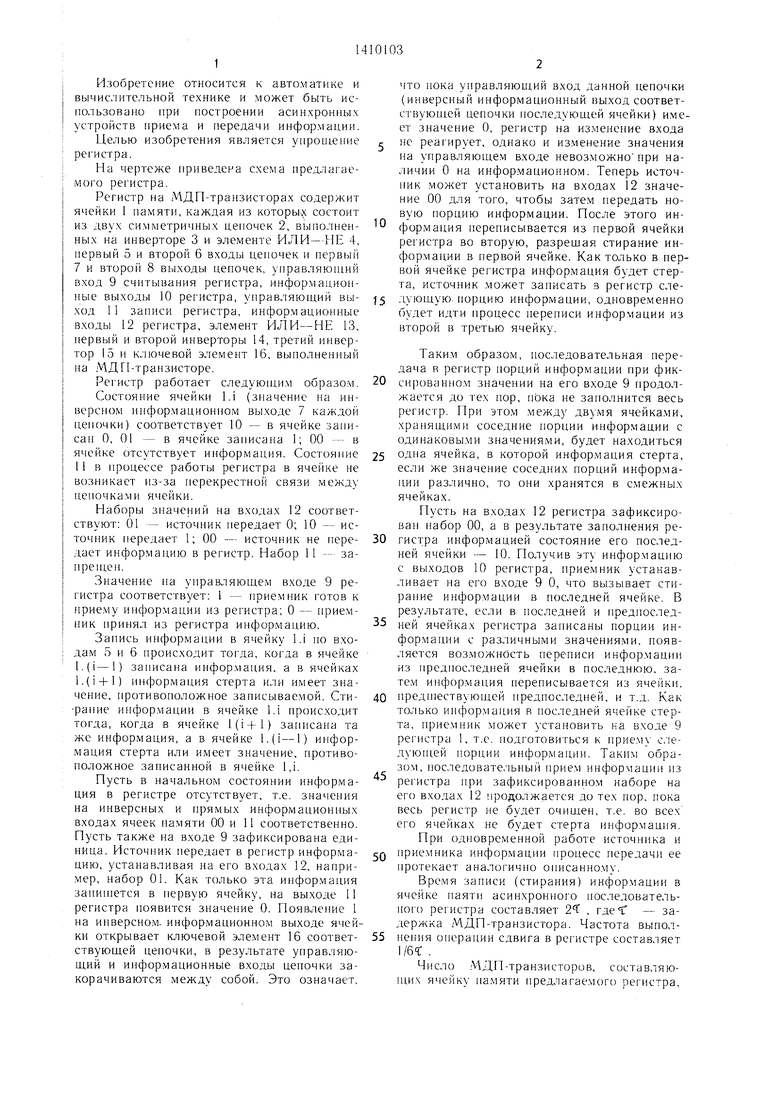

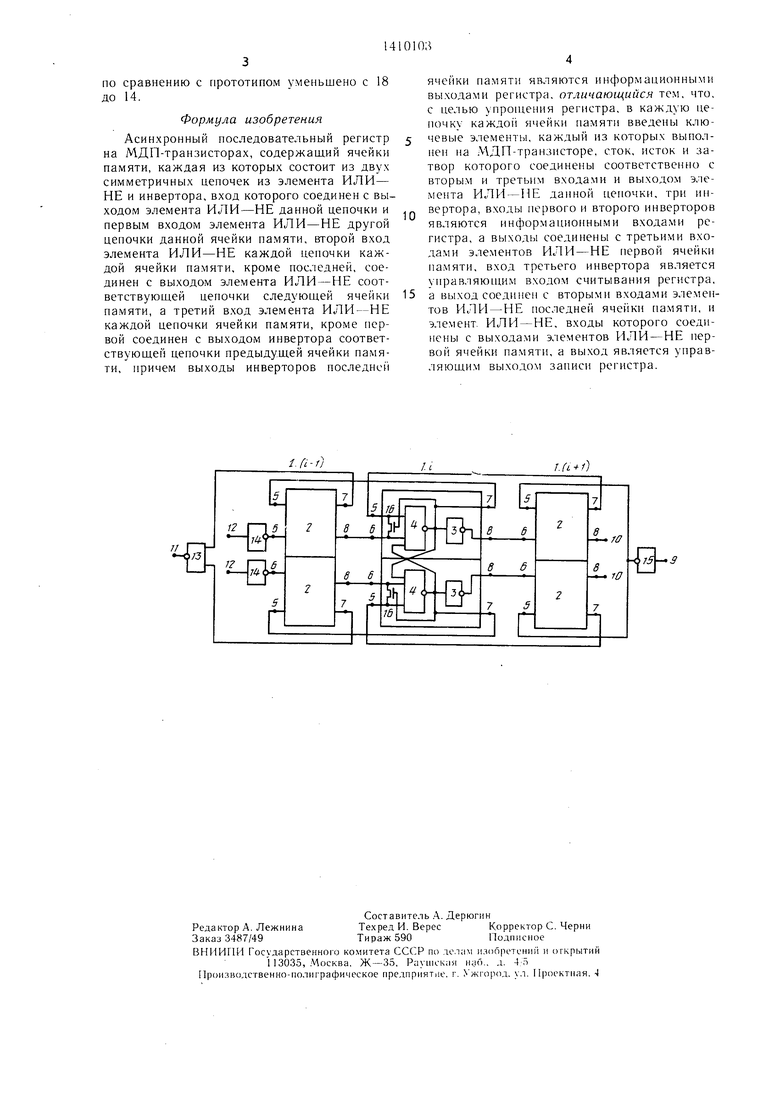

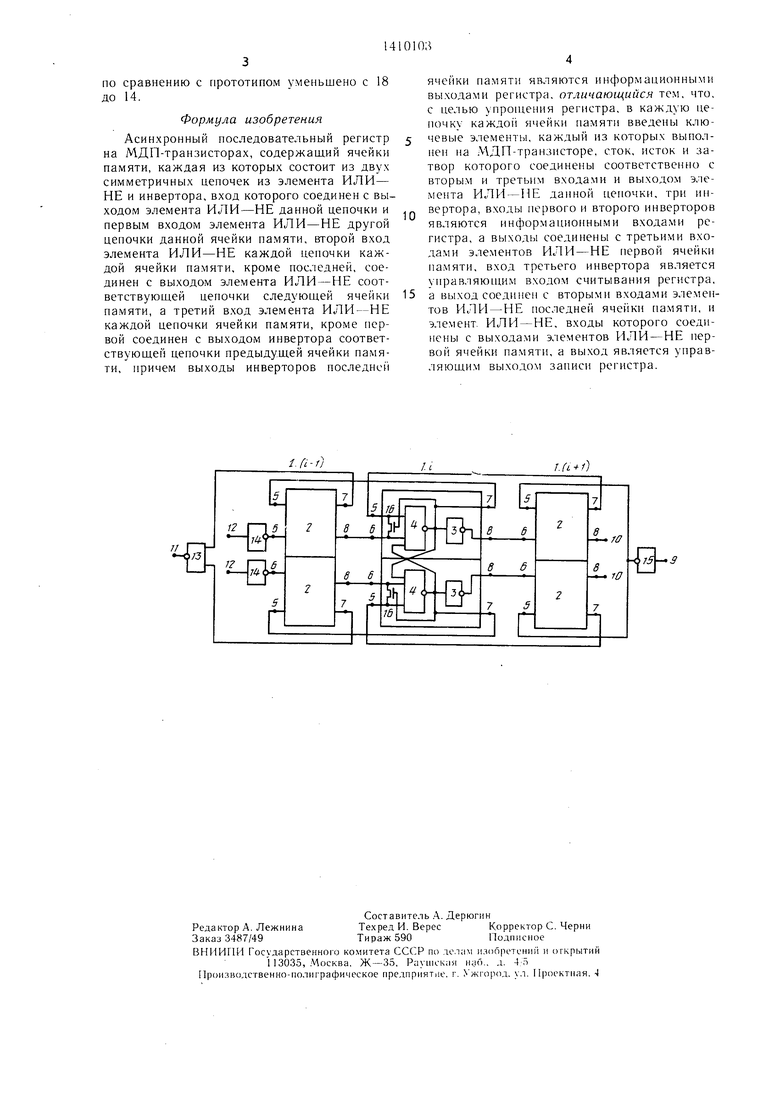

На чертеже нриведена схема предлагаемых) pei-истра.

Регистр на МДП-транзисторах содержит ячейки 1 памяти, каждая из которы-х состоит из двух симметричных цепочек 2, выполненных на инверторе 3 и элементе ИЛИ--МЕ 4, первый 5 и второй 6 входы цепочек и первый 7 и BTopoii 8 выходы цепочек, управляющий вход 9 считывания регистра, ипфор.чацион- пые выходы 10 регистра, управляющий выход 11 записи регистра, информационные входы 12 регистра, элемент ИЛИ-НЕ 13, иервый и второй инверторы 14, третий иивер- тор 15 и к;1ючевой элемент 16, выполненный на МДП-трапзисторе.

Регистр работает следующим образом.

Состояние ячейки l.i (значение па инверсном информационном вы.ходе 7 каждой цепочки) соответствует 10 - в ячейке записан О, 01 - в ячейке записана 1; 00 - в ячейке отсутствует информация. Состояние I1 в процессе работы регистра в ячейке не возникает из-за перекрестной связи между цепочками ячейки.

Наборы зпачений иа входах 12 соответствуют: 01 - источник передает 0; 10 - источник передает 1; 00 - источник не передает информацию в регистр. Набор 11 - запрещен.

Значение на уиравляюще.м входе 9 регистра соответствует: 1 - ириемник готов к приему информации из регистра; О - приемник иринял из регистра ипфор.мацию.

Запись информации в ячейку l.i по входам о и 6 происходит тогда, когда в ячейке l.(i-1) записана информация, а в ячейках l.(i + l) информация стерта или имеет значение, противоположное записываемой. Сти- рапие ипформации в ячейке l.i ироисходит тогда, когда в ячейке l(i+l) записана та же информация, а в ячейке l.(i-1) информация стерта или имеет значение, противоположное занисанной в ячейке l,i.

Пусть в начальном состоянии информация в регистре отсутствует, т.е. значения на инверсных и прямых информационных входах ячеек Памяти 00 и 11 соответственно. Пусть также на входе 9 зафиксирована единица. Источник иередает в регистр информацию, устанавливая на его входах 12, например, набор 01. Как только эта информация за1щщется в первую ячейку, на выходе 11 регистра появится значение 0. Появление 1 на инверсно.м. инфор.мационном выходе ячейки открывает ключевой элемент 16 соответствующей цепочки, в результате управляющий и информационные входы цепочки закорачиваются между собой. Это означает.

что пока управляющий вход данной цепочки (инверсный информационный выход соответствующей цепочки последующей ячейки) и.ме- ет значение О, регистр на из.менение входа не реагирует, однако и изменение значения на управляющем входе невозможно при наличии О на информационном. Теперь источник может установить на входах 12 значение 00 для того, чтобы зате.м передать новую порцию информации. После этого информация переписывается из первой ячейки регистра во вторую, разрещая стирание информации в цервой ячейке. Как только в первой ячейке регистра информация будет стерта, источник может записать в регистр сле5 дующую норцию информации, одновременно будет идти процесс переписи информации из второй в третью ячейку.

Таким образом, последовательная передача в регистр порций информации при фик0 сированном значении на его входе 9 продолжается до тех пор, пока не заполнится весь регистр. При это.1 между дву.мя ячейка.ми, хранящими соседние порции информации с одинаковыми значениями, будет находиться

5 одна ячейка, в которой информация стерта, если же значение соседних порций информации различно, то они хранятся в смежных ячейках.

Пусть на входах 12 регистра зафиксирован набор 00, а в результате заполнения ре0 гистра информацией состояние его последней ячейки - 10. Получив эту инфор.мацию с выходов 10 регистра, приемник устанавливает на его входе 9 О, что вызывает стирание информации в последней ячейке. В результате, если в носледней и предпослед5

5

ней ячейках регистра записаны порции инфор.мации с различными значениями, появляется возможность переписи информации из предпоследней ячейки в последнюю, затем информация нереписывается из ячейки,

0 предшествующей предпоследней, и т.д. Как только информация в последней ячейке стерта, приемник может становить на входе 9 регистра 1, т.е. подготовиться к прие.мч сле- дуюп1.ей порции информации. Таким образом, последовате.чьный прием информации из pei-истра при зафиксированном наборе на его входах 12 продолжается до тех пор, пока весь регистр не будет очищен, т.е. во всех его ячейках не будет стерта информация. При одиовременной работе источника и

Q .1ника информации фоцесс передачи ее протекает аналогично онисанно.му.

Время записи (стирания) информации в ячейке паяти асинхронного ноеледователь- ного регистра составляет 2 , - задержка МДП-транзистора. Частота выпол5 нения операции сдвига в регистре составляет

1/бч:.

Число МДП-транзисторов, составляющих ячейку памяти предлагаемого регистра.

по сравнению с прототипом уменьшено с 18 до 14.

Формула изобретения Асинхронный последовательный регистр на МДП-транзисторах, содержащий ячейки памяти, каждая из которых состоит из двух симметричных цепочек из элемента ИЛИ-НЕ и инвертора, вход которого соединен с выходом элемента ИЛИ-НЕ данной цепочки и первым входом элемента ИЛИ-НЕ другой цепочки данной ячейки памяти, второй вход элемента ИЛИ-НЕ каждой цепочки каждой ячейки памяти, кроме последней, соединен с выходом элемента ИЛИ-НЕ соответствующей цепочки следующей ячейки памяти, а третий вход элемента ИЛИ-НЕ каждой цепочки ячейки памяти, кроме первой соединен с выходом инвертора соответствующей цепочки предыдущей ячейки памяти, причем выходы инверторов последней

0

5

ячейки памяти являются информационными выходами регистра, отличающийся тем, что, с целью упрощения регистра, в каждую цепочку каждой ячейки памяти введены ключевые элементы, каждый из которых выполнен на Л ДП-транзисторе, сток, исток и затвор которого соединены соответственно с вторым и третьим входами и выходом элемента ИЛИ-НЕ данной юночки, три инвертора, входы первого и второго инверторов являются информационными входами регистра, а выходы соединены с третьими входами элементов ИЛИ-НЕ первой ячейки памяти, вход третьего инвертора является управляющим входом считывания регистра, а выход соединен с вторыми входами элементов ИЛИ-НЕ последней ячейки памятн, и элемент. ИЛИ-НЕ, входы которого соединены с выходами элементов ИЛИ-НЕ первой ячейки памяти, а выход является управляющим выходом записи регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Асинхронный регистр сдвига на МДП-транзисторах | 1986 |

|

SU1411829A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Асинхронный последовательный регистр | 1990 |

|

SU1805501A1 |

| МОЛЕКУЛЯРНО-ЭЛЕКТРОННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2068586C1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1076951A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении асинхронных устройств приема и передачи информации. Целью изобретения является упрощение регистра. Для достижения этой цели каждая ячейка памяти регистра, состоящая из двух элементов ИЛИ-НЕ и двух инверторов, содержит два ключевых элемента, каждый из которых выполнен на МДП-транзисторе, исток, сток и затвор которого соединены соответственно с вторым и третьим входами и выходом соответствующего элемента ИЛИ- НЕ. Число МДП-транзисторов, составляющих ячейку памяти регистра, по сравнению с прототипом уменьщено с 18 до 14. Частота приема (или выдачи) информации составляет 1/6 Я (CL - задержка переключения МДП-транзистора). 1 ил.

/-А-//

/-С

г. А /}

| Ячейка памяти для буферного регистра | 1976 |

|

SU661606A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-15—Публикация

1986-11-17—Подача