дикациеи окончания фазы записи инфор- 5 вает правильное функционирование ре- мации из источника. После этого ис- гистра при любых задержках его эле- точник вновь устанавливает на инфор- ментов и при любом их соотношении, мационных входах 27, 26 регистра зна- Для преобразования информации, чение 11, что вызывает перепись ин20

формации из триггера на элементах 13- 15 в триггер на элементах 10-12 и в элементы И-НЕ 17. Одновременно с этим информация из входной ячейки памяти ;регистра переписывается в первую ячейку памяти и далее, после чего во входной ячейке памяти сначала информация стирается (состояние 000), а потом после переписи в элементы И-НЕ 17 информации из триггера на элементах 13-15, т.е. установления на их выходах значений 01 I или МО, ячейка переходит в состояние, соответствующее хранению информации, записанной в триггере, т.е. 100 или dOl. Запись . информации во входную ячейку памяти регистра и в трехстабильный триггер на элементах 1 0-12-вызывает и змене- ние значения на выходе 28 регистра с 1 на 0. При этом схема соединения регистра с источником оказывается в состоянии, аналогичном исходному, с отличным от него состоянием трех- стабильных триггеров на элементах 10-12 и 13-15.

Если теперь значение О появляется на другом информационном входе регистра (в отличие от предьздущего случая) 5 переключение схемы соединения с источником происходит аналогично описанному, и после гашения источником информации на входах во входную ячейку регистра записывается значение очередного разряда сдвигаемого кода, отличное от значения предыдущего разряда. Если значение О появляется ма том же информационном вхо-, де регистра, что и в предьщущем случае, трехстабильный триггер на элементах 13-15 устанавливается в сост

30

35

записанной в регистр в соответствии с описанной дисциплиной, в парафаз- ную служат элементы ИЛИ-НЕ 21, 22 и 19, 20. Последние два образуют RS- триггер, который устанавливается в единичное или нулевое состояние при 25 появлении значения 1 на выходе 7 первой или третьей цепочки 2 последней ячейки I регистра. Значение 1 на выходе 7 одной из трех цепочек 2 последней ячейки 1 регистра может, появиться при наличии значения О на его управляющем входе 25. При этом, если значение 1 появляется на выходе 7 первой или третьей цепочки 2 последней ячейки 1 памяти, на выходах элементов 21 и 22 устанавливаются значения О в соответ- ствии с состоянием RS-триггера, образованного элементами 19 и 20. Если значение 1 появляется на выходе 7 второй цепочки 2 последней ячейки 1 памяти, на выходах элементов 21 и 22 устанавливаются значения О независимо от состояния этого RS-триггера. После того, как на выходах элементов 21 и 22 появляются значения О, т.е. эти значения появляются на информационных выходах .23 и 24 регистра, на его управляющем входе 25 может быть установлено значение 1, которое вызывает стирание информации в последней ячейке 1 регистра и появление на выходах 7 всех ее цепочек 2 значений О. Б результате этого на выходе одного из элементов 21 и 22 (т.е. на одном из информационных выходов 23 и 24 регистра) появляется значение

1 в соответствии, с состоянием RS- триггера, образованного элементами .,19 и 20.

40

45

50

55

5 вает правильное функционирование ре- гистра при любых задержках его эле- ментов и при любом их соотношении, Для преобразования информации,

20

0

5

записанной в регистр в соответствии с описанной дисциплиной, в парафаз- ную служат элементы ИЛИ-НЕ 21, 22 и 19, 20. Последние два образуют RS- триггер, который устанавливается в единичное или нулевое состояние при 25 появлении значения 1 на выходе 7 первой или третьей цепочки 2 последней ячейки I регистра. Значение 1 на выходе 7 одной из трех цепочек 2 последней ячейки 1 регистра может, появиться при наличии значения О на его управляющем входе 25. При этом, если значение 1 появляется на выходе 7 первой или третьей цепочки 2 последней ячейки 1 памяти, на выходах элементов 21 и 22 устанавливаются значения О в соответ- ствии с состоянием RS-триггера, образованного элементами 19 и 20. Если значение 1 появляется на выходе 7 второй цепочки 2 последней ячейки 1 памяти, на выходах элементов 21 и 22 устанавливаются значения О независимо от состояния этого RS-триггера. После того, как на выходах элементов 21 и 22 появляются значения О, т.е. эти значения появляются на информационных выходах .23 и 24 регистра, на его управляющем входе 25 может быть установлено значение 1, которое вызывает стирание информации в последней ячейке 1 регистра и появление на выходах 7 всех ее цепочек 2 значений О. Б результате этого на выходе одного из элементов 21 и 22 (т.е. на одном из информационных выходов 23 и 24 регистра) появляется значение

1 в соответствии, с состоянием RS- триггера, образованного элементами .,19 и 20.

0

5

0

5

Для,установки регистра в исходное состояние приемник перед началом работы при заф.иксированном значении 11 на информационных входах регистра осуществляет последовательный Прием информации из регистра, пока все ячейки за исключением входной не будут очищены, прием информации из регистра может быть произведен не олее, чрм п раз, где п - число яче- регистра. Информация,) записанная входную ячейку регистра, в началь jjioM состоянии соответствует состоя- ;Йию трехстабильного триггера на эле- ентах 13-15 и не соответствует ни .icaKoft информации, передаваемой источником в регистр, поэтому в процес te работы с регистром приемник пер-- Ьую порцию информации, принятую посл |1ачала передачи информации источни- oMj игнорирует так же, как и те, iiTO приняты им из регистра в процесс kro начальной установки.

Описанный регистр служитj напри- Mepj ДД1Я согласования работы устройств., связанных асинхронным последовательным интерфейсом, предполагающим наличие в калсдом передаваемом байте стартового и стокового (одного |или,двух) битов. Так, например, ра Ьотает интерфейс на основе микросхе- КР580ВВ51 . Сохранение во входной рчейке памяти регистра стокового бита при передаче очередного байта до прихода стартового бита последу1ощего байта не приводит к ошибкам в передаче информации.

Быстродействие регистра без учета схемы соединения его с источником составляет , где сГ ,- задержка МДП- транзистора, схема соедш ения вносит задержку в работу регистра, с учетом которой его быстродействие (время между записью соседних разрядов сдвигаемого кода) составляет б€ , против lot в прототипе.

Оценивая затраты оборудования числом транзисторов на реализацию ячейки регистра, получим 2.4 МДП-транзис- тора для предложенного регистра и 36 МДП-транзисторов для прототипа.

Формулаизрбре тения

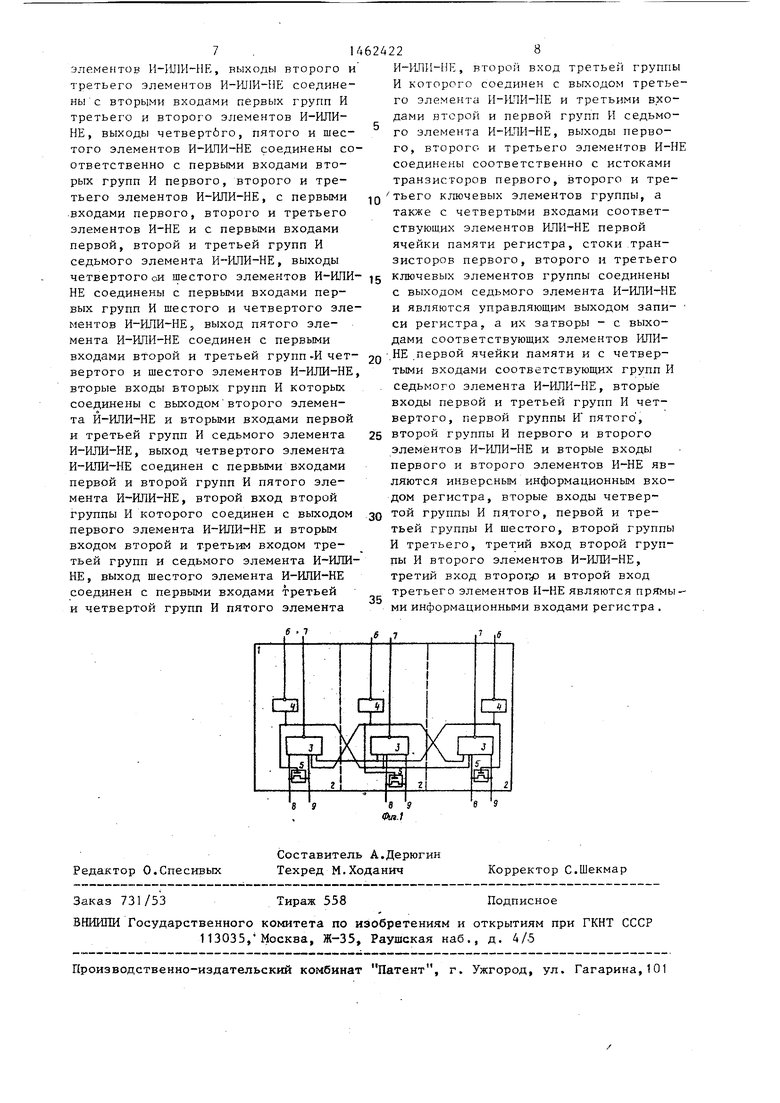

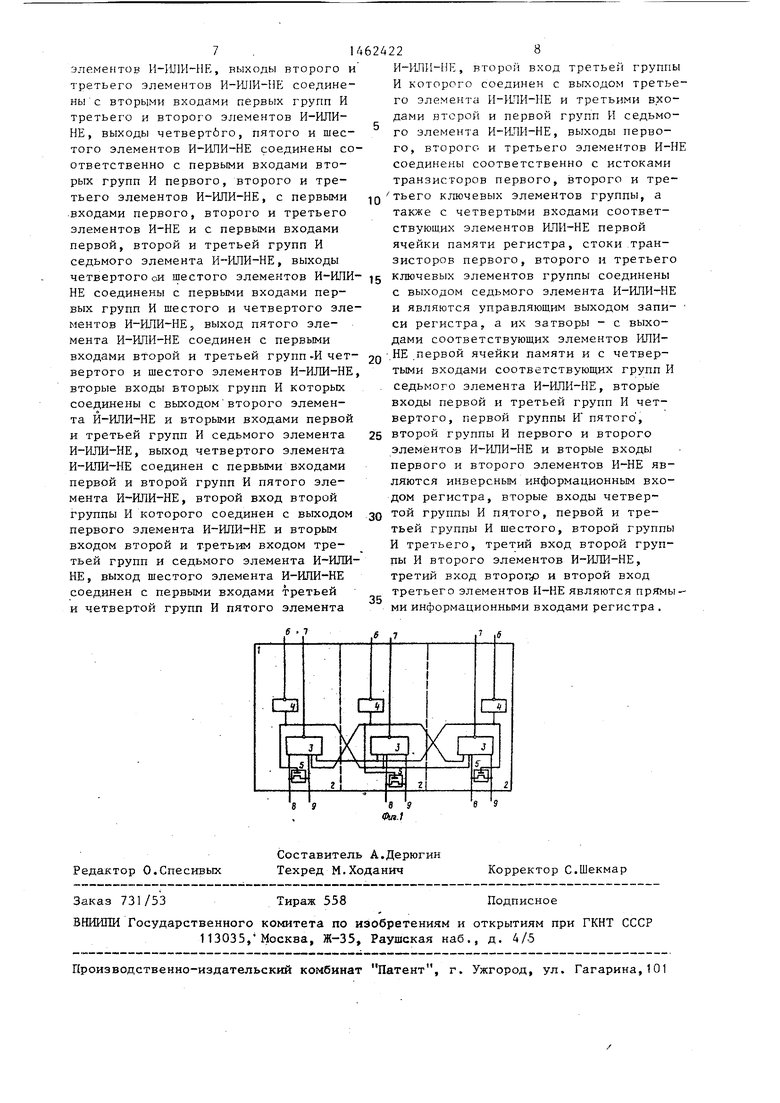

Асинхронный последовательный регистр, содержащий ячейки памяти каждая из которых кроме последнейд состоит из трех элементов ИЛИ-НЕ и

трех инверторов, входы которых соединены с выходами соответствующих элементов , а последняя ячейка памяти состоит из трех элементов ИЛИ-НЕ, причем в каждой ячейке памяти первый и второй входы каждого элемента ИЛИ-НЕ соединены соответственно с выходами других элементов

ИЛИ-НЕ, а третий вход каждого элемента ИЛИ-НЕ каждой ячейки памяти, кроме последней, соединены с выходом соответств5пощего элемента ИПИ-НЕ последующей ячейки памяти, а третьи

входы элементов ИЛИ-НЕ последней ячейки памяти являются управляющим входом считывания регистра, и группу элементов,ИЛИ-НЕ, выходы первого и второго элементов ИЛИ-НЕ группы соедикены соответственно с первыми входами второго и первого элементов ЛПИ-НЕ группы и с первьв ш входами третьего и четвертого элементов ИЛИ- НЕ группы, которых являются

соответственно прямым и инверсным выходами регистра, отличающийся тем, что, с целью упрощения регистра и повышения его быстродействия, в регистр введены семь элементов И-ИЛИ-НЕ, три элемента,И-НЕ и группа ключевых элементовs каждый из которых выполнен на МДП-транзис- торе, и в каждую ячейку памяти введены три ключевых элемента, каждый

из которых выполнен на МДП транзис- торе, сток, исток и затвор которого соединены соответственно с третьим и четвертым входами и выходом соответствующего .элемента, ИЛИ-НЕ ячейки

памяти, выходы первого и третьего элементов ИЛИ-НЕ последней ячейки памяти соединены соответственно с вторыми входами первого и третьего и второго и четвертого элементов ИЛИНЕ группы, а вход второго элемента ИЛИ-НЕ последней ячей1си памяти сое,- динен с третьими входами третьего и четвертого элементов ИЛИ-НЕ группы, выход инвертора каждой ячейки

памяти, кроме последней, соединен с четвертым входом соответствующего элемента ИЛИ-НЕ последующей ячейки памяти, выходы первого и второго элементов И-ИЛИ-НЕ соединены с первьпми

входами первых групп И второго и первого элементов И-ИЛИ-НЕ, выходы первого и третьего элементов И-ИЛИ-НЕ соединены с первым и вторым входами первых групп И третьего и первого

е . 7

S 9

б 7

S

в 9

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1119082A1 |

| Устройство для накопления и обработки информации | 1985 |

|

SU1295408A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1410103A1 |

| Устройство для измерения интервалов времени | 1990 |

|

SU1739361A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении асинхронных устройств приема и передачи информационных посьток, обрамленных стартовым и стоковым битами. Целью изобретения является упрощение асинхронного последовательного регистра и повышает его быстродействия. Цель достигается тем, что каждая ячейка памяти регистра содержит три элемента Ш1И-НЕ, три инвертора и три ключевых элемента. Для согласования с приемником используются семь элементов И-ИПИ-НЕ 10-16, три элемента И 17 и три дополнительных ключевых элемента 18. Для хранения одного разряда регистра требуется одна ячейка памяти. Интервал времени между записью соседних разрядов сдвигаемого кода составляет 6 С против 10 в прототипе (с - задержка переключения МДП-тран- зистора), а число МДП-транзисторов, затрачиваемых на реализащпо одной ячейки памяти, составляет 24 против 36 .в прототипе. 2 ил. S со С

Редактор 0.Спесивых

Составитель А.Дерюгин Техред М.Ходанич

Заказ 731/53

Тираж 558

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035,Москва, Ж-35, Раушская наб., д. 4/5

Корректор С.Шекмар

Подписное

| Авторское свидетельство СССР ,№ 1196954, кл | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1989-02-28—Публикация

1987-01-08—Подача