щим выходом соответствующей цепочки (1+1)-й ячейки памяти, а ее второй управлякмций вход - с управляющим выходом симметричной цепочки (1+1)-й ячейки, при этом информационные входы обеих цепочек первой ячейки памяти регистра являются его информационными входами, а их управляющие выходы - его управляющими выходами, информационные выходы обеих цепочек последней ячейки памяти регистра являются его информационными выходами, а их первые управляющие входы объединены с вторыми управляющими входами симметричных цепочек последней ячейки памяти регистра и являются его управляющими входами, отличающийся тем, что, с целью повышения быстродействия асинхронного регистра сдвига, второй

вход второго элемента И-НЕ каждой цепочки является ее первым управляющим входом, а выход - ее управлякицим выходом и соединен с вторым входом ее третьего элемента И-НЕ, третий и четвертый входы которого являются соответственно вторым и дополнительным управляющими входами цепочки, причем дополнительный управляющий вход каждой цепочки i-й ячейки памяти соединен с управляющим выходом соответствукицей цепочки (1+2)-й ячейки памяти, при этом управляющие выходы обеих цепочек второй ячейки регистра являются его дополнительными управляющими выходами, а дополнительные управляющие входы обеих цепочек последней ячейки памяти регистра - его дополнительными управляющими входами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1410103A1 |

| Устройство для дифференцированного учета материала, перемещаемого конвейерной линией | 1981 |

|

SU972536A2 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

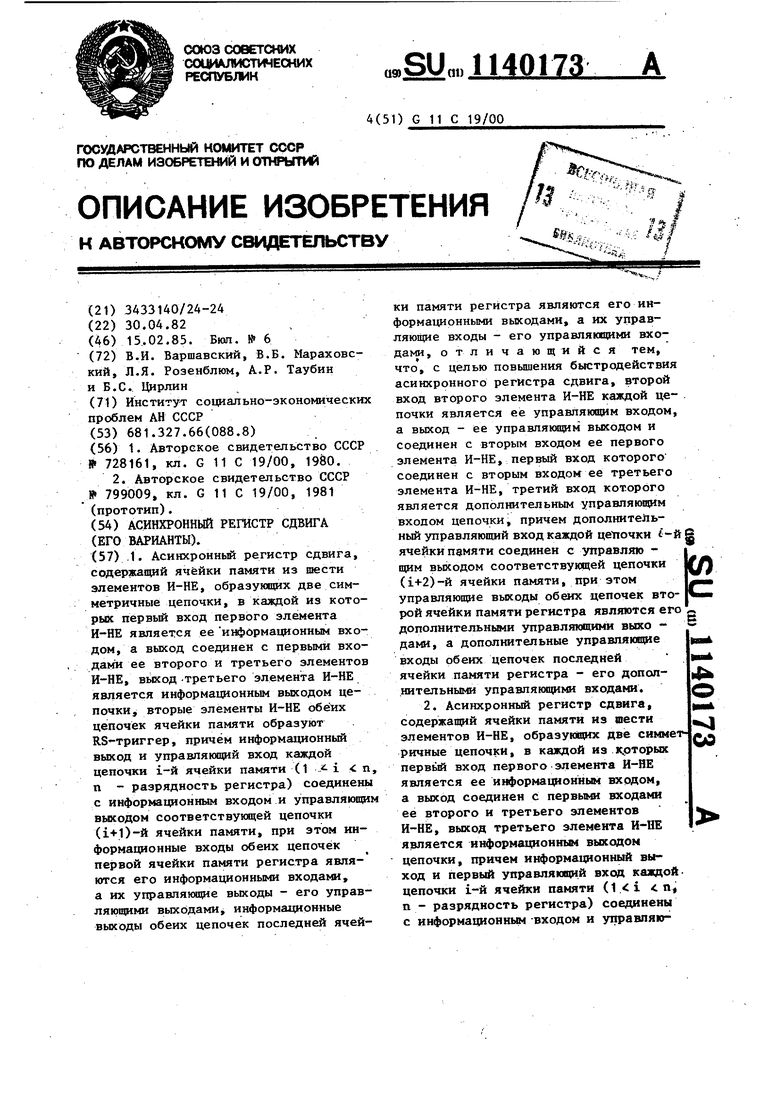

.1. Асинхронный регистр сдвига, содержащий ячейки памяти из шести элементов И-НЕ, образующих две симметричные цепочки, в каждой из которых первый вход первого элемента И-НЕ является ее информационным входом, а выход соединен с первыми входами ее второго и третьего элементов И-НЕ, выход -третьего элемента И-НЕ является информационным выходом цепочки, вторые элементы И-НЕ обеих цепочек ячейки памяти образуют RS-TpHrrep, причём информационный выход и управляющий вход каждой цепочки i-й ячейки памяти

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных машин. Известен асинхронный регистр сдвига, содержащий ячейки памяти из четырех элементов И-НЕ каждая, причем первый, второй и третий элементы И-НЕ ячейки образуют трехстабильньй триггер,первые входы первого и второго элементов И-НЕ являются информационными входами ячейки, а первые . входы ее третьего и четвертого элементов И-НЕ - ее управляющим входом, выходы первого и второго элементов И-НЕ являются информационньв«1 выходами ячейки, а выход третьего элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ выход которого является управляющим выходом ячейки, информационные и управляющий входы 1-й ячейки (,n- разрядность регистра) соединены соответственно с информационными и управляющим выходами (1-1)-й ячейки, два входа первого и второго элементов И-НЕ i-й ячейки и третий вход ее четвертого элемента И-НЕ соединены соответственно с информационными и управляющим выходами (1+1)-й ячейки, а четвертый и пятый входы четвертого элемента И-НЕ i-й ячейки - с выходами (i+2)-й ячейки. Быстродействие этого регистра сдвига достаточно высоко Т. Недостатком известного устройства является избыточность оборудования. Наиболее близким к предлагаемому является асинхронный регистр сдвига, содержащий ячейки памяти из шести элементов И-НЕ, образующих две симметричные цепочки так, что первые элементы обеих цепочек составляют основной, а втсфые - вспомогатепьньй RS-триггеры ячейки, первый, второй и третий входы первого элемента И-НЕ каждой цепочки являются ее информационным, первым и вторым управляющими входами, а .выход первого элемента И-НЕ соединен с первьми входами второго и третьего элементов И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ, а выход является информационным и управляющим выходом цепочки, причем информационный выход и первый управляющий вход каждой цепочки i-й ячейки (1 i п, п - разрядность регистра) соединены с информационным входом и управляющим выходом соответствзпощей цепочки (i+1)-й ячейки, а ее второй управляющий вход - с управляющим выходом противоположной цепочки ()-й ячейки, при этом информационные входы

беих цепочек первой яиейки регистра вляются его- инфоркационньв и входами, их управляющие выходы - его управяющими выходами, информационные выходы об,еих цепочек: последней ячейки 5 егистра являются его информационными выходами, а их управляющие входы его yпpaвля|oщи 0I входами. Констукция описанного регистра достаточно проста 2 J.О

Недостатком известного регистра вляется низкое быстродействие сдвиг на один разряд осуществляется в нем за время от до впУ в зависимости от информации, записан- 15 ной в регистре, где f- задержка элемента И-ЦЕ; п - разрядность регистра.

Цель изобретения - повышение быстродействия асинхронного регистра 20 сдвига.

Поставленная цель достигается тем, что Б асинхронном регистре сдвига, содержащем ячейки памяти из иести элементов И-НЕ, образующих две 25 симметричные цепочки, в каждой из , которых первый вход первого элемента И-НЕ является ее информационным входом, а выход соединен с первьми входами ее второго и третьего эле- 30 ментов И-НЕ, выход третьего элемента И-ИЕ является информадаонным выходом цепочки, вторые элементы И-НЕ обеих цепочек ячейки памяти образуют RS-триггер, причем информационн1й 35 выход и управляющий вход каждой цепочки i-й ячейки памяти (IX i п, п - разрядность регистра) соединены с информационном входом и управляющим выходом соответствукщей цепочки 40 (1+1)-й ячейки памяти, при этом информационные входы обеих цепочек первой ячейки памяти регистра являются его йнформаф1оннь б{ входакш, а их управпякяцие выходы - его управ- 45 ляющими выходами,/ ияформационнвые выходы обеих цепочек последней ячейки памяти регистра являются его информационными выходами, а их управляющие входы - его управляющими входа- 50 ми, второй вход второго элемента И-НЕ каждой цепочки является ее управляющим входом, а выход - ее управпякяцим выходом и соединен с вторым входом ее первого элемента js И-НЕ, первый вход которого соединен с вторым входом ее третьего элемента И-НЕ, третий вход которого

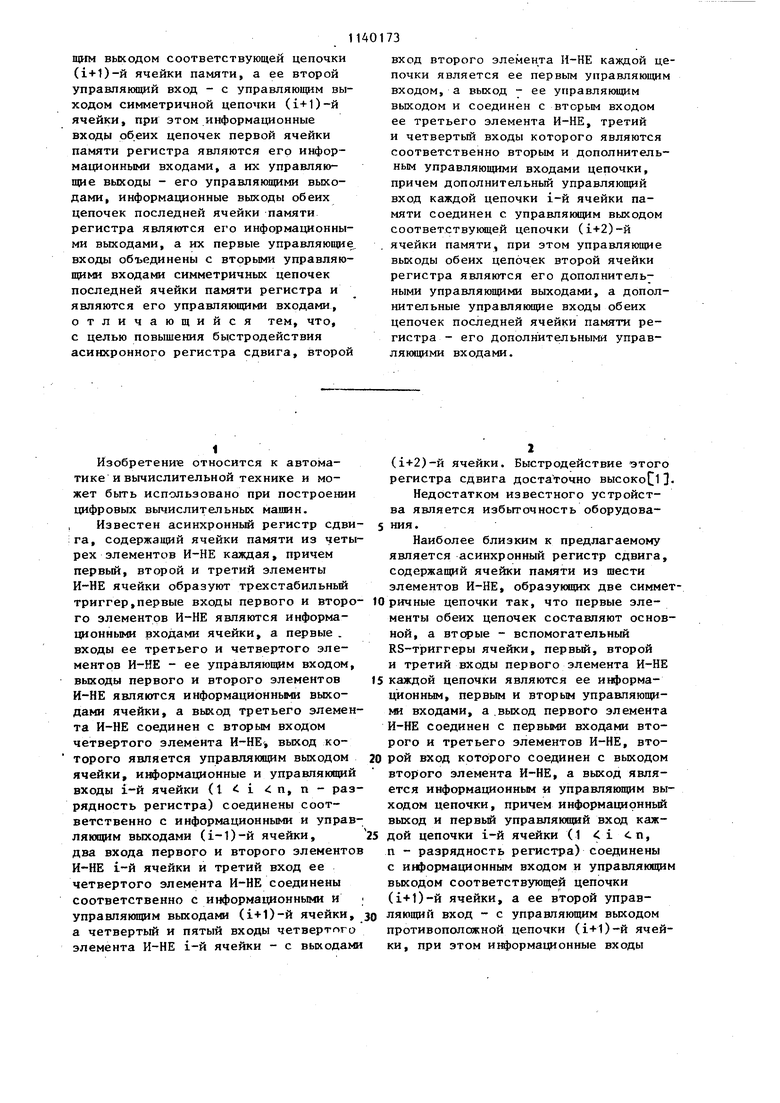

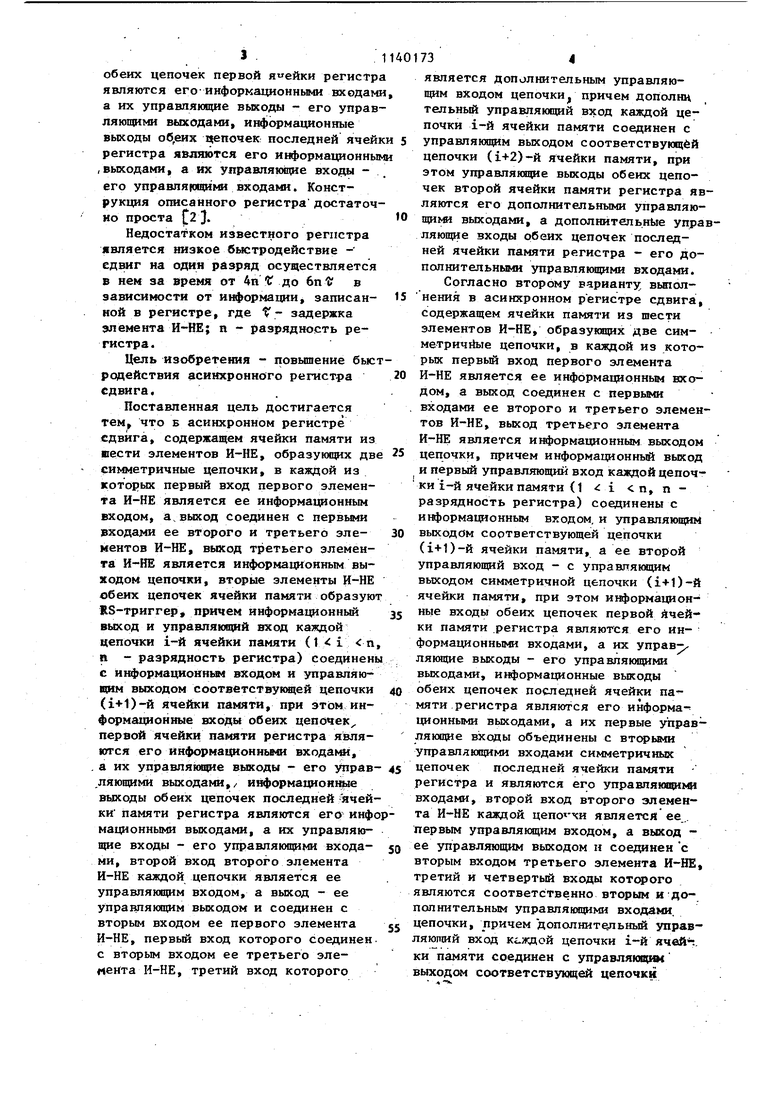

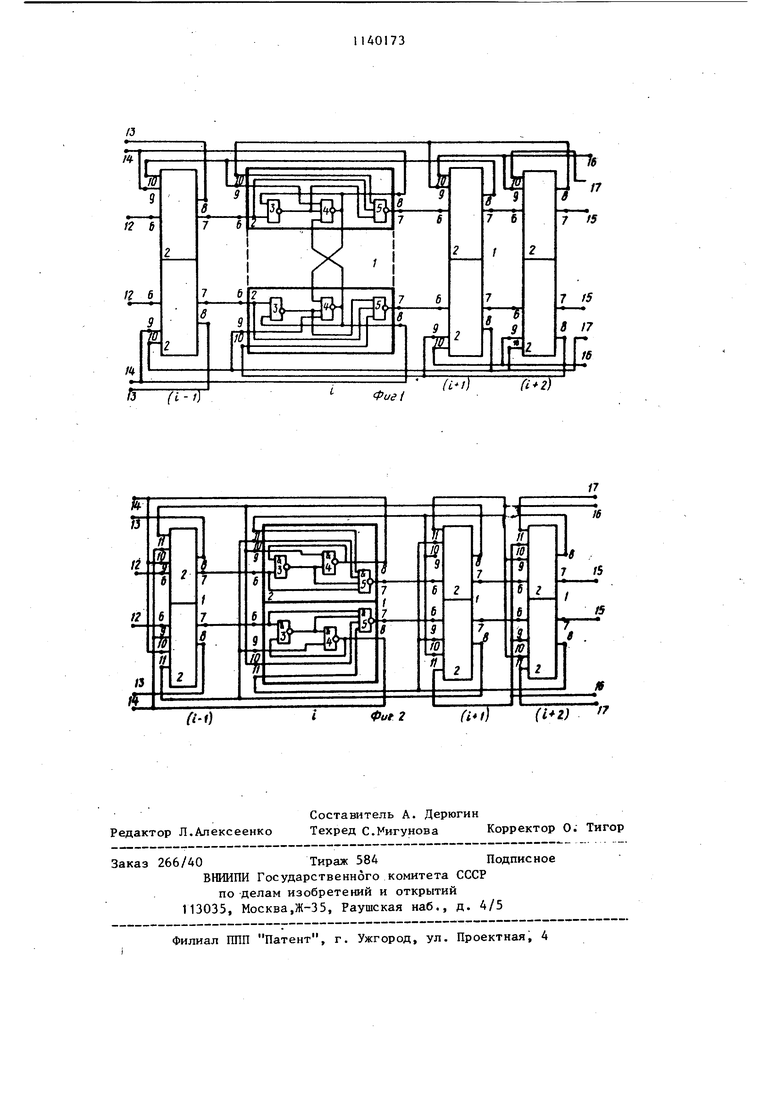

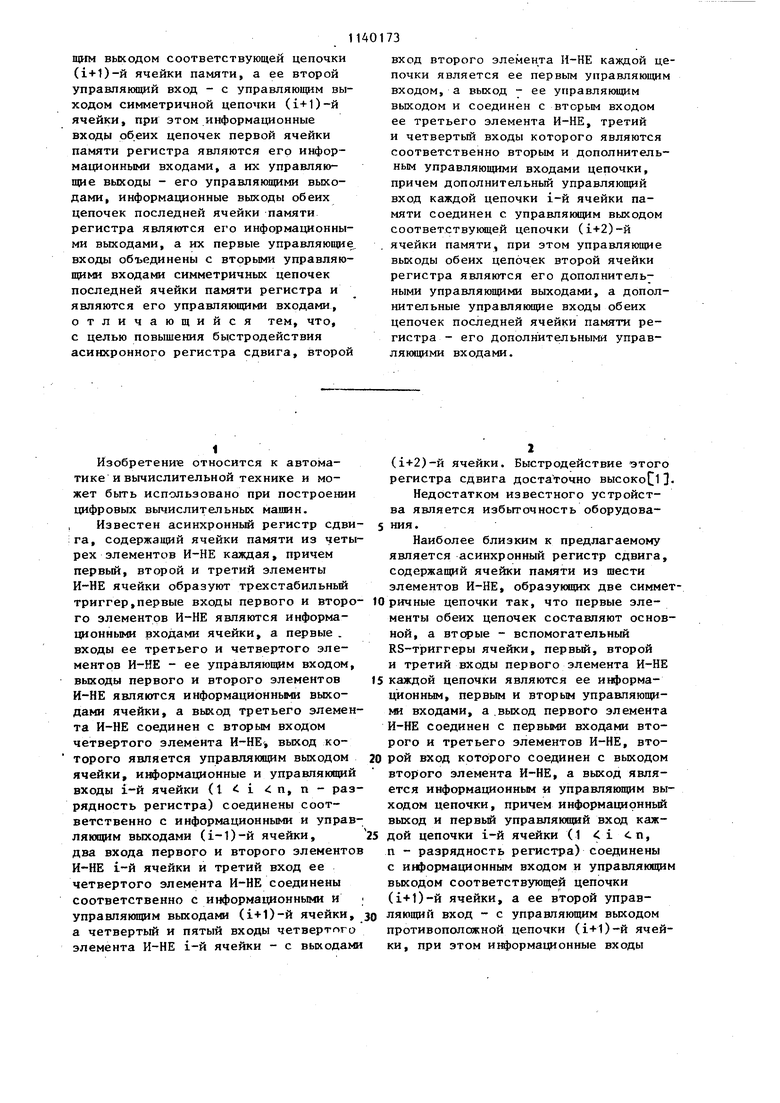

734

является дополнительным управляющим входом цепочки причем дополни тельный управляющий вход каждой цепочки i-й ячейки памяти соединен с управляющим выходом соответствующей цепочки ()-й ячейки памяти, при этом управляющие выходы обеих цепочек второй ячейки памяти регистра являются его дополнительными управляющим выходами, а дополнительные упраляющие входы обеих цепочек последней ячейки памяти регистра - его дополнительными зтравлякицими входами. Согласно второму варианту выполнения в асинхронном регистре сдвига, содержащем ячейки памяти из шести элементов И-НЕ, образующих две симметричйые цепочки, в каждой из которых первый вход первого элемента И-НЕ является ее информационным входом, а выход соединен с первьв и входами ее второго и третьего элементов И-НЕ, выход третьего элемента И-НЕ является информационным выходом цепочки, причем информационный выход и первый управляющий вход каждой цепочки i-й ячейки памяти {1 : i п, п разрядность регистра) соединены с информахщонным входом, и управляквцим выходом соответствующей цепочки (i+1)-й ячейки памяти, а ее второй управляющий вход - с управляющим выходом симметричной цепочки (i+1)-и ячейки памяти, при этом информационные входы обеих цепочек первой йчейки памяти регистра являются его информационными входами, а их управу ляющие выходы - его упра влякнцими выходами, информационные выходы обеих цепочек последней ячейки па мяти .регистра являются его информационными выходами, а их первые управляющие входы объединены с управплющиют входами симметричных цепочек последней ячейки памяти регистра и являются его управпяющи входами, второй вход второго элемен та И-НЕ каждой является ее., первым управляющим входом, а выход ее управляющим выходом и соединен с вторым входом третьего элемента И-НЕ третий и четвертый входы которого являются соответственно вторым и дополнительным управляющими входами, цепочки, причем дополнительный управляюпий вход каждой цепочки i-й ячей-. ки памяти соединен с управляют выходом соответствующей цепочки (i + 2)-и ячейки памяти, при этом управпякнцие выходы обеих цепочек второй ячейки памяти регистра являются его дополнительными управлякяци ми выходами, а дополнительные управлякхще входы обеих цепочек последней ячейки памяти регистра - его дополнительными управляющи1чи входами. На фиг. 1 изображена схема предла гаемого асинхронного регистра сдвига первый вариант выполнения; на фиг.2 то же, второй вариант. Асинхронньй регистр сдвига содержит ячейки 1 памяти, каждая из которых состоит из двух симметричных цепочек 2, образованных тремя элемен тами И-НЕ 3, 4 и 5. Первьй вход элемента 3 цепочки 2 являетсй ее информационным входом 6, а его выход соединен с первыми входами элементов 4 и 5, выход элемента 5 является информа1Д1онным выходом 7 этойцепочки 2. Выход элемента 4 цепочки 2 являет ся ее управляющим выходом 8. Согласно первому варианту (фиг.1 элементы 4 обеих цепочек 2 ячейки 1 образуют RS-триггер, второй вход элемента 4 цепочки 2 является ее управляющим входом 9, а третий вход ее элемента 5. - дополнительным управляющим входом 10. Входы 6, 9 и 10 каждой цепочки 2 i-й ячейки 1 соединены соответственно С выходом 7 соответствующей цепочки 2 (1-1)-й ячейки 1 и выходами 8 соответствующих цепочек 2 (1+1)-й и (1-4-2)-й ячеек 1. Согласно второму варианту (фиг.2 второй вход элемента 4 цепочки 2 является ее первым управляющим входом 9, а третий и четвертый входы ее элемента 5 - вторым управляющим входом 10 и-дополнительным управляющим входом 11 соответственно. Входы 6, 9 и 11 каждой цепочки 2 i-й ячейки 1 соединены с выходом 7 соответствующей цепочки 2 (1-1)-й ячейки 1 и выходами 8 соответствующих цепочек 2 (1+1)-й и (1+2)-й ячеек 1, а вход 10 этой цепочки 2 соединен с выходом 8 противоположной цепочки 2 (1+1)-й ячейки 1. Входы 6 обеих цепочек 2 первой ячейки регистра образуют его информационные входы 12, а выходы 8 этих целочек 2 - его управляющие выходы 13. Выходы 8 обеих цепочек 2 второй ячейки 1 регистра образуют его дополнительные управляющие выходы 14. Выходы 7 обеих цепочек 2 последней ячейки 1 регистра образуют его информационные выходы 15, а входы 9 этих цепочек 2 - его управляющие входы 16, причем согласно второму варианту входы 9 этих цепочек 2 соединены также с входами 10 противопо-тсжных цепочек 2 последней ячейки 1 регистра. Дополнительные управляюнще входы 10 согласно первому варианту и 11 согласно второму варианту обеих цепочек 2 последней ячейки 1 регистра .образуют его дополнительные управляннцие входы 17. Элементы 3 и 4 цепочки 2 образуют RS-триггер. Если в ячейку 1 записана единица или ноль, то в одной из ее цепочек 2 этот RS-триггер установлен в единичное состояние, т.е. на выходе элемента 3 этой цепочки 2 имеется значение 1, а на выходе ее элемента 4 - значение О. При этом во второй цепочке 2 этой ячейки 1 аналогичный RS-триггер находится в нулевом состоянии, т.е. на выходе элемента 3 этой цепочки 2 имеется значение О, а на выходе ее элемента 4 - значение 1. Если же в ячейке 1 информащ1я стерта, то в обеих ее цепочках 2 эти RS-триггеры находятся в нулевом состоянии, т.е. на выходах обоих элементов 3 этой ячейки 1 имеется значение О, а на вькодах обоих ее элементов 4 - значение 1. Установка RS-триггера, образованного элементами 3 и 4 одной из цепочек 2 ячейки 1,3 единичное состояние, т.е. запись информации в эту ячейку 1, осуществляется подачей значения О на информационный вход 6 этой цепочки 2. Установка этих RS-триггеров в нулевое состояние, т.е. стирание информации в ячейке 1, осуществляется подачей значения О на ее управляющий вход 9. Если в i-ю ячейку 1 записана информация, т.е. один из RS-триггеров ее цепочек 2 установлен в единичное Состояние и на всех входах этой ячейки 1 имеется значение 1, то на одном из ее информационных выходов 7 появляется значение О, которое вызывает перепись информации из i-й ячейки 1 в (i+1)-ю.

Поскольку запись в ячейку t единицы и нуля происходит по раздельным каналам, должна блокироваться возможность одновременной записи единицы и нуля в одну ячейку 1. Дпя этого

согласно первому варианту элементы 4 обеих цепочек 2 1 образуют RS-триггер так, что, если RS-триггер из элементов 3 и 4 одной цепочки 2 этой ячейки 1 находится в единичном состоянии, RS-триггер из элементов 3 и А другой ее цепочки 2 не может установиться в единичное состояние.

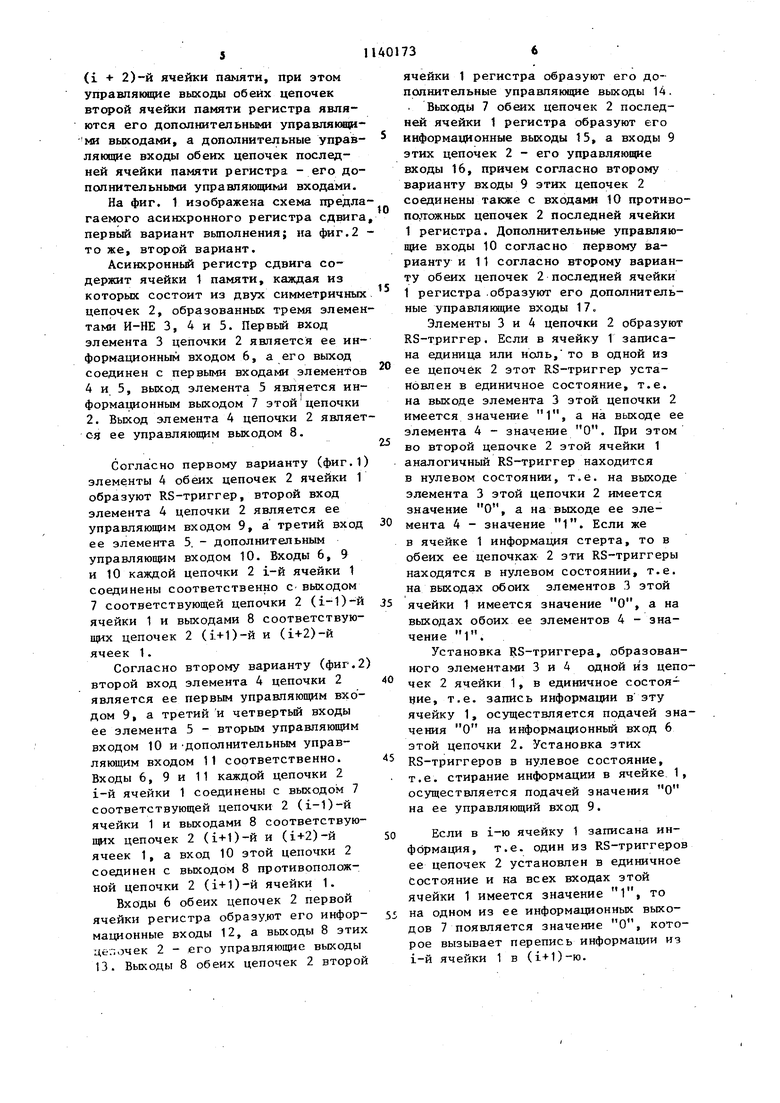

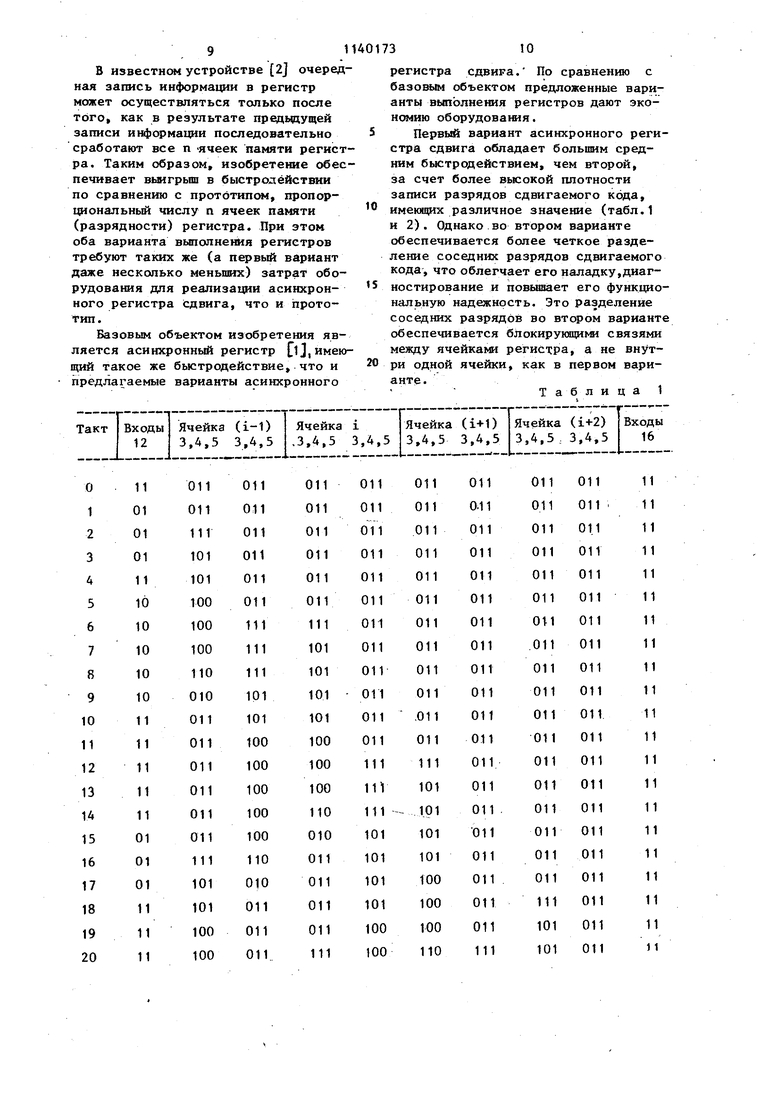

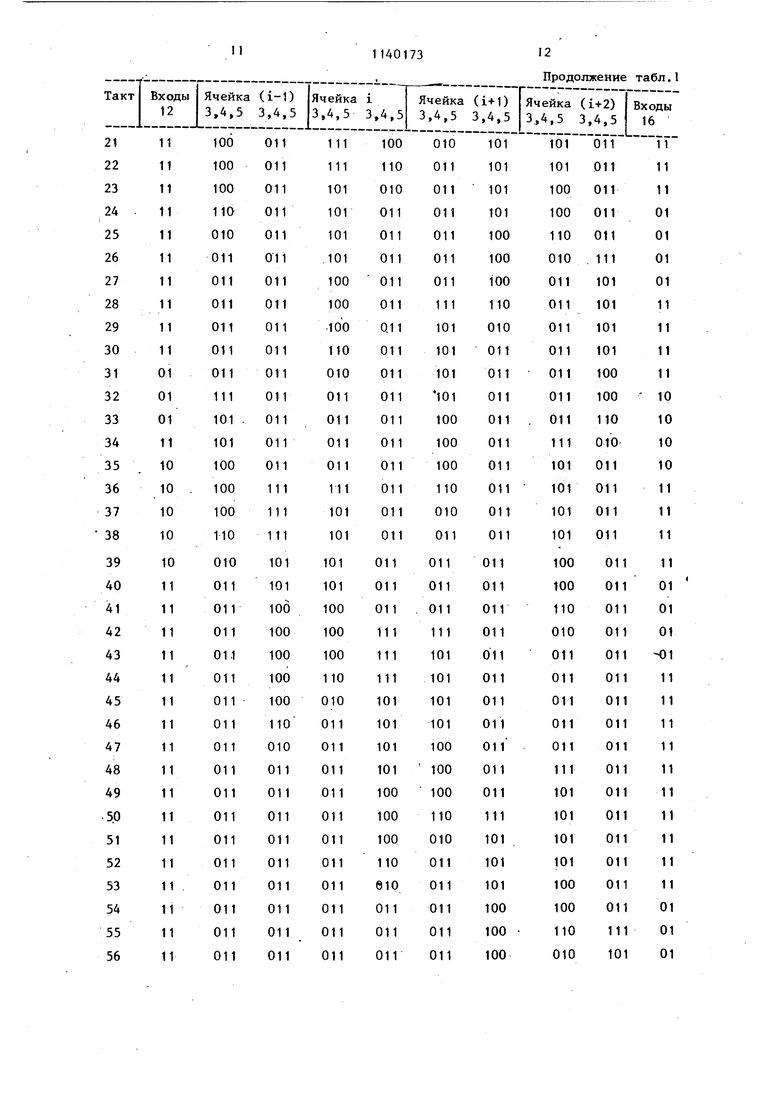

Функционирование асинхронного

perTiCTpa сдвига, выполненного согласно первому варианту, при прохождении через него последовательности 01001 иллюстрируется табл. 1, где в каждой колонке первые пози11 1и относятся к верхним входам и цепочкам 2 регистра (фиг. 1), а вторые - к нижним. В исходном состоянии (такт 0) информация во всех ячейках 1 регистра стерта. Далее указаны состояния, возникакхцие в ячейках 1 под действием изменений значений на входах регистра, в предположении, что задержки всех его элементов равны &.

Значение 11 на информационных входах 12 регистра соответствует отсутствию информации, значения 01 и 10 - нулю и единице соответственно, комбинация 00 запрещена. Значения 01 и 10 на управляющих ,вькодах 13 регистра являются квитанцией о приеме регистром нуля и единищ 1 соответственно. По этой квитанции на входах 12 .регистра может быть установлено значение 11, которое II на управляющих выходах 14 регистра разрешает установку значений 01 или 10 на его входах 12, значение 01 на управляющих выходах 14 регистра разрешает установку только значения 10V на его входах 12, а значение 10 на выходах 14 - только значение 01 на входах 12.

Значение 11 на информационных выходах 15 регистра соответствует отсутствию информации, значения 01 и 10 - нулю и единице соответственно, значение 00 на этих выходах в процессе работы регистра не возникает. Значения 01 и 10 на управляющих входах 16 регистра являются квитанцией о приеме нуля и единицы соответственно с его вы8

ходов 15. По этой квитат ии стирается информация в последней ячейке 1 регистра и на его выходах 15 устанавливается значение 11. На управляющих входах 17, введенных в состав регистра для унификации его входного и выходного интерфейса, зафиксировано- значение 11, разрешающее установку значений 01 и 10 на его выходах 15. Поэтому значения на управляющих выходах 17 регистра в табл. 1 не приведены.

Из табл. 1 видно, что быстродействие регистра, вьтолненного согласно первому варианту, определяемое временем между двумя последовательными записями информации в регистр, не хуже 16 Т: одна запись происходит например, в такте 15, а следующая в такте 31, причем эта характеристика не зависит от числа ячеек регистра.

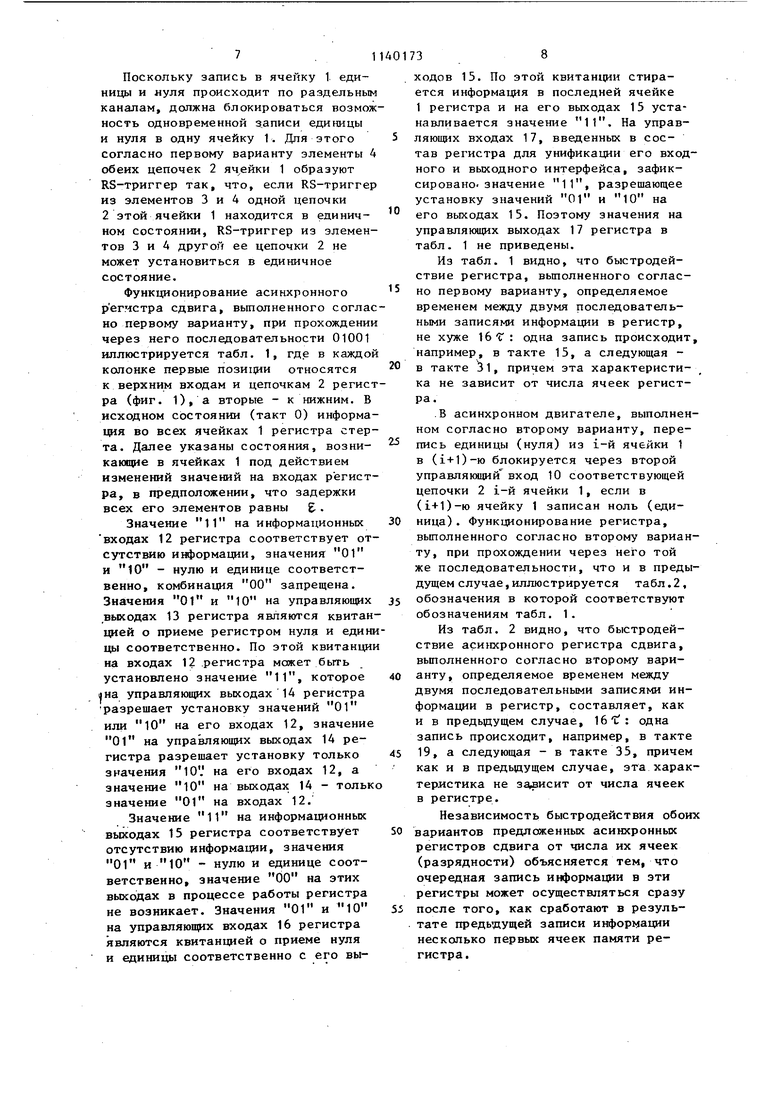

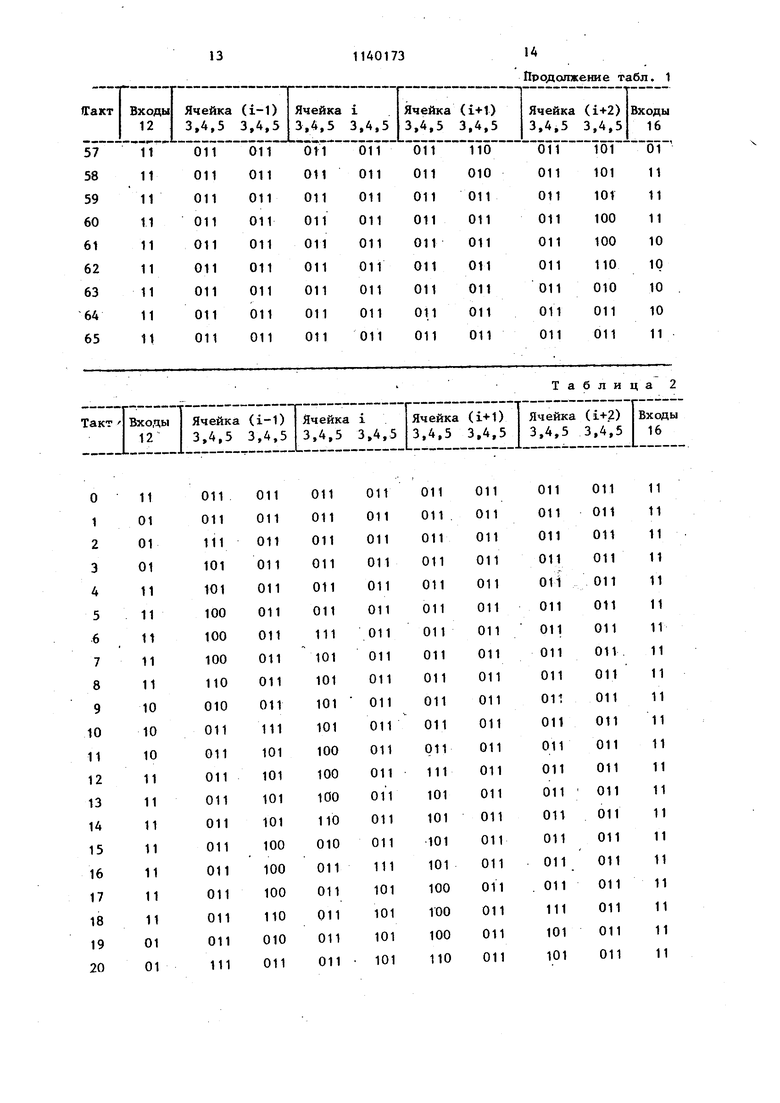

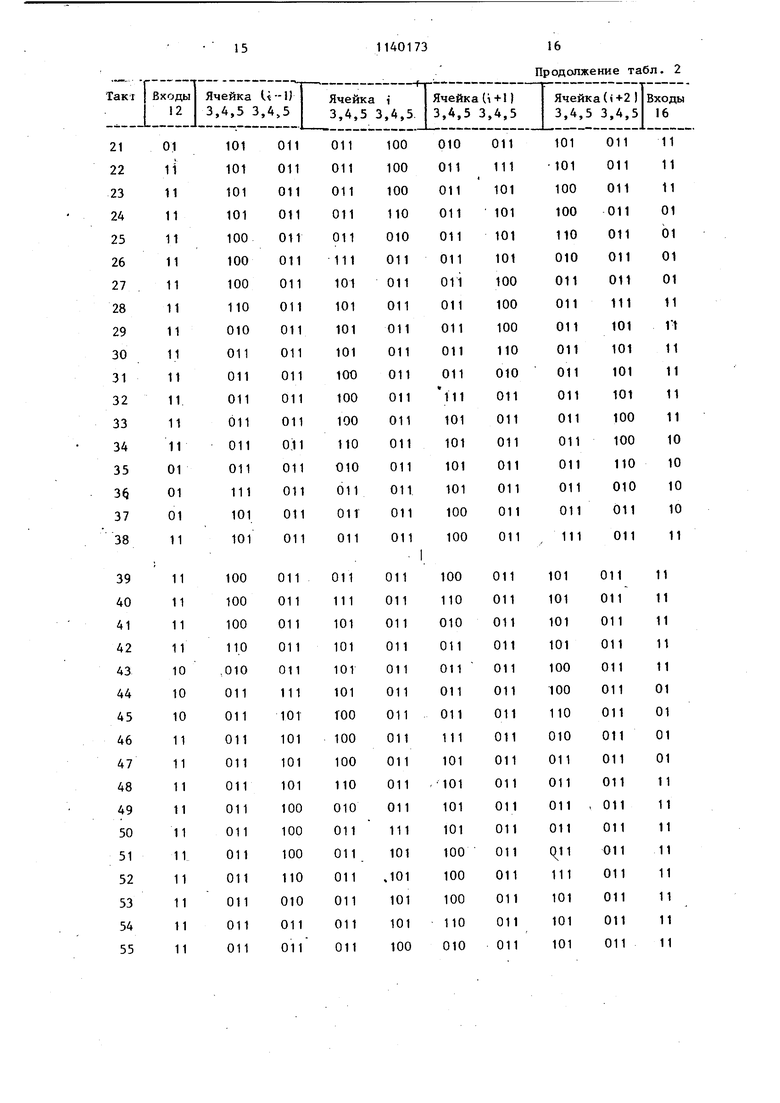

.В асинхронном двигателе, выполненном согласно второму варианту, перепись единицы (нуля) из i-й ячейки 1 в (1+1)-ю блокируется через второй управляющий вход 10 соответствующей цепочки 2 i-й ячейки 1, если в (1+1)-ю ячейку 1 записан ноль (единица) . Функционирование регистра, выполненного согласно второму варианту, при прохождении через него той же последовательности, что и в предыдущем случае, иллюстрируется табл.2, обозначения в которой соответствуют обозначениям табл. 1.

Из табл. 2 видно, что быстродействие асинхронного регистра сдвига, вьтолненного согласно второму варианту, определяемое временем между двумя последовательными записями информации в регистр, составляет, как и в предьщущем случае, 16 L: одна запись происходит, например, в такте 19, а следующая - в такте 35, причем как и в предьрущем случае, эта характеристика не зависит от числа ячеек в регистре.

Независимость быстродействия обои вариантов предложенных асинхронных регистров сдвига от числа их ячеек (разрядности) объясняется тем, что очередная запись информации в эти регистры может осуществляться сразу после того, как сработают в результате предыдущей записи информации несколько первых ячеек памяти регистра. 9 В известном устройстве 2j очеред ная запись информации в регистр может осуществляться только после того, как в результате предьщущей записи информации последовательно сработают все п -ячеек памяти регист ра. Таким образом, изобретение обес печивает выигрыш в быстродействии по сравнению с прототипом, пропор191ональный числу п ячеек памяти (разрядности) регистра. При этом оба варианта выполнения регистров требуют таких же (а первый вариант даже несколько менышпс) затрат оборудования для реализации асинхронного регистра сдвига, что и прототип . Базовым объектом изобретения является асинхронный регистр fij, имею щий такое же бьютродействие, что и предлагаемые варианты асинхронного 3 сдвига. По сравнению с регистра базовьм объектом предложенные варианты выполнения регистров дают экономию оборудовашя. Первь вариант асинхронного регистра сдвига обладает большим средним быстродействием, чем второй, за счет более высокой плотности записи разрядов сдвигаемого кода, имекицих различное значение (табл.1 и 2). Однако во втором варианте обеспечивается более четкое разделение соседних разрядов сдвигаемого кода, что облегчает его наладку,диагностирование и повышает его функциональную надежность. Это разделение соседних разрядов во втором варианте обеспечивается блокирукяцим связями между ячейками регистра, а не внутри одной ячейки, как в первом варианте. Таблица1

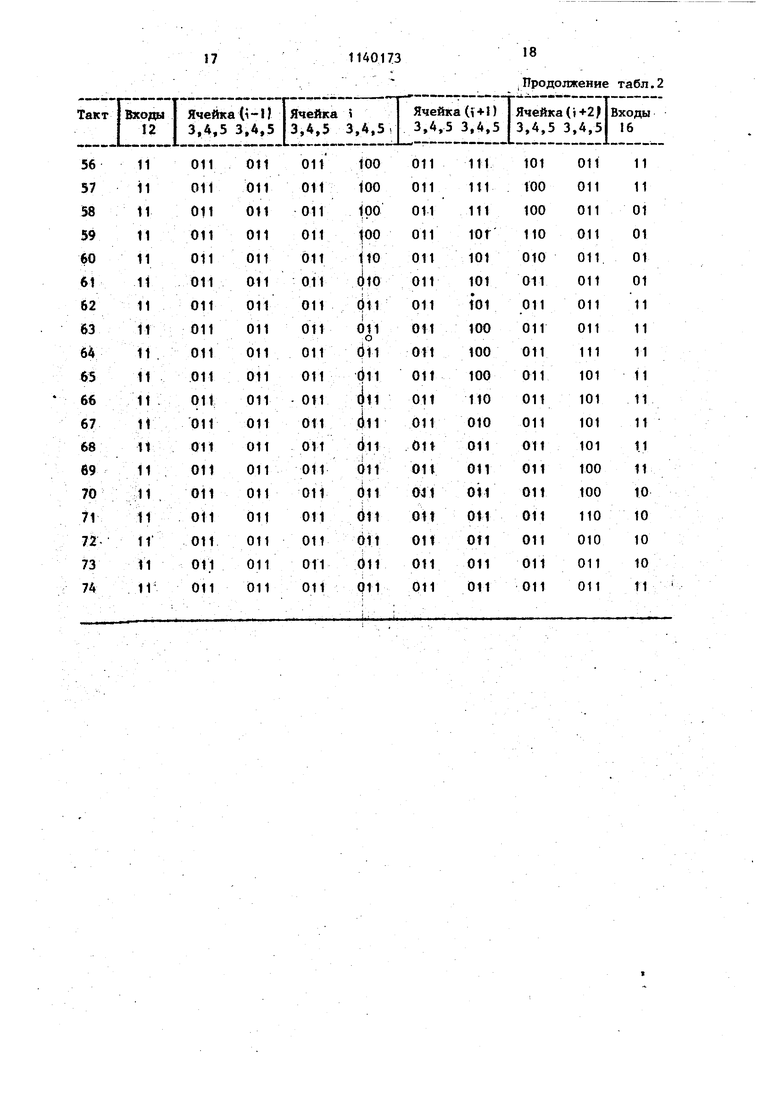

,Продолжение табл.2 Гз (Г 4 17

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Асинхронный регистр сдвига | 1978 |

|

SU728161A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Регистр сдвига | 1979 |

|

SU799009A2 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-02-15—Публикация

1982-04-30—Подача