Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения асинхронных устройств приема и передачи информащш.

Цель изобретения - упрощение регистра.

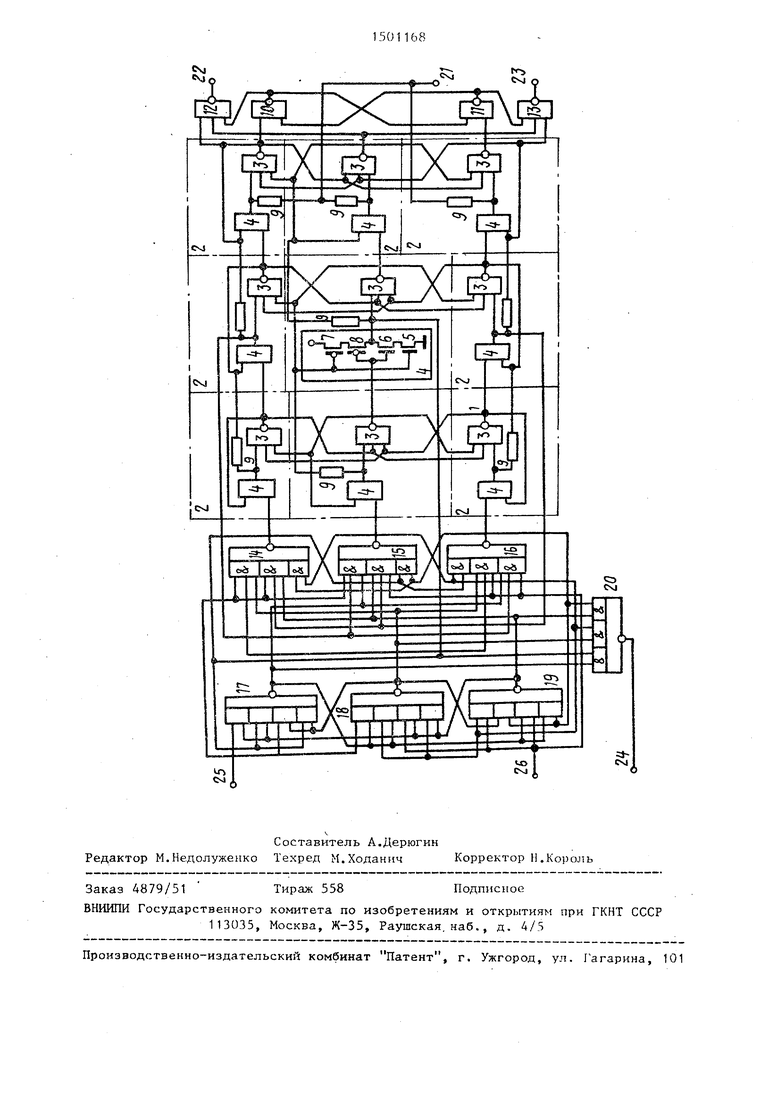

На чертеже представлена схема регистра.

Регистр выполнен на КЬЩП-тран- зисторах и содержит ячейки 1 памяти, каждая из которых состоит из трех симметричных цепочек 2, в состав каждой из которых входят элемент И-НЕ 3, логический элемент 4, состоящий из первого и второго транзисторов п-типа 5, 6 и первого и второго транзисторов р-типа 7, 8)и элемент 9 связи, выполненный на резисторе,группу из четырех элементов И-НЕ 10-13 и семь элементов И-ИПИ-НЕ 14-20. На

чертеже показаны также управляющий вход 21 записи, прямой 22 и инверс- нь1й 23 информационные выходы, управляющий выход 24 считывания, прямой 25 и инверсный 26 информационные входы регистра.

Значение сопротивления резистора 9 должно быть не менее 3,7г, где г - сопротивление канала открытого КЬЩП- транзистора. Ограничение сверху накладывается требованиями к быстродействию регистра

Асинхронный последовательный регистр работает следующим образом. Наборы значений на входах 25 и 26 регистра соответствуют: 00 - информация на входах отсутствует, 01 - передача единицы, 10 - передача нуля, набор 11 - запрещен. Наборы значений на выходах 22, 23 регистра со- .ответствуют: 11 - отсутствие инфорел

ot

00

MaiuiH, 01 - передача нуля, 10 - пердача единицы, набор 00 в процессе работы регистра не возникает. Состояния ячейки 1 памяти (значения на выходах элементов 3 ее цепочек 2) соответствуют: 110 - в ячейке записан ноль, 011 - в ячейке записана единица, 101 - значение разряда кода, записанного в ячейку, совпадает со значением предыдущего разряда, т.е. в ячейку записана метка, и. 111 - информация в ячейке стерта. Другие состояния ячейки 1 памяти в процессе работы регистра не возникают из-за перекрестных связ.ей межд элементами 3 ее цепочек 2.

Приведенное кодирование состояний ячейки 1 памяти означает, что первые и третьи цепочки 2 ячеек 1 памяти регистра образуют каналы, за которыми закреплены соответственно единичное и нулевое значение разрядов сдвигаемого кода, а вторые цепочки 2 этих ячеек 1 памяти - канал для передачи меток. Таким образом, если соседние разряды сдвигаемого кода имеют различное значение, то соответственно продвигаются по первому и третьему каналам, если же одинаковое значение то по первому (третьему) и второму каналам. Этим обеспечивается продвижение соседних разрядов сдвигаемого кода вплотную .друг за другом, тогда как в каждом из каналов между соседними порциями информации образуется интервал не менее, чём в одну ячейку памяти. Если на выходе элемента 3 цепочки 2 i-й ячейки памяти 1 имеется 1, в элементе 4 этой цепочки 2 транзистор 5 открыт, а транзистор 7 закрыт и, если при этом на второй вхо этого элемента 4 поступает значение О, с выхода элемента 3 соответствующей цепочки 2 (1г1)-й ячейки 1 памяти, то закрыт и его транзистор и потенциал на первом входе элемента 3 этой цепочки 2 определяется значением на выходе элемента 3 соответствующей це.почки 2 (1+1)-й ячейки 1 памяти, т.е.,если 1 переписалась из цепочки 2 i-й ячейки 1 памяти в цепочку 2 (1+1)-й ячейки 1 памяти, то в цепочку 2 i-й ячейки 1 памяти может быть записан О. Аналогично, если О переписан из цепочки 2 i-й ячейки 1 памяти в цепочку 2 (i+1)-й ячейки 1 па

0

5

0

5

0

5

0

5

мяти, то в цепочку 2 i-й ячейки 1 памяти может быть записана 1.

Распределение информации по каналам обеспечивают два трехстабиль- ных триггера, образованные элементами 17, 18, 19 и 14, 15, 16, состояния которых соответствуют: 100 и 011 - единица, 001 и 110 - ноль, 010 и 101 - метка. При наборе 00 на входах 25, 26 регистра запись в триггер на элементах 14, 15, 16 блокируется, а в триггер на элементах 17, 18, 19 переписывается информация из триггера на элементах 14, 15., 16, после чего на выходе элемента 20, т.е. на управляющем выходе записи 24 регистра устанавливается значение 1. После этого на входах 25, 26 может установиться информационный набор, соответствующий единице или нулю. При этом, если на входах 25 и 26 устанавливается единичньш набор, а в триггере из элементов 17, .18, 19 записан нуль или метка, то в триггер из элементов 14, 15, 16 записывается единица, если же в триггере из элементов 17, 18, 19 записана еди- ница, то в триггер из элементов 14, 15, 16 записьшается метка. При нулевом наборе на входах 25, 26 в триггер из элементов 14, 15, 16 записывается нуль, если в триггере из элементов 17 18, 19 записана единица или метка и в триггер из элементов 14, 15, 16 записывается метка, если в триггере из элементов 17, 18, 19 записан нуль. Необходимым условием записи информации в триггер из элементов 14, 15, 16 является перепись ранее хранимой в нем информации в первую ячейку 1 памяти, а именно совпадение значений на выходах элементов 4 цепочек 2 второй ячейки 1 памяти и элементов 17, 18, 19. По завершении записи информации в триг- тер из элементов 14, 15, 16. на выходе элемента 20,т.е. управляющем выходе . записи 24 регистра, устанавливается значение О, после чего информация с входов 25, 26 регистра может быть снята и т.д.

Для преобразования информации, записанной в ячейки 1 памяти регистра, в парафазную служат дополнительные элементы 12, 13 и 10,11, Два последних образуют RS-триггер, который устанавливается в единичное или

5

нулевое состояние при появлении значения О на выходе элемента 3 первой или третьей цепочек 2 последней ячейки 1 памяти. Значение О на выходе элемента 3 одной из трех цепочек 2 последней ячейки 1 памяти может появиться при наличии значения 1 на управляющем входе 21 регистра. При этом, если значения О по- являются на выходах элементов 3 первой Ш1И третьей цепочек 2 последней ячейки 1 памяти, то на выходах элементов 12, 13, т.е. выходах 22, 23

регистра, появляется набор 11 в

соответствии с состоянием RS-тригге- ра из элементов 10, 11, если же значение О появляется на выходе элемента 3 второй цепочки 2 последней ячейки 1 памяти, то этот набор на вы ходах 22, 23 регистра появляется независимо от состояния этого КЗ-триггера. После появления набора 11 на выходах 22, 23 регистра на его управляющем входе 21 считывания мо- жет быть установлено значение О, которое вызывает стирание информации в последней ячейке памяти 1, в результате чего на выходах элементов 12, 13, т.е. информационных выходах 22, 23 регистра появляется единичный или нулевой наборы в соответствии с состоянием RS-триггера из элементов 10, 11, после появления которого на управляющем входе 21 считывания регистра может быть .установле- но значение 1 и т.д.

В,исходном состоянии все ячейки 1 памяти регистра должны находиться в одинаковых состояниях, для приведе- ния регистра в исходное состояние необходимо, зафиксировав на информационных входах 25, 26 регистра набор 00, повторить некоторое число раз считьшание из него информации путем изменения значений на управляющем входе 21 считывания регистра.

Из описания работы регистра следует,, что в данном регистре к сдвигаемому коду добавляется один раз- ряд из предьщущей последовательности а последний разряд данной последовательности остается в регистре. Тако регистр может быть использован для согласования работы устройств, связанных асинхронным последовательным интерфейсом, предполагающим наличие в каждой передаваемой информационной последовательности, например

ю

5

5

20 5 о

Q с

Q

5

1686

байте, стартового и стопоЬого (одного или двух) битов. Так, например, работает интерфейс на основе микросхемы КР580ВВ51.

Сложность ячейки 1 памяти предлагаемого регистра составляет 33 КМДП транзистора (включая резисторы 9), а известного - 54.

Формула изобретения

Асинхронный последовательный регистр на КМДП-транзисторах, содержащий ячейки памяти, каждая из которых состоит из трех элементов И-НЕ и трех логических элементов, причем каждый логический элемент состоит из двух пар транзисторов п- и р-типов, причем истоки первых транзисторов п- и р-типов соединены с шиной нулевого потенциала и с шиной питания регистра соответственно, их затворы - с выходом соответствующего элемента И-НЕ данной ячейки памяти, первьй вход которого соединен со стоками вторых транзисторов п- и р-типов соответствующего логического элемента, исток второго транзистора п-типа соединен со стоком первого транзистора п-типа, второй и третий входы каждого элемента И-НЕ соединены с выходами других элементов И-НЕ данной ячейки памяти, и группу элементов И-НЕ,причем выход первого элемента И-НЕ группы соединен с первыми входами второго и третьего , а выход второго - с первыми входами первого и четвертого элементов И-НЕ группы, выходы третьего и, четвертого элементов И-НЕ группы являются прямым и инверсным информационными выходами регистра соответственно, отличающий- с я тем, что, с целью упрощения регистра,он содержит семь элементов И-ИЛИ-НЕ и в каждой ячейке памяти три элемента связи, выполненные на резисторах, причем первый вход элемента И-НЕ каждой ячейки памяти, кроме последней, соединен через резистор с выходом соответствующего элемента И-НЕ последутацей ячейки памяти, а выход элемента И-НЕ - с затворами вторьк транзисторов п- и р-типов соответствующего логичес кого элемента последующей ячейки памяти, первые входы элементов И-НЕ последней ячейки памяти соединены с первыми выводами соответствующих

резисторов, вторые выводы которых являются управляющим входом считывания регистра, выходы первого и третьего элементов И-НЕ последней ячейки памяти соединены с вторыми входами первого и третьего и второ - го и четвертого элементов И-НЕ группы соответственно, а выход второго элемента И-НЕ последней ячейки па- мяти - с третьими входами третьего и четвертого элементов И-НЕ группы, причем в каждом логическом элементе каждой ячейки памяти сток первого транзистора р-типа соединен с ис- током второго транзистора р-типа, вы ходы первого, второго и третьего элементов И-ИЛИ-НЕ соединены соответственно с затворами вторых транзисторов п- и р-типов соответст- вуюших логических элементов первой ячейки памяти, первыми входами первых групп И второго, третьего и первого элементов И-ИЛИ-НЕ, первыми входами первых и вторых групп И чет- вертого, пятого к шестого элементов И-ИЛИ-НЕ и первыми входами первой, второй и третьей групп И седьмого элемента И-ИЛИ-НЕ, выходы четвертого, пятого и шестого элементов И-ИЛИ НЕ соединелы с вторыми входами первых и третьих групп И пятого, шестого и четвертого элементов И-ИЛЙ-НЕ, вторыми входами вторых и четвертых

: групп И шестого, четвертого и пятого .элементов И-ИЛИ-НЕ, первыми входами вторых групп И второго, третьего и первого элементов И-ИЛИ-НВ и с вторыми входами первой, второй и третьей группы И седьмого элемента И-ИЛИ- НЕ, выход которого является управляющим выходом записи регистра, первые входы третьей и четвертой групп И четвертого элемента И-ИЛИ-НЕ, пер- вьш вход третьей группы И пятого элемента И-ИЛИ-НЕ, вторые входы второй и третьей групп И первого элемента И-ИЛИ-НЕ и второй вход второй группы И второго элемента И-ИЛИ- НЕ являются прямым информационным входом регистра, а первые входы третьей и четвертой групп И шестого элемента И-ИЛИ-НЕ, первый вход четвертой группы И пятого элемента И-ИЛИ-НЕ, вторые входы второй и третьей групп И третьего элемента И-ИЛИ НЕ и второй вход третьей группы И второго элемента И-ИЛИ-НЕ являются инверсным информационным входом регистра, первые входы первого, второго и третьего элементов И-НЕ второй ячейки памяти соединены соответственно с третьими входами вторых . групп И второго,, третьего и первого элементов И-ИЛИ-НЕ и третьих групп И третьего, первого и второг о элементов И-ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1410103A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для реализации подстановок | 1990 |

|

SU1805478A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения асинхронных устройств приема и передачи информации, каждая последовательность которой сопровождается стартовым и стоповым (одним или двумя) битами. Целью изобретения является упрощение регистра. Для этого в каждую ячейку памяти, состоящую из элемента И-НЕ и логического элемента, введен элемент связи, выполненный на резисторе. Для согласования регистра с источником информации он содержит семь элементов И-ИЛИ-НЕ, образующих два трехстабильных триггера. 1 ил.

| Ячейка памяти для буферного регистра | 1976 |

|

SU661606A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-08-15—Публикация

1987-07-01—Подача