«125

Изобретение относится к автоматие и вычислительной технике.

Цель изобретения - упрощение асинхонного регистра сдвига.

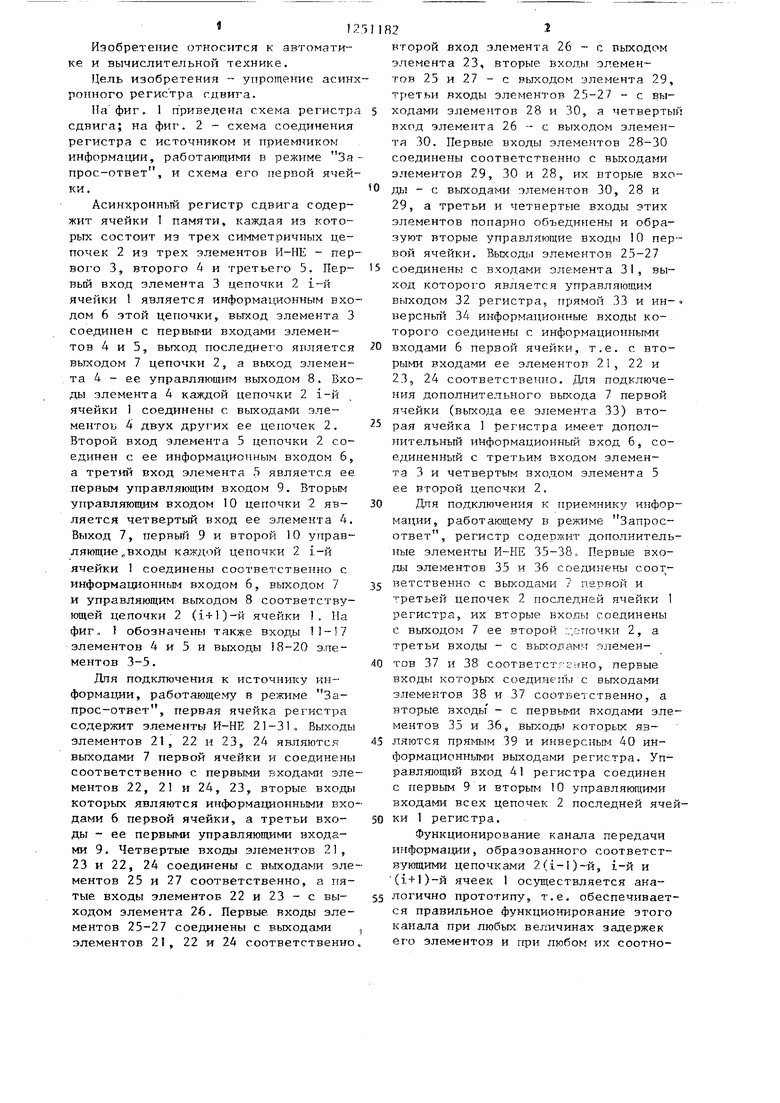

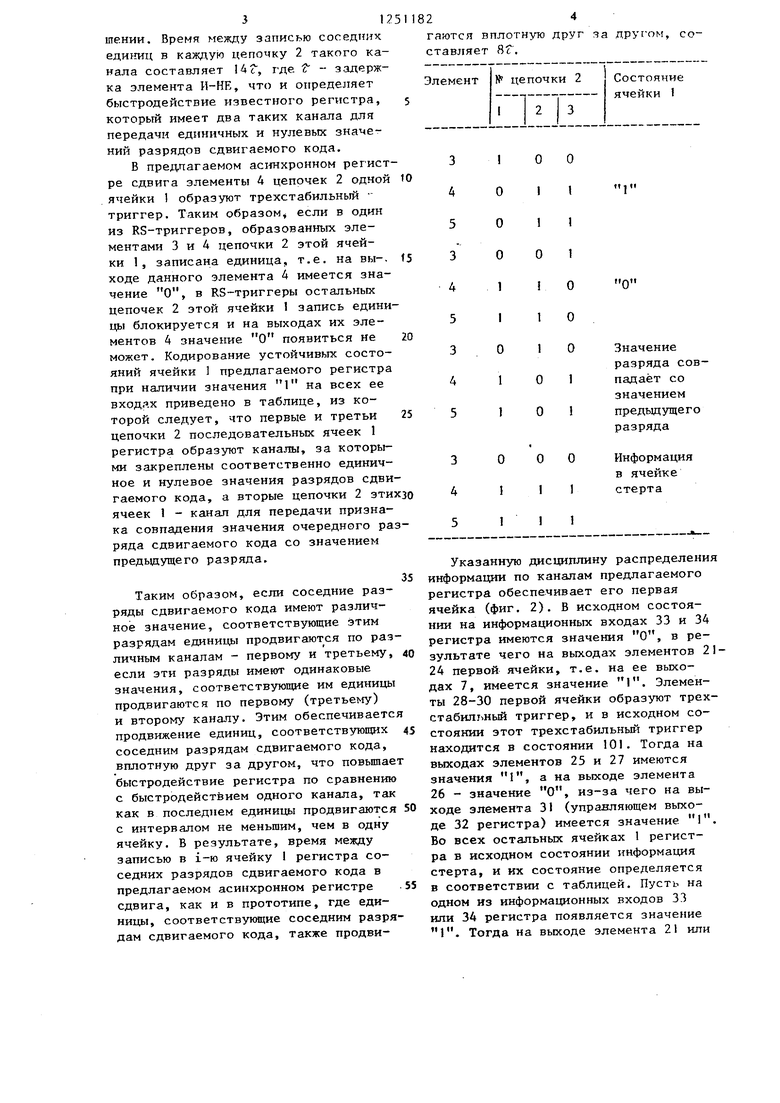

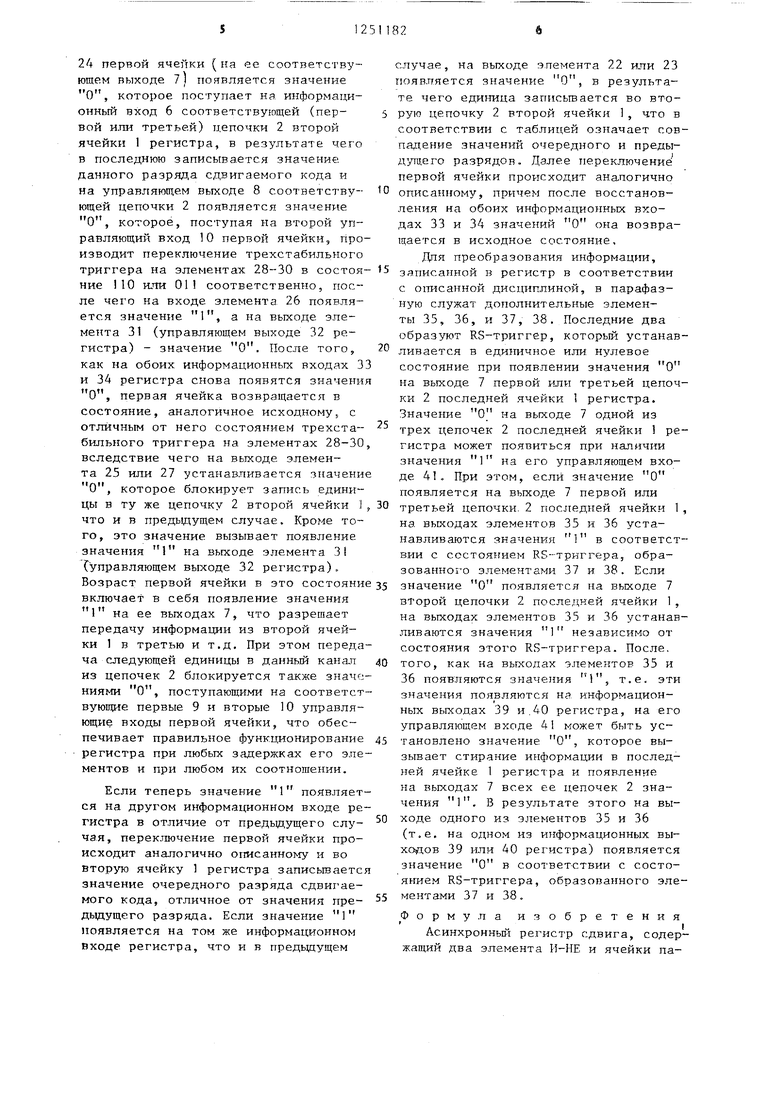

На фиг. 1 приведена схема регистра двига; на фиг. 2 - схема соединения егистра с источником и нриемником нформагц и, работающими в режиме Зарос-ответ, и схема его первой ячейи.

Асинхронный регистр сдвига содерит ячейки I памяти, каждая из которых состоит из трех симметричных цепочек 2 из трех элементов И-НЕ - первого 3, второго 4 и третьего 5. Первый вход элемента 3 цепочки 2 i-й ячейки 1 является информац:ионным входом 6 этой цепочки, выход элемента 3 соединен с первыми входами элементов 4 и 5, выход последнего является выходом 7 цепочки 2, а выход элемен- та 4 - ее управляющим выходом 8. Входы элемента 4 каждой цепочки 2 i-й ячейки 1 соединены с выходами элементов 4 двух других ее цепочек 2. Второй вход элемента 5 цепочки 2 соединен с ее информационным входом 6 а третий вход элемента 5 является ее первым управляющ ш входом 9. Вторым управляющим входом 10 цепочки 2. является четвертый вход ее элемента 4. Выход 7, первь й 9 и второй 10 управляющие „входы каждой цепочки 2 i-й ячейки соединены соответственно с информационным входом 6, выходом 7 и управляющим выходом 8 соответствующей цепочки 2 (ifl)-й ячейки 1. На фиг. J обозначены также входы 11-Г/ элементов 4 и 5 и выходы 8-20 элементов 3-5.

Для подключения к источнику информации, работающему в режиме Запрос-ответ, первая ячейка регистра содержит элементы И-НЕ 21-3 К Выходы элементов 21, 22 и 23, 24 якпяются выходами 7 первой ячейки и соединены соответственно с первыми входам элементов 22, 21 и 24, 23, вторые входы которых являются информатдионными входами 6 первой ячейки, а третьи входы ее первыми управляющими входами 9, Четвертые входы элементов 21, 23 и 22, 24 соединены с выходами элементов 25 и 27 соответственно, а пятые входы элементов 22 и 23 - с выходом элемента 26. Первые входы элементов 25-27 соединены с выходами , элементов 21, 22 и 24 соответственно.

2

второй вход элемента 26 - с выходом элемента 23, вторые входы элементов 25 и 27 - с рыходом элемента 29, третьи входы элементов 25-27 - с выходами элементов 28 и 30, а четвертый вход элемента 26 -- с выходом элемента 30. Первые входы элементов 28-30 соединены соответственно с выходами элементов 29, 30 и 28, их вторые вхо;(ь - с выходами элементов 30, 28 и 29, а третьи и четвертые входы этих элементов попарно объединены и образуют вторые управляющие входы 10 первой ячейки. Выходы элементов 25-27

соединены с входами элемента 31, выход которого является управляющим выходом 32 регистра, прямой 33 и ин- версный 34 информационные входы которого соединены с информационными

входами 6 первой ячейки, т.е. с вторыми входами ее элементов 21, 22 и 23, 24 соответственно. Для подключения дополнительного выхода 7 первой ячейки (выхода ее элемента 33) вторая ячейка 1 регистра имеет допол- нительньй информационный вход 6, соединенный с третьим Входом элемента 3 и четвертым входом элемента 5 ее второй цепочки 2.

Для подключения к приемнику информации, работающему в режиме Запрос- ответ, регистр содержит дополнительные элементы И-НЕ 35-38.. Первые входы элементов 35 и 36 соединены соот ветственно с выходами 7 первой и

третьей цепочек 2 последней ячейки 1 регистра, их вторые входь соединены с выходом 7 ее второй г.епочки 2, а третьи входы - с выходамм элементов 37 и 38 соответстя:гуно, первые входы которых соединеиь с выходами элементов 38 и 37 соответственно, а вторые входы - с первьпун входами элементов 35 и 36, выходы которых язляются прямым 39 и инверсным 40 информационными выходами регистра. Управляющий вход 41 регистра соединен с первым 9 и вторым 10 управляющими входами всех цепочек 2 последней ячейки 1 регистра.

Функционирование канала передачи информац ти, образованного соответствующими цепочками 2(1-1)-и, 1-й и (1+1)й ячеек 1 осуществляется аналогично прототипу, т.е. обеспечивается правильное функционирование этого канала при любых величинах задержек его элементов и при любом их соотно31

ше.нии. Время между записью соседних едигшц в каждую цепочку 2 такого канала составляет 14, где t задержка элемента И-НЕ, что и определяет быстродействие известного регистра, который имеет два таких канала для передачи единичных и нулевых знамений разрядов сдвигаемого кода.

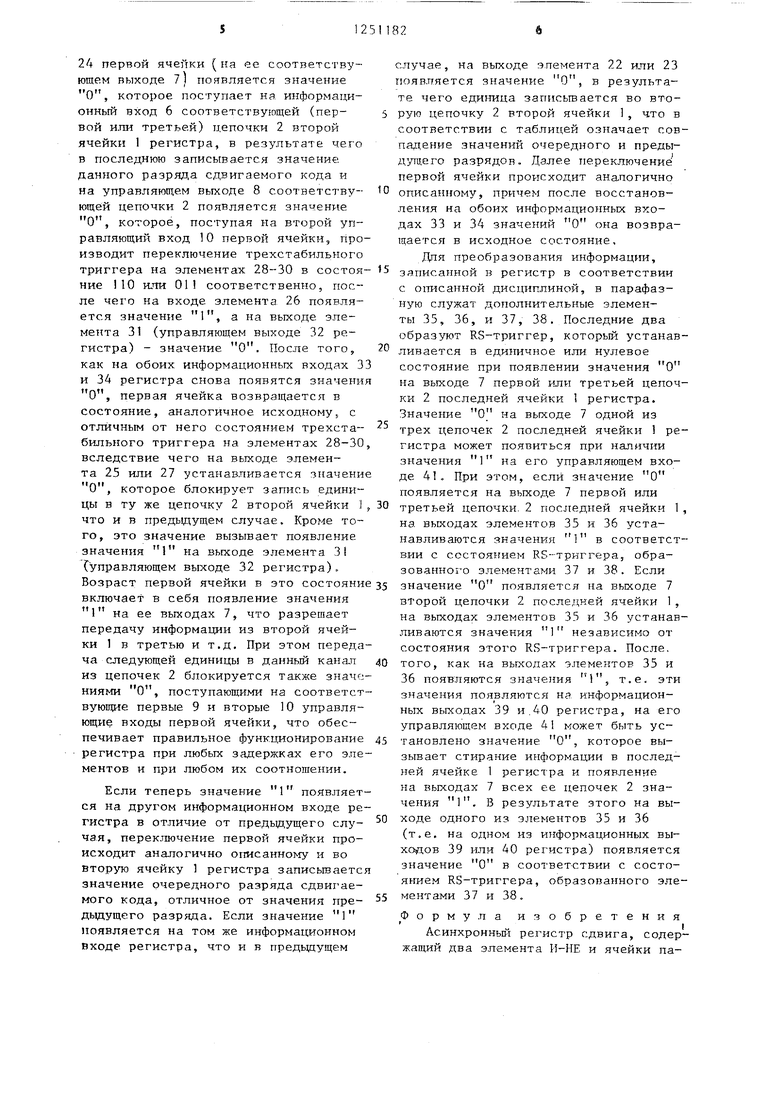

В предпагаемом асинхронном регистре сдвига элементы А цепочек 2 одной ячейки 1 образуют трехстабильный триггер. Таким образом если в один из RS-триггеров, образованных элементами 3 и 4 цепочки 2 этой ячейки 1, записана единица, т.е. на вы-, ходе данного элемента 4 имеется значение О, в КЗ-триггеры остальных цепочек 2 этой ячейки 1 запись единицы блокируется и на выходах их элементов 4 значение О появиться не может. Кодирование устойчивых состояний ячейки 1 предлагаемого регистра при наличии значения 1 на всех ее входлх приведено в таблице, из которой следует, что первые и третьи цепочки 2 последовательных ячеек 1 регистра образуют каналы, за которыми закреплены соответственно единичное и нулевое значения разрядов сдвигаемого кода, а вторые цепочки 2 зти ячеек 1 - канал для передачи признака совпадения значения очередного раряда сдвигаемого кода со значением предыдущего разряда.

Таким образом, если соседние разряды сдвигаемого кода имеют различное значение, соответствующие этим разрядам единицы продвигают ся по различным каналам - первому и третьему, если эти разряды имеют одинаковые значения, соответствующие им единицы продвигаются по первому (третьему) и второму каналу. Этим обеспечиваетс продвижение единиц, соответствующих соседним разрядам сдвигаемого кода, вплотную друг за другом, что повышае быстродействие регистра по сравнению с быстродействием одного канала, так как в последнем единицы продвигаются с интервалом не меньшим, чем в одну ячейку. В результате, время между записью в i-ю ячейку 1 регистра соседних разрядов сдвигаемого кода в предлагаемом асинхронном регистре сдвига, как и в прототипе, где единицы, соответствуницие соседним разрядам сдвигаемого кода, также продви182

гаются вплотную друг за другом, составляет 8Г.

Указанную дисциплину распределени информации по каналам предлагаемого регистра обеспечивает его первая ячейка (фиг. 2). В исходном состоянии на информационных входах 33 и 34 регистра имеются значения О, в результате чего на выходах элементов 2 24 первой ячейки, т.е. на ее выходах 7, имеется значение I. Элементы 28-30 первой ячейки образуют трехстабильный триггер, и в исходном состоянии этот трехстабильный триггер находится в состоянии 101. Тогда на выходах элементов 25 и 27 имеются значения I, а на выходе элемента 26 - значение О, из-за чего на выходе элемента 31 (управляющем выходе 32 регистра) имеется значение 1. Во всех остальных ячейках 1 регистра в исходном состоянии информация стерта, и их состояние определяется в соответствии с таблицей. Пусть на одном из информационных входов 33 или 34 регистра появляется значение 1. Тогда на выходе элемента 21 или

24 первой ячейки ( на ее соответствующем выходе 7) появляется значение О, которое поступает на информационный вход 6 соответствующей (пер- вой И.Т1И третьей) цепочки 2 второй ячейки 1 регистра, в результате чего в последнюю записывается значение . данного разряда сдвигаемого кода и на управляющем выходе 8 с.оответс7 ву- ющей цепочки 2 появляется значение О, которое, поступая на второй управляющий вход 10 первой ячейки, производит переключение трехстабильного триггера на элементах 28-30 в состоя- ние ПО или 011 соответственно, после чего на входе элемента 26 появляется значение 1, а на выходе элемента 31 (управляющем выходе 32 регистра) - значение О. После того, как на обоих информационных входах 33 и 34 регистра снова появятся значения О, первая ячейка возвращается в состояние, аналогичное исходному, с отличным от него состоянием трехста- бильного триггера на элементах 28-30 вследствие чего на выходе элемента 25 или 27 устанавливается значение О, которое блокирует запись единицы в ту же цепочку 2 второй ячейки 1 что и в предыдущем случае. Кроме того, это значение вызывает появление значения 1 на выходе элемента 3 (управляющем выходе 32 регистра),. Возраст первой ячейки в это состояние включает в себя появление значения 1 на ее выходах 7, что разрешает передачу информации из второй ячейки 1 в третью и т.д. При этом передача следующей единицы в данный канал; из цепочек 2 блокируется также значениями О, поступающими на соответствующие первые 9 и вторые 10 з правля- ющие входы первой ячейки, что обеспечивает правильное функционирование регистра при любых задержках его элементов и при любом их соотношении.

Если теперь значение 1 появляется на другом информационном входе регистра в отличие от предьщущего слу- чая, перек-лючение первой ячейки происходит аналогично описанному и во вторую ячейку 1 регистра записьшается значение очередного разряда сдвигаемого кода, отличное от значения пре- дьщущего разряда. Если значение 1 появляется на том же информационном входе регистра, что и в предьщущем

случае, на выходе элемента 22 или 23 появляется значение О, в результате чего единица записьюается во вторую цепочку 2 второй ячейки 1, что в соответствии с таблицей означает совпадение значений очередного и предыдущего разрядов. Далее переключение первой ячейки происходит анапогично описанному, причем после восстановления на обоих информационных входах 33 и 34 значений О она возвращается в исходное состояние.

Для преобразования информации, записанной в регистр в соответствии с описанной дисциплиной, в парафаз- ную служат дополнительные элементы 35, 36, и 37, 38. Последние два образуют RS-триггер, который устанавливается в единичное или нулевое состояние при появлении значения О на выходе 7 первой или третьей цепочки 2 последней ячейки 1 регистра. Значение О на выходе 7 одной из трех цепочек 2 последней ячейки 1 регистра может появиться при наличии значения 1 на его управляющем входе 41, При этом, если значение О появляется на выходе 7 первой или третьей цепочки. 2 последней ячейки 1 на. выходах элементов 35 и 36 устанавливаются значения 1 в соответствии с состоя1-гием RS-триггера, образованного элементами 37 и 38. Если значение О появляется на выходе 7 второй цепочки 2 послеп,ней ячейки 1 , на выходах элементов 35 и 36 устанавливаются значения 1 независимо от состояния этого RS-триггера. После, того, как на вькодах элементов 35 и 36 ПОЯВ.ЛЯЮТСЯ значения М, т.е. эти значения появляются на информационных выходах 39 и.40 регистра, на его управляющем входе 41 может быть установлено значение О, которое вызывает стирание информации в последней ячейке 1 регистра и появление на выходах 7 всех ее цепочек 2 значения 1. В результате зтого на выходе одного из элементов 35 и 36 (т.е. на одном из информационных выходов 39 или 40 регистра) появляется значение О в соответствии с состоянием RS-триггера, образованного элементами 37 и 38.

Формула изобретения

Асинхронный регистр сдвига, содержащий два элемента И-НЕ и ячейки ла 1

мяти, каждая из которьгх, кроме псф вой, состоит из трех симметричных цепочек из трех элементов И-НЕ, причем в каждой цепочке выход первого элемента И-НЕ соединен с первыми входа- ми второго и третьего элементов И-НЕ второй вход третьего элемента И-НЕ соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ, второй и третий входы которот-о соединены соответственно с выходами вторых элементов И-НЕ других цепочек данной ячейки, при этом первьй вход первого элемента И-НЕ и выходы второ го и третьего элементов И-НЕ каждой цепочки каждой ячейки, кроме второй, соединены соответственно с выходом третьего элемента И-НЕ и с четвертым входом второго и третьим входом тре- тьего элементов И-НЕ соответствующей цепочки предыдущей ячейки, а первая ячейка состоит из одиннадцати элементов И-НЕ, причем в данной ячейке выходы первого и второго и третьего и четвертого элементов И-НЕ соединены соответственно с первыми входами второго и первого и четвертого и третьего элементов И-НЕ, вторые входы которых являются соответственно прямым и инверсным информационными входами регистра сдвига, выходы и третьи входы первого, второго и четвертого элементов И-НЕ соединены соответственно с первыми входами и выходами пятого, шестого и седьмого элементов И-НЕ, вторые входы пятого и седьмого элементов И-НЕ соединены соответственно с выходами восьмого и десятого элементов И-НЕ, первые входы восьмого и девятого элементов И-НЕ соединены соответственно с выходами девятого и восьмого элементов И-НЕ, первый и второй входы одиннадцатого элемента И-НЕ соединены с выходами пятого и шестого элементов И-НЕ, а выход является управляющим выходом регистра сдвига, выходы и четвертые входы первого, второго и четвертого элементов И-НЕ первой ячейки соединены соответственно с первыми входами.первых Элементов И-НЕ и выходами третьих элементов И-НЕ первой, второй и третьей цепочек второй ячейки, выходы вторых элементов И-НЕ первой и третьей uenoчек которой соединены соотве.тствевво

1828

с вторым входом восьмого гт первым входом десятого элементов И-НЕ перво ячейки, причем выходы первого и второго элементов Pi-HE являются соответственно прямым и инверсным выxoдa OI регистра сдвига, первые входы соединены соответственно с выходами третьих элементов И-НЕ первой и третьей цепочек последней ячейки, а второй вход первого элемента И-НЕ соединен с выходом третьего элемента И-НЕ второй цепочки последней ячейки, о т - л и ч а ю щ и и с я тем, что, с целью -упроще ния регистра сдвига, он содержит третий и четвертьш элементы И-НЕ, первые входы которых соединены с выходами четвертого и третьего элементов И-НЕ соответственно, а вторые входы - с первыми входами первого и второго элементов И-НЕ соответственно, второй вход второго элемента И-НЕ соединен с вторым входом первого элемента И-НЕ, а третьи входы первого и второго элементов - с выходами третьего и четвертого элементов И-НЕ соответственно, причем в первой ячейке третий вход третьего элемента И-НЕ соединен с выходом шестого элемента И-НЕ, второй, третий и четвертьп входы которого соединены соответственно с выходами третьего, восьмого и десятого элементов И-НЕ, выход седьмого элемента И-НЕ соединен с третьим входом одиннадцатого элемента И-НЕ, четвертый вход третьего элемента И-НЕ соединен с четвертым входом второго элемента И-НЕ, а пятые входы данных элементов соединены соответственно с выходами пятого и седьмого элементов И-НЕ третьи входы которых соединены с выходами девятого элемента И-НЕ, второй вход и выход которого соединены соответственно с выходом и вторым входом десятого элемента И-НЕ, а третий и четвертьй входы - с вторыми входами восьмого и десятого элементов И-НЕ, третьи входы которых соединены с выходами десятого и восьмого элементов И-НЕ соответственно, а четвертые входы - с выходом второго элемента И-НЕ второй цепочки второй ячейки, третий вход первого элемента И-НЕ и четвертый вход третьего элемента И-НЕ которой соединен с выхо-: дом третьего элемента И-НЕпервой ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1462422A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Шифратор | 1985 |

|

SU1298802A2 |

| Ячейка памяти для буферногоРЕгиСТРА | 1979 |

|

SU799010A2 |

| Асинхронный последовательный регистр | 1986 |

|

SU1383444A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1119082A1 |

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является упрощение регистра сдвига. Регистр содержит ячейки памяти, каждая из которых в отличие от прототипа состоит не из четыпех, а из трех сш метричных цепочек. Каждая цепочка состоит из трех элементов И-КЕ. Первая ячейка регистра состоит из 1I элементов И-НЕ и имеет два информационных входа и один управляющий выход для связи с источником. В состав регистра входят элементы И-НЕ для связи с приемником с помощью двух информационных выходов и одного управляющего входа. 2 ил., 1 табл.

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 1196954, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-15—Публикация

1985-02-11—Подача