третьего триггера соединен с выходом Окончание преобразования аналогоцифрового преобразователя, выход схемы сравнения соединен с вторым входом элемента ИЛИ и через второй элемент задержки с единичным входом второго триггера, выходы первого и второго элементов И соединены со счетным входом счетчика адреса, выход второго элемента И через третий элемент задержки соединен с входом Начало преобразования аналого-цифрового преобразователя,при этом каждьм из блоков управления вводом группы содержит регистр начального адреса, регистр конечного адреса, два узла сравнения, счетчик, дешифратор, четьфе элемента И, два триггера, элемент задержки и магистральный усилитель, причем выходы регистров начального и конечного адресов соединены соответственно .с первыми входами первогои второго узлов сравнения, вторые входы которых соединены соответственно с первым и вторым выходами счетчика, выход первого триггера соединен с первым входом первого элемента И, выход которого соединен со счетным входом счетчика и через элемент задержки - с первыми входами второго и третьего элементов И, вторые входы которых соединены соответственно с выходами первого и второго узлов сравнения, выходы второго и третьего элементов И соединены с первыми входами первого и второго триггеров, выход дешифратора соединен с управляющими входами регистров начального и конечного адресов, магистрального усилителя и первым входом четвертого элемента И, выход ко.торого соединен с вторь м входом второго триггера, информационные входы и входы записи регистров начального и конечного адресов соединены с информационной шиной и шиной записи соответствующейцифровой вычислительной машины, шина прерывания которой соединена с выходом первого узла сравнения, а адресная шина и шина чтения цифровой вычислительной машины соединены соответственно с входом дешифратора и вторым входом четвертого элемента И, выход магистрального усилителя соединен с информационной шиной цифровой вычислительной машины, информационные входы магистральных усилителей всех блоков управления вводом соединены с информационным выходом аналого-цифрового преобразователя, выход первого элемента И блока управления обменом соединен со сбросовыми входами первого и второго триггеров и счетчика всех блоков управления вводом группы вторые входы первых элементов И которых соединены с выходом третьего элемента И блока управления обменом, а выходы вторых триггеров - с соответствующими входами пятого элемента и блока управления обменом, еди.ничный вход второго триггера, второй управляющий вход аналоговой вычислительной, машины и входы запуска цифровых вычислительных машин являются входом Пуск устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1986 |

|

SU1348844A1 |

| Устройство для сопряжения аналоговой и цифровой вычислительных машин | 1979 |

|

SU858022A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1985 |

|

SU1317445A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Устройство для сопряжения цифровой и аналоговой вычислительных машин | 1983 |

|

SU1128273A1 |

УСТРОЙСТВО ДЛЯ СВЯЗИ АНАЛОГОВОЙ И ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН, содержащее аналого-цифровой преобразователь, информационный вход которого соединен с информационным выходом аналоговой вычислительной машины, счетчик адреса,, первый и второй выходы которого соединены соответственно с управляющим входом .аналого-цифрового преобразователя и первым входом схемы сравнения, второй вход и выход которой соединены соответственно с выходом регистра числа каналов и сбросовым входом счетчика адреса, а вход регистра числа каналов является входом устройства, дешифратор адреса, группа входов которого соединена с адресной шиной цифровой вычислительной машины, цифроаналоговый преобразователь, выход которого соединен с информационным входом аналоговой вычислительной машины, а информационный и управляющий входы - с информационной и управляющей шинами цифровой вьмислительной машины, отличающееся тем, что, с целью повьшения быстродействия, оно содержит блок управления обменом и группу блоков управления вводом, причем блок управления обменом содержит пять триггеров, пять элементов И, элемент ИЛИ, три элемента задержки и генератор импульсов, при этом выход генератора импульсов соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с выходами первого, второго и третьего триггеров, третьи входы второго и третьего элементов И соединены с выходом четвертого триггера, (Л единичньй вход первого триггера и нулевые входы второго, третьего, четвертого и пятого триггеров соединены с выходом элемента ИЛИ, первый вход которого является входом установки в исходное положение устройства, выход второго элемента И соединен с нулевым входом второго триггера, выход третьего элемента И соединен с нулевым входом третьего триггера и через первый элемент задержки с единичным входом пятого триггера, со сд нулевой вход которого соединен с выходом второго элемента И, выход пятого триггера соединен с первым входом четвертого элемента И, второй вход которого соединен с выходам пятого элемента И, выход четвертого элемента И соединен с единичным входом второго триггера, выход первого элемента И соединен с нулевым входом первого триггера и единичным входом четвертого триггера, единичный вход

Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных гибридных вычислительных устройств и систем.

Известно устройство связи между цифровой вычислительной машиной (ЦВМ) и аналоговой вычислительной машиной (АВМ), состоящее из адресного распределителя, цифроаналоговьпх преобразователей (ЦАП), цифровых потенциометров и регистра управлеш я АВМ, многоканального аналогового запоминающего устройства, многоканального аналогоцифрового преобразователя (МАЦП), контроллера, таймера, регистра пульта 1 .

Недостатком известного устройства являются временные потери, возникающие вследствие периодического запуска элементов устройства и последовательного выполнения операций обмена между аналоговой и цифровой машинами Наиболее близким к предлагаемому является устройство для обмена инфор мацией между цифровой и аналоговой вычислительной машинами, содержащее аналого-цифровой преобразователь, цифроаналоговый преобразователь, счетчики, регистры, схемы сравнения, генератор импульсов, элементы И, ИЛИ, НЕ,блок памяти, дешифратор адреса, счетчик адреса, соединенные соответствующим образом 2j . Однако известное устройство характеризуется недостаточным быстродействием вследствие невозможности совмещения во времени операций аналого-цифрового преобразования с операциями вычислений. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в устройство для связи аналоговой и цифровых вычислительных машин, содержащее аналого-цифровой преобразователь, информационный вход которого соединен с информацион ным выходом аналоговой вычислительной машины, счётчик адреса, первый и второй выходы которого соединены соответственно с управляющим входом аналого-цифрового преобразователя и первым входом схемы сравнения, второй вход к выход которой соединей соответственно с выходом регистра числа каналов и сбросовым входом счетчика адреса, а вход регистра чис ла каналов является входом устройства, дешифратор адреса, группа входов которого соединена с адресной шиной цифровой вычислительной машины, цифроаналого.вый преобразователь, выход которого соединен с информационным входом аналоговой вычислительной машины, а информационный и управляющий входы - с информационной и управляющей шинами цифровой вычислительной машины, введены блок управления обменом и группа блоков управления вво дом, причем блок управления обменом содержит пять триггеров, пять элемен тов И, элемент ИЛИ, три элемента задержки и генератор импульсов, при этом выход генератора импульсов соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с выходами первого, второго и третьего триггеров, третьи входы второго и третьего элементов И соеди нены с выходом четвертого триггера, единичный вход первого триггера и нулевые входы второго, третьего, четвертого и пятого триггеров соединены с выходом элемента ИЛИ, первый вход которого является входом установки в исходное положение устройства, выход второго элемента И соединен с нулевым входом второго триггера, выход третьего элемента И соединен с нулевым входом третьего триггера и через первый элемент задержки с единичным входом пятого т риггера, нулевой вход которого соединен с выходом второго элемента И, выход пятого триггера соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом пятого элемента И, выход четвертого элемента И соединен с единичным входом второго триггера, выход первого элемента И соединен с нулевым входом первого триггера и единичным входом четвертого триггера, единичный вход третьего триггера соединен с выходом Окончание преобразования аналого-цифрового преобразователя, выход схемы сравне-. ния соединен с вторым входом элемента. ИЛИ и через второй.элемент задержки с единичным входом второго триггера, выходы первого и второго элементов И соединены со счетным входом счетчика .адреса, выход второго элемента И через третий элемент задержки соединен с входом Начало преобразования аналого-цифрового преобразователя, при этом каждый из блоков управления вводом группы содержит регистр начального адреса, регистр конечного адреса, два узла сравнения, счетчик, дешифратор, четьфе элемента И, два триггера, элемент задержки и магистральный усилитель, причем выходы регистров начального и конечного адресов соединены соответственно с первыми входами первого и второго узлов сравнения, вторые входы которых соединены соответственно с первым и вторым выходами счетчика, выход первого триггера соединен с первым входом первого элемента И, выход которого соединен со счетным входом счетчика и через элемент задержки - с первыми входами второго и третьего элементов И, вторые входы которых соединены соответственно с выходами второго и первого узлов сравненияJ выходы второго и третьего элементов И соединены

с первыми входами первого ft второго триггеров, выход дешифратора соединен с управляющими входами регистров начального и конечного адресов, магистрального усилителя и первым входом четвертого элемента И, выход которого соединен с вторым входом второго триггера, информационные входы и входы записи регистров начального и конечного адресов соединены с информационной шиной и шиной записи соответствукицей цифровой вычислительной машины, шина прерывания которой соединена с выходом первого узла сравнения, а адресная шина и шина чтения цифровой вычислительной машины соединены соответственно с входом дешифратора и вторым входом четвертого элемента И, выход магистрального усилителя соединен с информационной шиной цифровой вычислительной машины, информационные входы магистральных усилителей всех блоков управления вводом соединены с информационным выходом аналого-цифрового преобразователя, выход первого элемента И блока управления обменом соединен со сбросовыми входами первого и второго триггеров и счетчика всех блоков управления вводом группы, вторые входы первых элементов И которых соединены с выходом третьего элемента И блока управления обменом, а выходы вторых триггеров - с соответствующими входами пятого элемента и блока управления обменом, единичный вход второго триггера, второй управляющий вход аналоговой вычислительной машины и входы запуска цифровых вычислительных машин являются входом Пуск устройства.

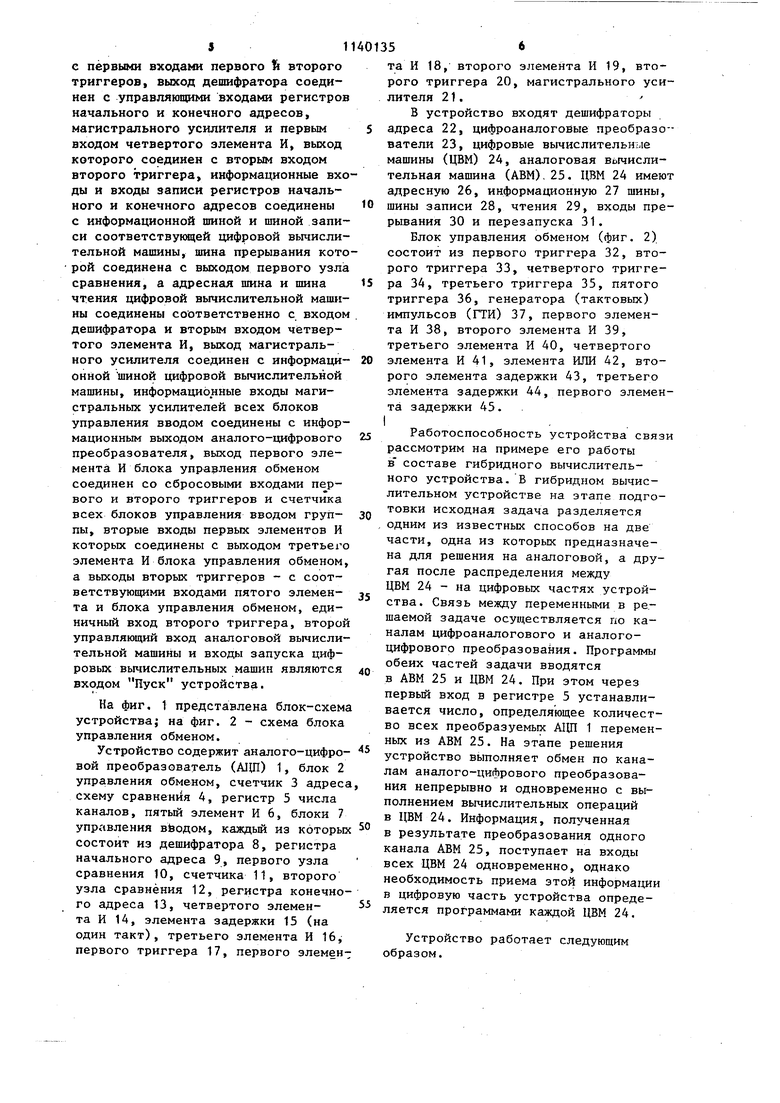

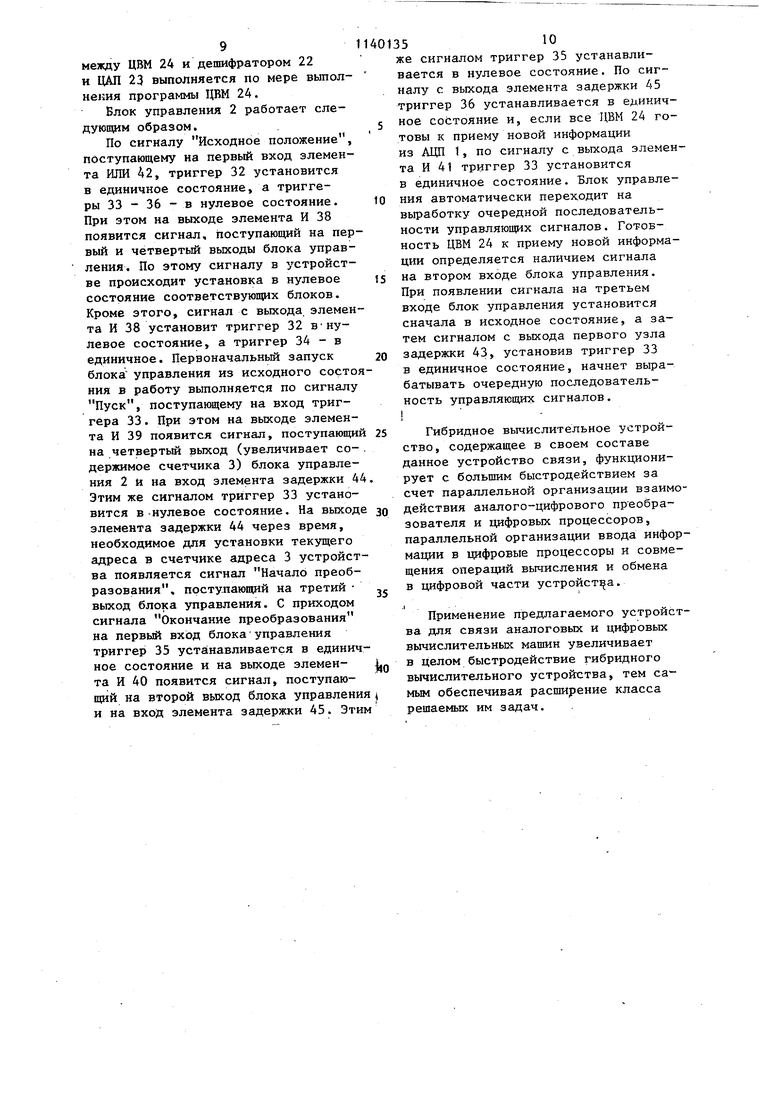

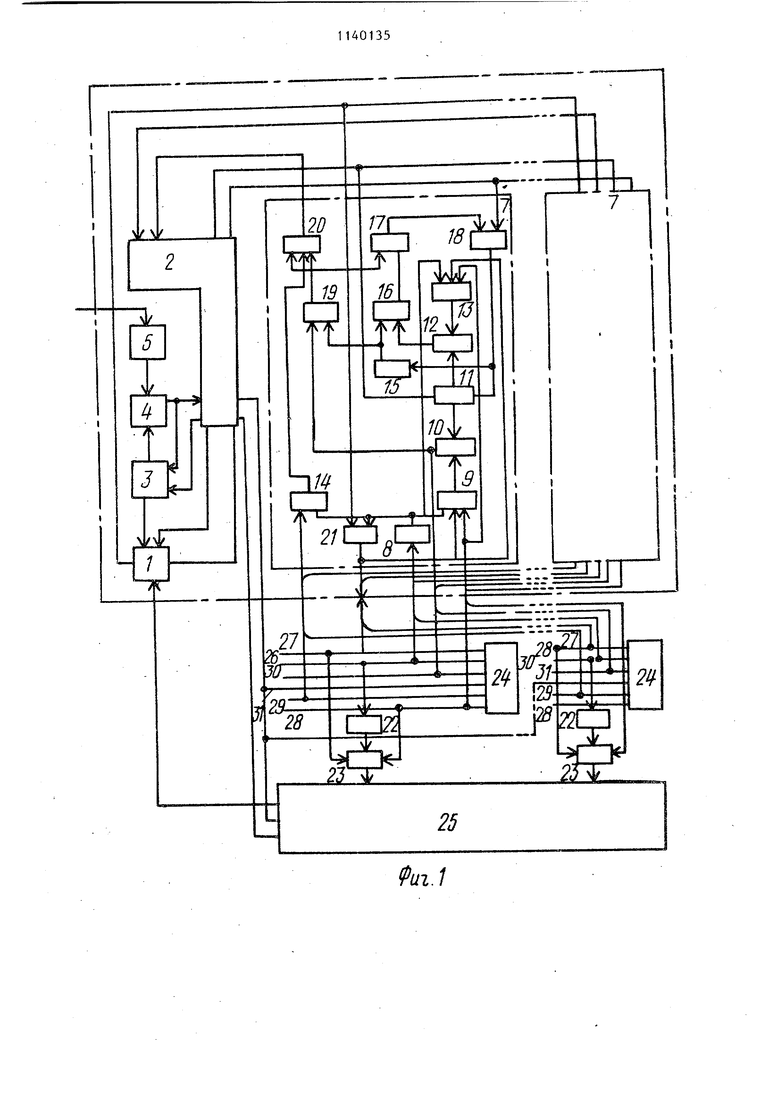

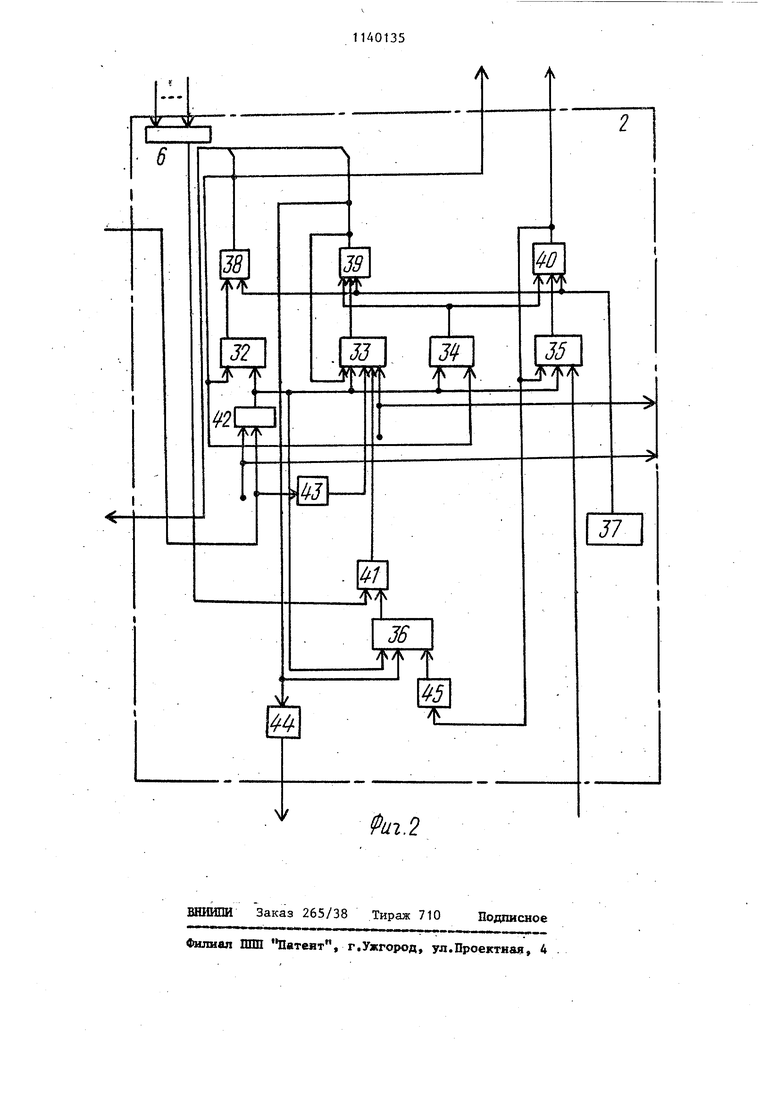

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема блока управления обменом.

Устройство содержит аналого-цифровой преобразователь (А1Щ) 1, блок 2 управления обменом, счетчик 3 адреса схему сравнения 4, регистр 5 числа каналов, пятый элемент И 6, блоки 7 управления вЬодом, каждый из которых состоит из дешифратора 8, регистра начального адреса 9, первого узла сравнения 10, счетчика 11, второго узла сравнения 12, регистра конечного адреса 13, четвертого элемента И 14, элемента задержки 15 (на один такт), третьего элемента И 16, первого триггера 17, первого элемента И 18, второго элемента И 19, второго триггера 20, магистрального усилителя 21.

В устройство входят дешифраторы адреса 22, цифроаналоговые преобразователи 23, цифровые вычислительные машины (ЦВМ) 24, аналоговая вычислительная машина (АВМ). 25. ЦВМ 24 имею адресную 26, информационную 27 шины, шины записи 28, чтения 29, входы прерывания 30 и перезапуска 31.

Блок управления обменом (фиг. 2) состоит из первого триггера 32, второго триггера 33, четвертого триггера 34, третьего триггера 35, пятого триггера 36, генератора (тактовых) импульсов (ГТИ) 37, первого элемента И 38, второго элемента И 39, третьего элемента И 40, четвертого элемента И 41, элемента ШШ 42, второго элемента задержки 43, третьего элемента задержки 44, первого элемента задержки 45. I

Работоспособность устройства связ рассмотрим на примере его работы в составе гибридного вычислительного устройства. В гибридном вычислительном устройстве на этапе подготовки исходная задача разделяется одним из известных способов на две части, одна из которых предназначена для решения на аналоговой, а другая после распределения между ЦВМ 24 - на цифровых частях устройства. Связь между переменными в решаемой задаче осуществляется по каналам цифроаналогового и аналогоцифрового преобразования. Программы обеих частей задачи вводятся в АВМ 25 и ЦВМ 24. При этом через первьй вход в регистре 5 устанавливается число, определяющее количество всех преобразуемых АЦП 1 переменных из АВМ 25. На этапе решения устройство выполняет обмен по каналам аналого-цифрового преобразования непрерывно и одновременно с выполнением вычислительных операций в ЦВМ 24. Информация, полученная в результате преобразования одного канала АВМ 25, поступает на входы всех ЦВМ 24 одновременно, однако необходимость приема зтой информации в цифровую часть устройства определяется программами каждой ЦВМ 24.

Устройство работает следующим образом.

71

В исходном состоянии блок 2 сигналом с четвертого выхода устанавливает счетчик 3 и сигналом с первого выхода счетчик 11 и триггеры 17 и 20 в нулевое состояние и сигналом с шее того выхода устанавливает АВМ 25 в исходное состояние. На инверсных выходах триггеров 17 и 20 вырабатываются при этом соответственно сигналы Разрешение приема и Готовность приема. Запуск АВМ 25 и ЦВМ 24 производится вьщачей сигнала с пятого выхода блока 2. В регистры 9 и 13 по сигналу с входачетвертой группы входов (с шины записи 28 ЦВМ 24) и при наличии разрешения на выходе де,шифратора 8 заносятся соответственно начальный и конечный адрес приема канала преобразования. В состоянии обмена информацией на выходе элемента 6 при наличии сигналов Готовност приема по всем входам вырабатывается сигнал, запускающий блок 2 на циклическую работу. Сигналом с четвертого .выхода блока 2 содержимое счетчика 3 увеличивается на единицу, тем самым формируется текущий адрес канала преобразования. АЦП 1 по сигналу Начало преобразования с третьего выхода блоки 2 преобразует аналоговый сигнал АВМ 25 в дискретную форму и подает его на первый вход

усилителя 21, вырабатывая при этом сигнал Окончание преобразования, который поступает на первый вход блока 2. Блок 2 с приходом сигнала Окончание преобразования вырабатывает управляющий сигнал, который поступает на первый вход элемента И 18, который вьфабатывает сигнал, который поступаетна второй вход счетчика 11, содержимое которого увеличивается на единицу, и на вход элемента задержки 15, на вьгходе которого сигнал появится с задержкой на время срабатывания счетчика 11 и узлов 10 и 12. После установления текущего адреса в счетчике 11 возможны несколько вариантов функционирования элементов блока 7. Если содержимое счетчика 11 меньше содержимого регистра 9 и содержимое регистра 13 не меньше содержимого регистра 9 и больше (в начальный момент) содержимого счетчика 11, узлы 10 и 12 не.вьфабатывают управляющих сигналов. Состояние триггеров 17 и 20 не изменяется и блок 2

58

вырабатывает управляющие сигналы, обеспечивающие преобразование сигнала из следующего канала АВМ 25. Если содержимое счетчика 11 не меньше содержимого регистра 9, на выходе узла 10 вырабатывается управляющий сигнал, который поступает на первый вход элемента И 19, который при наличии сигналов с выходов узла 10 и элемента 15, вьфабатывает сигнал, который по третьему входу триггера 20 устанавливает его в единичное состояние. Изменение состояния триггера 20 в любом из блоков 7 запрещает появление на входе элемента И 6 сигнала готовности приема новой информации. Управляющий сигнал с выхода узла 10, поступив на выход третьей группы выходов (вход прерывания 30 ЦВМ 24), вызывает прерывание (если оно разрешено) работы ЦВМ 24. По сигналу прерывания ЦВМ 24 выдает с входа третьей группы входов (шины адреса 26) в дешифратор 8 адрес, соответствующий усилителю 21, Информация с выхода А1Щ 1 через первый вход .усилителя 21 поступает на инормационную шину 27 ЦВМ 24. По окончании приема информации с шины чтения 29 поступает сигнал на первый вход элемента И 14, которьй при наичии разрешения на выходе дешифраора 8 вырабатывает сигнал, который по второму входу триггера 20 установит его в нулевое состояние, опрееляя тем самым готовность ЦВМ 24 к приему информации со следующего анала преобразования. Если содержимое регистра 13 и счетчика 11 совпадает, ня выходе узла 12 вырабатывается сигнал, который поступает на вход элемента И 16. Элемент И 16, анализируя наличие сигналов на обоих входах, вырабатывает сигнал, который устанавливает по второму входу триггер 17 в единичное состояние, сигнал с инверсного выхода которого, поступая на второй

вход элемента И 18, запрещает вьфаботку управляющего сигнала. Аналогоцифровое преобразование выполняется до тех пор, пока содержимое счетчика 3 не совпадает с содержимым регистру 5. При этом сигнал с выхода схеы. 4, поступая в блок 2, произведет установку устройства в исходное состояние. Запуск блока 2 из исходного состояния в работу происходит автоматически. Обмен информацией

91

между ЦВМ 24 и дешифратором 22 и ЦАП 23 выполняется по мере вьтолнепия программы ЦВМ 24.

Блок управления 2 работает следующим образом.

По сигналу Исходное положение, поступающему на первый вход элемента ИЛИ А2, триггер 32 установится в единичное состояние, а триггеры 33 - 36 - в нулевое состояние. При этом на выходе элемента И 38 появится сигнал, поступающий на первый и четвертый выходы блока управления. По этому сигналу в устройстве происходит установка в нулевое состояние соответствующих блоков. Кроме этого, сигнал с выхода элемента И 38 установит триггер 32 внулевое состояние, а триггер 34 - в единичное. Первоначальный запуск блока управления из исходного состоя ния в работу выполняется по сигналу Пуск, поступающему на вход триггера 33. При этом на выходе элемента И 39 появится сигнал, поступающий на четвертый выход (увеличивает со-, держимое счетчика 3) блока управления 2 h на вход элемента задержки 44 Этим же сигналом триггер 33 установится в-нулевое состояние. На выходе элемента задержки 44 через время, необходимое для установки текущего адреса в счетчике адреса 3 устройства появляется сигнал Начало преобразования, поступающий на третий выход блока управления. С приходом сигнала Окончание преобразования на первый вход блокауправления триггер 35 устанавливается в единичное состояние и на выходе элемента И 40 появится сигнал, поступающий на второй вькод блока управления и на вход элемента задержки 45. Этим

4013510

же сигналом триггер 35 устанавливается в нулевое состояние. По сигналу с выхода элемента задержки 45 триггер 36 устанавливается в единичное состояние и, если все ЦВМ 24 готовы к приему новой информации из АЦП 1, по сигналу с выхода элемента И 41 триггер 33 установится в единичное состояние. Блок управления автоматически переходит на

выработку очередной последовательности управляющих сигналов. Готовность ЦВМ 24 к приему новой информации определяется наличием сигнала

t5 на втором входе блока управления. При появлении сигнала на третьем входе блок управления установится сначала в исходное состояние, а затем сигналом с выхода первого узла

0 задержки 43, установив триггер 33 в единичное состояние, начнет вырабатывать очередную последовательность управляющих сигналов. I

5 Гибридное вычислительное устройство, содержащее в своем составе данное устройство связи, функционирует с большим быстродействием за счет параллельной организации взаимодействия аналого-цифрового преобразователя и цифровых процессоров, параллельной организации ввода информации в цифровые процессоры и совмещения операций вычисления и обмена в цифровой части устройства.

.1 .

Применение предлагаемого устройства для связи аналоговых и цифровых вычислительных машин увеличивает

Q в целом быстродействие гибридного вычислительного устройства, тем са-

мым обеспечивая расширение класса решаемых им задач.

;лу W

/W

JV 7t

1ж

Wt

ж

Й/2.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3427301/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-15—Публикация

1983-01-14—Подача