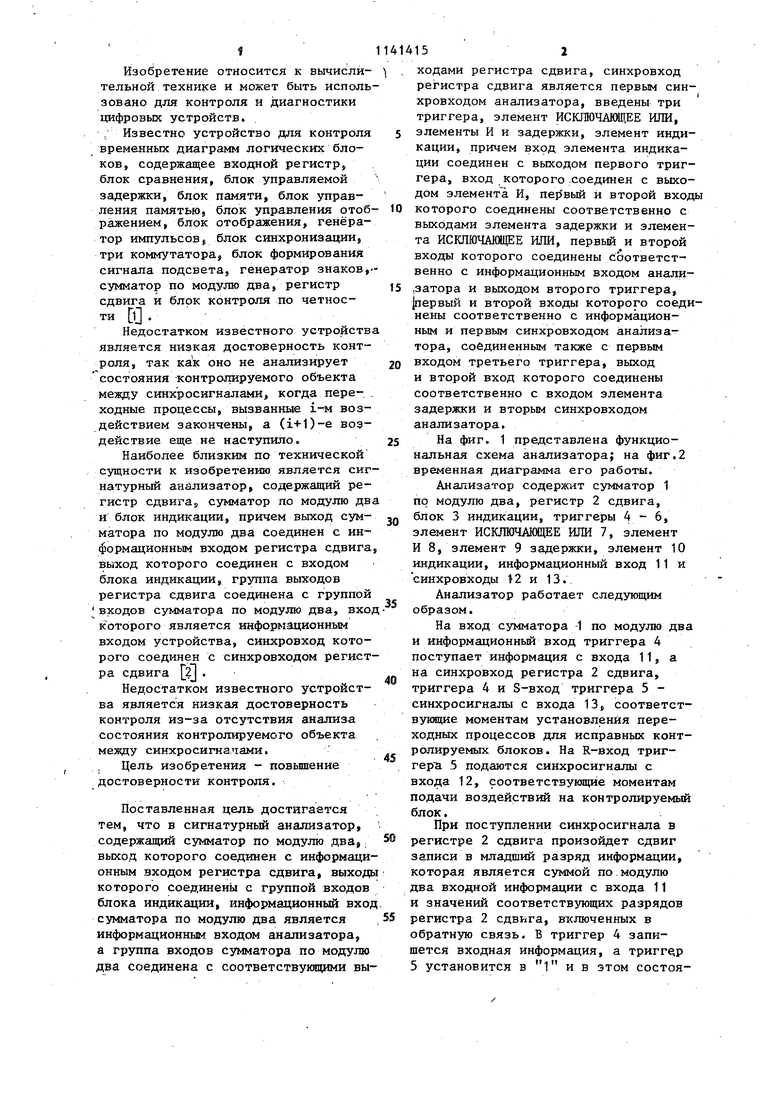

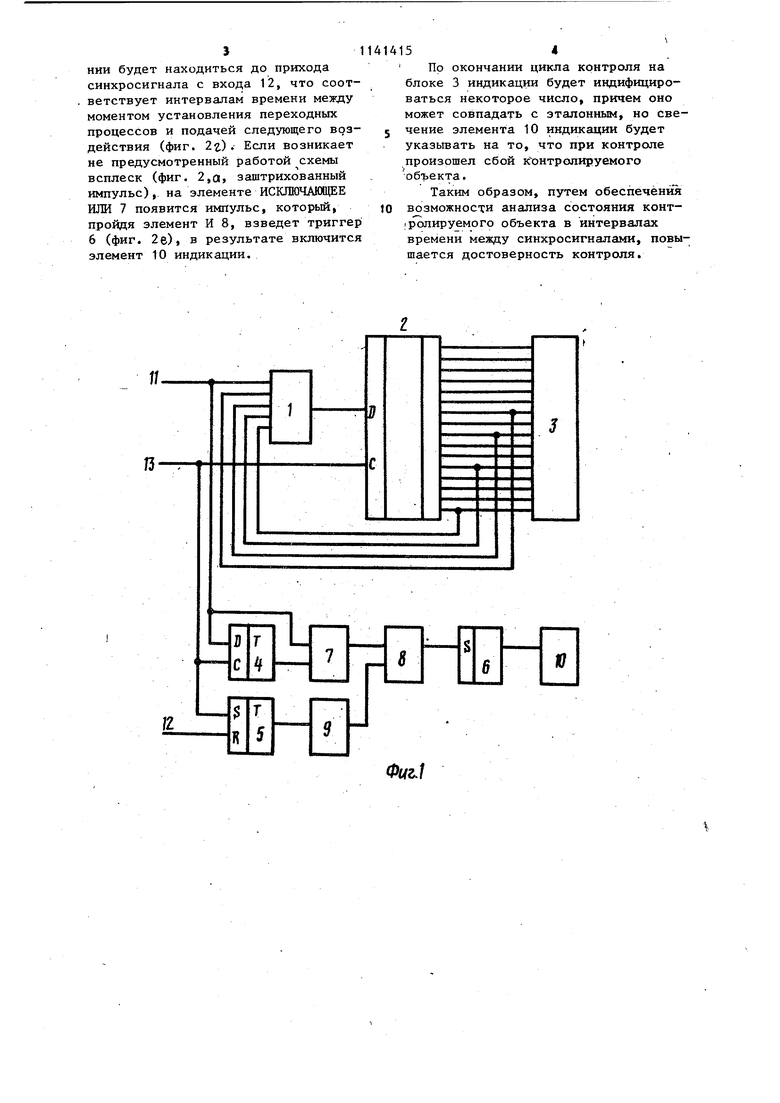

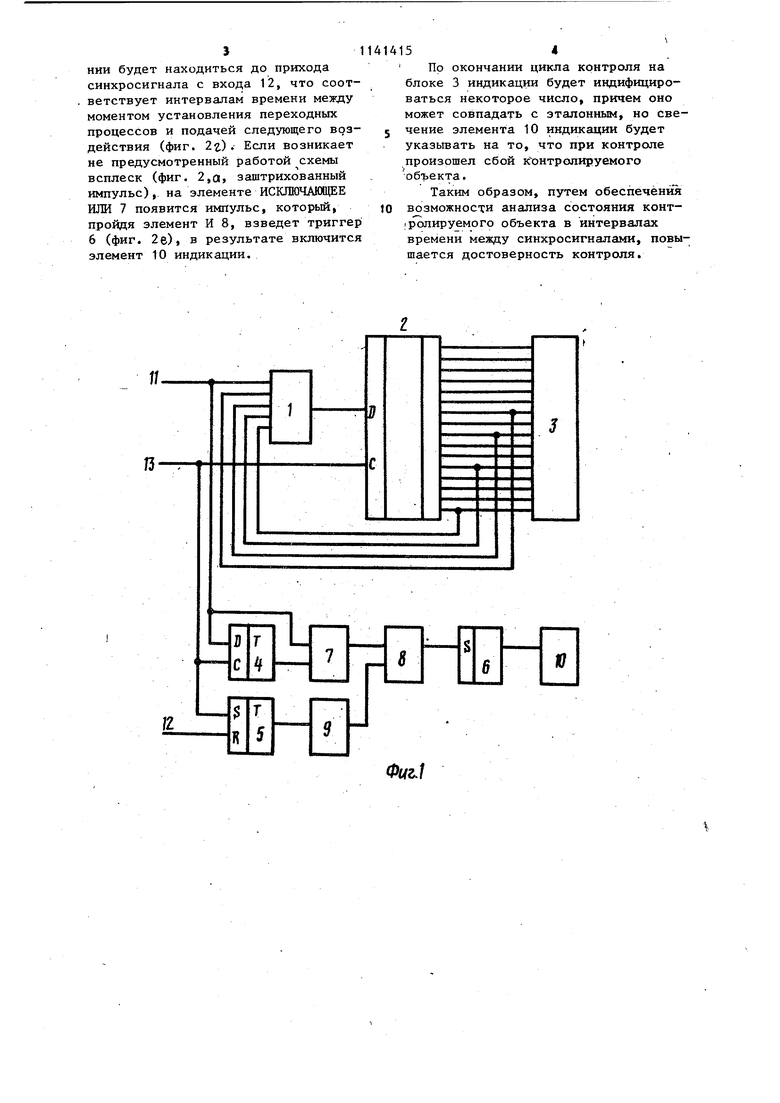

Изобретение относится к вычислительной технике и может быть исполь зовано для контроля и диагностики цифровых устройств. , Известно устройство для контроля временных диаграмм логических блоков, содержащее входной регистр, блок сравнения, блок управляемой задержки, блок памяти, блок управления памятью, блок управления отоб ражением, блок отображения, генератор импульсовt блок синхронизации, три коммутатора, блок формирования сигнала подсвета, генератор знаков, сумматор по модулю два, регистр сдвига и блок контроля по четности l . . Недостатком известного устройств является низкая достоверность контроля, так как оно не анализирует состояния контролируемого объекта между синхросигналами когда переходные процессы, вызванные i-м воздействием закончены, а (i+1)-e воддействие еще не наступило. Наиболее близким по технической сущности к изобретению является сиг натурный анализатор, содержащий регистр сдвига., сумматор по модулю дв и блок индикации, причем выход сумматора по модулю два соединен с информационным входом регистра сдвига выход которого соединен с входом блока индикации, группа выходов регистра сдвига соединена с группой входов сумматора по модулю два, вхо которого является информационным входом устройства, синхровход которого соединен с синхровходом регист ра сдвига . Недостатком известного устройства является низкая достоверность контроля из-за отсутствия анализа состояния контролируемого объекта между синхросигналами. Цель изобретения - повьшение достоверности контроля. Поставленная цель достигается тем, что в сигнатурный анализатор, содержащий сумматор по модулю два,; выход которого соединен с информаци онным входом регистра сдвига, выход которого соединены с группой входов блока индикаций, информационный вхо сумматора по модулю два является информационным входом анализатора, а группа входов сумматора по модулю два соединена с соответствукяцими вы ходами регистра сдвига, синхровход регистра сдвига является первым синхровходом анализатора, введены три триггера, элемент ИСКЛЮЧАЩЕЕ ИЛИ, элементы И и задержки, элемент индикации, причем вход элемента индикации соединен с выходом первого триггера, вход которого .соединен с выходом элемента И, первый и второй входы которого соединены соответственно с выходами элемента задержки и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с информационным входом анали.затора и выходом второго триггера, |первый и второй входы которого соединены соответственно с информационным и первым синхровходом анализатора, соединенным тавсже с первым входом третьего триггера, выход и второй вход которого соединены соответственно с входом элемента задержки и вторым синхровходом анализатора. На фиг. 1 представлена функциональная схема анализатора; на фиг,2 временная диаграмма его работы. Анализатор содержит сумматор 1 по модулю два, регистр 2 сдвига, блок 3 индикации, триггеры 4-6, элемент ИСКЛЮЧАЩЕЕ ИЛИ 7, элемент И 8, элемент 9 задержки, элемент 10 индикации, информационный вход 11 и синхровходы 12 и 13. Анализатор работает следующим образом. На вход сумматора 1 по модулю два и информационньй вход триггера 4 поступает информация с входа 11, а на синхровход регистра 2 сдвига, триггера 4 и S-вход триггера 5 синхросигналы с входа 13, соответствующие моментам установления переходных процессов для исправных контролируемых блоков. На R-вход триггера 5 подаются синхросигналы с входа 12, соответствующие моментам подачи воздействий на контролируемый блок. При поступлении синхросигнала в регистре 2 сдвига произойдет сдвиг записи в младший разряд информации, которая является суммой по модулю два входной информации с входа 11 и значений соответствующих разрядов регистра 2 сдвига, включенных в обратную связь. В триггер 4 запишется входная информация, а триггер 5 установится в 1 и в этом состояJ 1

НИИ будет находиться до прихода синхросигнала с входа 12, что соответствует интервалам времени между моментом установления переходных процессов и подачей следующего воздействия (фиг. 2г). Если возникает не предусмотренный работой схемы всплеск (фиг. 2,0, заштрихованный импульс) ,. на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 7 появится импульс, который, пройдя элемент И 8, взведет триггер 6 (фиг. 2е), в результате включится элемент 10 индикации.

414154

По окончании цикла контроля на блоке 3 индикации будет индифицироваться некоторое число, причем оно может совпадать с эталонным, но свечение элемента 10 индикации будет указьшать на то, что при контроле произошел сбой контролируемого объекта.

Таким образом, путем обеспечёнйя 10 возможности анализа состояния конт.ролируемого объекта в интервалах времени между синхросигналами, повышается достоверность контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Сигнатурный анализатор | 1984 |

|

SU1270773A1 |

| Сигнатурный анализатор | 1987 |

|

SU1444776A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Сигнатурный анализатор | 1982 |

|

SU1065857A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1336010A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Сигнатурный анализатор | 1984 |

|

SU1262501A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

СИГНАТУРНЫЙ АНАЛИЗАТОР, содержавший сумматор по модулю два, выход которого соединен с информационным входом регистра сдвига, выходы которого соединены с группой входов блока индикации, информационный вход сумматора по модулю два является информационным входом анализатора, а группа входов сумматора по модулю два соединена с соответствующими выходами регистра сдвига, синхровход регис гра сдвига является первым синхровходом анализатора, отличающийся тем, что, с целью повышения достоверности контроля, в него введены три триггера, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И и задержки, элемент индикации, причем вход элемента индикации соединен с выходом первого триггера, вход которого соединен с выходом элемента И, первый и второй входы которого соединены соответственно с выходами элемента задержки и элемента ИСКЛЮЧАЮОЩЕ ИЛИ, первый и второй входы которого соединены соответственно с инфо1 1ационным входом анализатора и выходом - (Л второго триггера, первый и второй входы которого соединены соответственно с информационным и первым синхровходом анализатора, соединенным также с первым входом третьего триггера, выход и второй вход которого соединены соответственно с входом элемента задержки к вторым синхровхЪдом анализатора. 4 СП

$

l

5

R

S

ю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля временных диаграмм логических блоков | 1979 |

|

SU788111A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника, 1977 № 5, с | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| . | |||

Авторы

Даты

1985-02-23—Публикация

1981-11-25—Подача