o

05

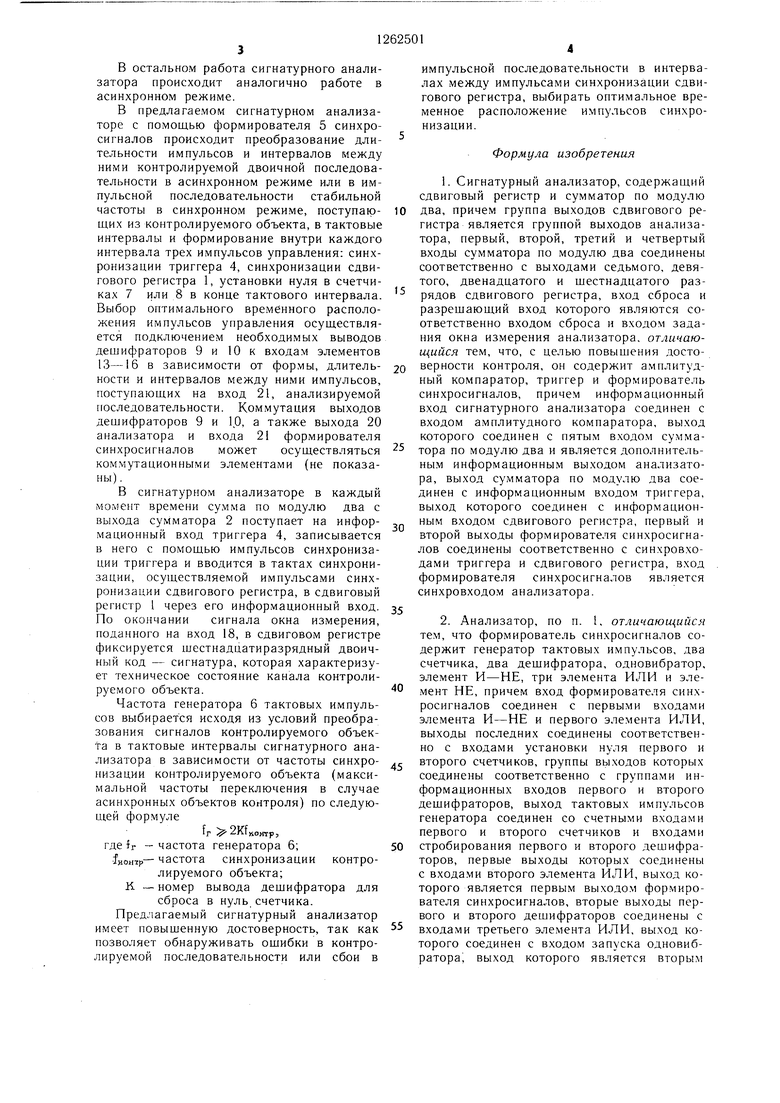

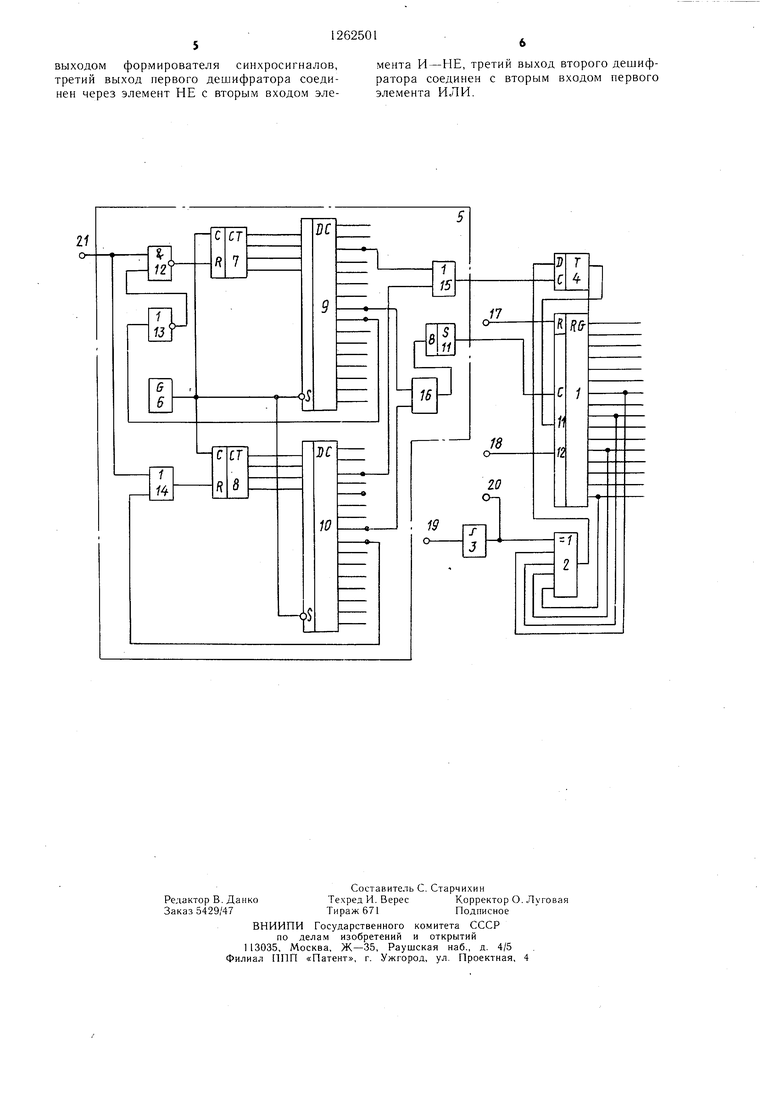

ю сл Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностирования цифровых объектов. Целью изобретения является повышение достоверности контроля. На чертеже приведена функциональная схема сигнатурного анализатора. Анализатор содержит сдвиговый регистр 1, сумматор 2 по модулю два, амплитудный компаратор 3, триггер 4, формирователь 5 синхросигналов, в состав которого входят генератор 6 тактовых импульсов, двоичные счетчики 7 и 8, дешифраторы 9 и 10, одновибратор 11, элемент И НЕ 12, элемент НЕ 13, элементы ИЛИ 14-16, вход 17 установки в нуль сдвигового регистра, вход 18 окна измерения, информационный вход 19, выход 20 амплитудного компаратора, вход 21 формирователя синхроимпульсов. Выход 20 амплитудного комнаратора 3 является дополнительным информационным выходом анализатора. Сигнатурный анализатор допускает работу в двух режимах: асинхронном и синхронном и работает следуюшим образом. В асинхронном режиме работы выход 20 анализатора соединяют с входом 21 формирователя 5 синхросигналов. Сигнал установки в нуль, подаваемый на вход 17, устанавливает сдвиговый регистр 1 в нуль. Информация в виде импульсов единичных уровней и интервалов между ними различной длительности, подаваемая от контролируемого цифрового объекта на вход 19, поступает на вход амплитудного компаратора 3, с помошью которого поступаюшие импульсы с пологими фронтами и спадами преобразуются в импульсы прямоугольной формы. С выхода амплитудного компаратора информация поступает на вход 2 формирователя синхросигналов и на первый вход сумматора 2, где она суммируется по модулю два со значениями информации в цепях обратной связи сдвигового регистра 1 (до прихода сигнала окна измерения - с нулевым). Затем сумма по модулю два поступает на информационный вход триггера 4. Генератор 6 формирователя 5 синхросигналов генерирует импульсную последовательность стабильной частоты, которая непрерывно поступает на счетные входы двоичных счетчиков 7 и 8 и входы стробирования дешифраторов 9 и 10. При этом частота работы генератора 6 превыщает частоту синхронизации контролируемого объекта. При поступлении на вход 21 импульса с единичным уровнем счетчик 8 устанавливается в нулевое состояние, на всех выходах дешифратора 10 устанавливаются нулевые уровни, кроме нулевого выхода, а счетчик 7 начинает подсчет импульсов, так как на его входе установки в нуль устанавливается нулевой уровень вместо единичного, и на выходах дешифратора 9 будут последовательно появляться импульсы единичного уровня по мере поступления на его вход стробирования импульсов нулевого уровня. Появление импульса на первом выходе (по порядку активации одного из трех выходов, подключенных к последующим цепям) приводит к появлению такого же импульса на выходе элемента ИЛИ 15 и как следствие к записи суммы по модулю два в триггер 4, с выхода которого эта сумма подается на информационный вход сдвигового регистра 1. Появление импульса на втором выходе дешифратора 9 приводит к появлению такого же импульса на выходе элемента ИЛИ 16 и запуску одновибратора 11. Импульс, формируемый одновибратором и подаваемый на вход синхронизации сдвигового регистра 1, является синхронизирующим: он производит сдвиг кода в регистре и ввод в него суммы по модулю два. При этом к этому времени на вход 18 подается сигнал окна измерения. Подаваемый на вход 18 сигнал окна измерения определяет своей длительностью длину двоичной последовательности, поступающей на информационный вход 19 для преобразования ее в сигнатуру. Появление импульса на третьем выходе дещифратора 9 приводит (с помощью эле.ментов 12 и 13) к установке счетчика 7 в нулевое состояние, причем в интервале между импульсами единичного уровня, поступающими на счетный вход счетчика, после чего данный цикл снова повторяется и будет повторяться, формируя тактовые интервалы, до появления на входе 19 сигнала с нулевым уровнем. При появлении на информационном входе 19 сигнала с нулевым уровнем на выходе амплитудного компаратора 3 устанавливается нулевой уровень, и так как выход 20 соединен с входом 21, то этот уровень устанавливается на первых входах элементов 12 и 14, в связи с чем счетчик 7 устанавливается в нулевое состояние, на всех выходах дешифратора 9 (кроме нулевого) также устанавливаются нулевые уровни, а счетчик 8 начинает подсчет импульсов, так как на его входе установки в нуль устанавливается нулевой уровень, в работу включается дешифратор 10. Дальше работа сигнатурного анализатора происходит аналогично рассмотренной при поступлении на вход 21 импульса с единичным уровнем. В синхронном режиме выход 20 не подключают к выходу 21, на этот вход подают импульсную последовательность стабильной частоты от контролируемого цифрового объекта. В остальном работа сигнатурного анализатора происходит аналогично работе в асинхронном режиме. В предлагаемом сигнатурном анализаторе с помощью формирователя 5 синхросигналов происходит преобразование длительности импульсов и интервалов между ними контролируемой двоичной последовательности в асинхронном режиме или в импульсной последовательности стабильной частоты в синхронном режиме, поступающих из контролируемого объекта, в тактовые интервалы и формирование внутри каждого интервала трех импульсов управления: синхронизации триггера 4, синхронизации сдвигового регистра 1, установки нуля в счетчиках 7 или 8 в конце тактового интервала. Выбор оптимального временного расположения импульсов управления осуществляется подключением необходимых выводов дешифраторов 9 и 10 к входам элементов 13-16 в зависимости от формы, длительности и интервалов между ними импульсов, поступающих на вход 21, анализируемой последовательности. Коммутация выходов дешифраторов 9 и 10, а также выхода 20 анализатора и входа 21 формирователя синхросигналов может осуществляться коммутационными элементами (не показаны) . В сигнатурном анализаторе в каждый момент времени сумма по модулю два с выхода сумматора 2 поступает на информационный вход триггера 4, записывается в него с помощью импульсов синхронизации триггера и вводится в тактах синхронизации, осуществляемой импульсами синхронизации сдвигового регистра, в сдвиговый регистр 1 через его информационный вход. По окончании сигнала окна измерения, поданного на вход 18, в сдвиговом регистре фиксируется шестнадцатиразрядный двоичный код - сигнатура, которая характеризует техническое состояние канала контролируемого объекта. Частота генератора 6 тактовых импульсов выбирается исходя из условий преобразования сигналов контролируемого объекта в тактовые интервалы сигнатурного анализатора в зависимости от частоты синхронизации контролируемого объекта (максимальной частоты переключения в случае асинхронных объектов контроля) по следующей формуле IT 2Kl контр 3 где fr - частота генератора 6; ноитр- частота синхронизации контролируемого объекта; К - номер вывода дешифратора для сброса в нуль счетчика. Пред.лагаемый сигнатурный анализатор имеет повышенную достоверность, так как позволяет обнаруживать ошибки в контролируемой последовательности или сбои в импульсной последовательности в интервалах между импульсами синхронизации сдвигового регистра, выбирать оптимальное временное расположение импульсов синхронизации. Формула изобретения 1.Сигнатурный анализатор, содержащий сдвиговый регистр и сумматор по модулю два, причем группа выходов сдвигового регистра является группой выходов анализатора, первый, второй, третий и четвертый входы сумматора по модулю два соединены соответственно с выходами седьмого, девятого, двенадцатого и щестнадцатого разрядов сдвигового регистра, вход сброса и разрещающий вход которого являются соответственно входом сброса и входом задания окна измерения анализатора, отличающийся тем, что, с целью повышения достоверности контроля, он содержит амплитудный компаратор, триггер и формирователь синхросигналов, причем информационный вход сигнатурного анализатора соединен с входом амплитудного компаратора, выход которого соединен с пятым входом сумматора по модулю два и является дополнительным информационным выходом анализатора, выход сумматора по модулю два соединен с информационным входом триггера, выход которого соединен с информационным входом сдвигового регистра, нервый и второй выходы формирователя синхросигналов соединены соответственно с синхровходами триггера и сдвигового регистра, вход формирователя синхросигналов является синхровходом анализатора. 2.Анализатор, по п. 1, отличающийся тем, что формирователь синхросигналов содержит генератор тактовых импульсов, два счетчика, два дешифратора, одновибратор, элемент И-НЕ, три элемента ИЛИ и эле.мент НЕ, причем вход формирователя синхросигналов соединен с первыми входами элемента И-НЕ и первого элемента ИЛИ, выходы последних соединены соответственно с входами установки нуля первого и второго счетчиков, группы выходов которых соединены соответственно с группами информационных входов первого и второго дешифраторов, выход тактовых импульсов генератора соединен со счетными входами первого и второго счетчиков и входами стробирования первого и второго дешифраторов, первые выходы которых соединены с входами второго элемента ИЛИ, выход которого является первым выходом формирователя синхросигналов, вторые выходы первого и второго дешифраторов соединены с входами третьего элемента ИЛИ, выход которого соединен с входом запуска одновибратора; выход которого является вторым

выходом формирователя синхросигналов, третий выход первого дешифратора соединен через элемент НЕ с вторым входом элемента И-НЕ, третий выход второго дешифратора соединен с вторым входом первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1987 |

|

SU1501061A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Сигнатурный анализатор | 1984 |

|

SU1270773A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

| Сигнатурный анализатор | 1986 |

|

SU1383358A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностирования цифровых объектов. Целью изобретения является повышение достоверности контроля. Сигнатурный анализатор содержит сдвиговый регистр с обратными связями через многовходовой сумматор по модулю два, триггер, амплитудный компаратор и формирователь синхросигналов. Формирователь синхросигналов, в свою очередь, содержит генератор тактовых импульсов, два счетчика, два дешифратора, одновибратор, элемент И-НЕ, три элемента ИЛИ и элемент НЕ. В предлагаемом сигнатурном анализаторе с помощью формирователя синхросигналов происходит преобразование длительности импульсов и интервалов между ними контролируемой последовательности в тактовые интервалы и формирование внутри каждого интервала оптимальным образом импульсов управления соотзру(, узлами анализатора. Сигнатурный анализатор имеет повышенную достоверность, так как позволяет обнаруживать ошибки в контролируемой после Ф довательноети в интервалах между импульсами синхронизации сдвигового регистра. сл 1 з.п. ф-лы, 1 ил.

| «Зарубежная радиоэлектроника | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| «Электроника | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1986-10-07—Публикация

1984-12-29—Подача