верхнему и нижнему порогам, характерным для .той или иной элементной базы контролируемых цифровых блоков, В случае несоответствия установленному уровню хотя бы одного бита сформированная сигнатура будет отличаться от .эталоннойо Устройство позволяет на- ряду с контролем временных последовательностей цифровых сигналов осу1

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля работоспособности цифровых блоков и локализации неисправных узлов в них.

Цель изобретения повьшение достверности контроля за счет обеспечения контроля уровней входных сигналов.

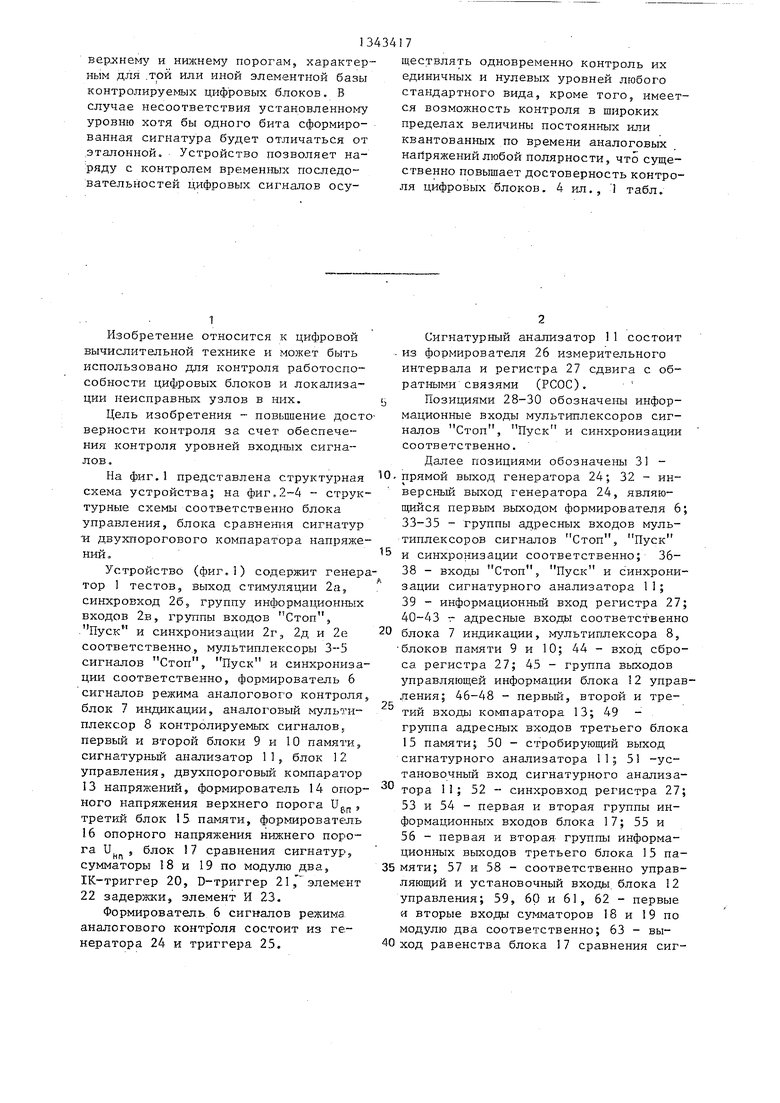

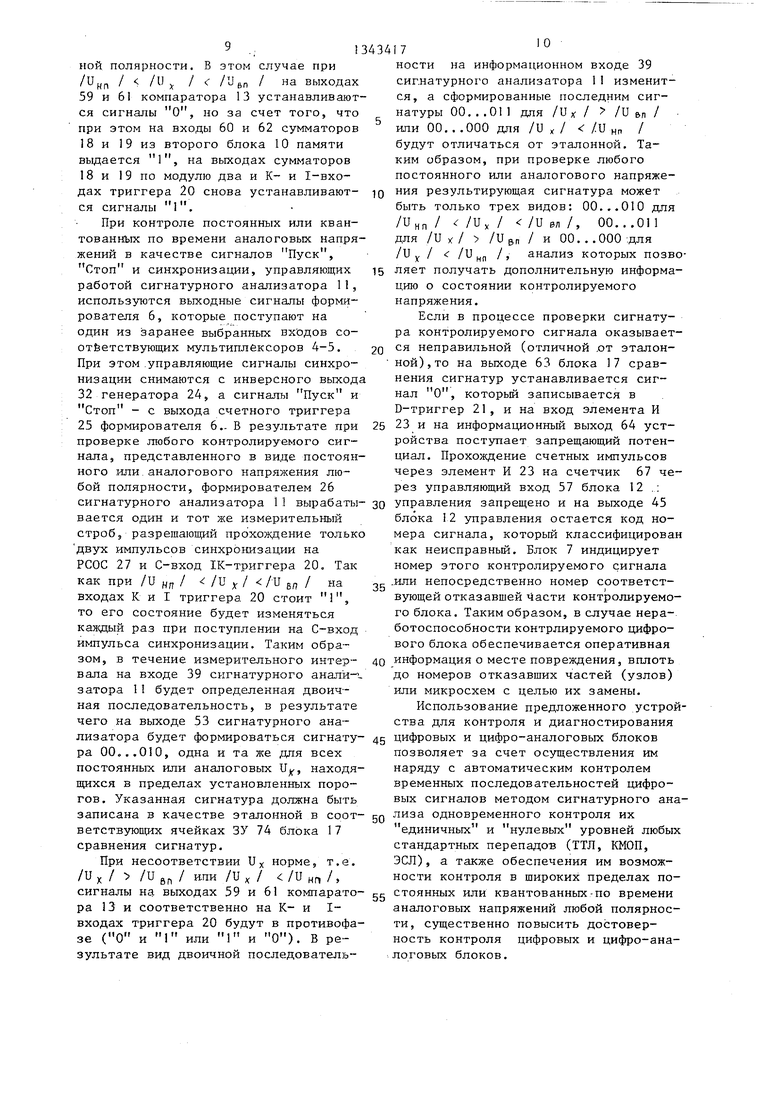

На фиг.1 представлена структурная схема устройства; на фиг,2-4 - структурные схемы соответственно блока управления, блока сравнеш-ш сигнатур и двухпорогового компаратора напряжений ,

Устройство (фиг.) содержит генер тор 1 тестов, выход стимуляции 2а, синхровход 26, группу информационньгх входов 2в, группы входов Стоп, Пуск и синхронизации 2r, 2д и 2е соответственно., мультиплексоры 3-5 сигналов Стоп, Пуск и синхронизации соответственно, формирователь 6 сигнгшов режима аргалогового контроля блок 7 индикации, аналоговый мультиплексор 8 контролируемых сигналов, первый и второй блоки 9 и 10 памяти, сигнатурный анализатор 11, блок 12 управления, двухпороговьй компаратор 13 напряжений, формирователь 14 опорного напряжения верхнего порога и , третий блок 15 памяти, формирователь 16 опорного напряжения нижнего порога и , блок 7 сравнения сигнатур.

МП

сумматоры 18 и 19 по модулю два, 1К-триггер 20, В триггер 21,элемент 22 задержки, элемент И 23,

Формирователь 6 сигналов режима, аналогового контр оля состоит из генератора 24 и триггера 25.

ществлять одновременно контроль их единичных и нулевых уровней любого стандартного вида, кроме того, имеется возможность контроля в широких пределах величины постоянных или квантованных по времени аналоговых напряжений любой полярности, что существенно повьшает достоверность контроля цифровых блоков. 4 ил., 1 табл.

Сигнатурный анализатор 11 состоит . из формирователя 26 измерительного интервала и регистра 27 сдвига с обратными связями (РСОС).

Позициями 28-30 обозначены информационные входы мультиплексоров сигналов Стоп, Пуск и синхронизации соответственно.

Далее позициями обозначены 31 0, прямой выход генератора 24; 32 - инверсный выход генератора 24, являю- пщйся первь м выходом формирователя 6; 33-35 - группы адресных входов мультиплексоров сигналов Стоп, Пуск

5 и синхронизации соответственно; 3638- входы Стоп, Пуск и синхрони- зации сигнатурного анализатора 11;

39- информационный вход регистра 27; 40-43 г- адресные входы соответственно

0 блока 7 индикации, мультигшексора 8, блоков памяти 9 и 10; 44 - вход сброса регистра 27; 45 - группа выходов управляющей информации блока 12 управления; 46-48 - первый, второй и третий входы компаратора 13; 49 - группа адресных входов третьего блока 15 памяти; 50 - стробирующий выход сигнатурного анализатора 11; 51 -установочный вход сигнатурного анализа 0 тора II; 52 - синхровход регистра 27; 53 и 54 - первая и вторая группы информационных входов блока 17; 55 и 56 - первая и вторая- группы информационных выходов третьего блока 15 па35 мяти; 57 и 58 - соответственно управляющий и установочный входы, блока 12 управления; 59, 60 и 61, 62 - первые и вторые входы сумматоров 18 и 19 по модулю два соответственно; 63 - вы40 ход равенства блока 17 сравнения сиг5

313

натур; 64 - информационный выход устройства; 65 - вход начальной установки устройства.

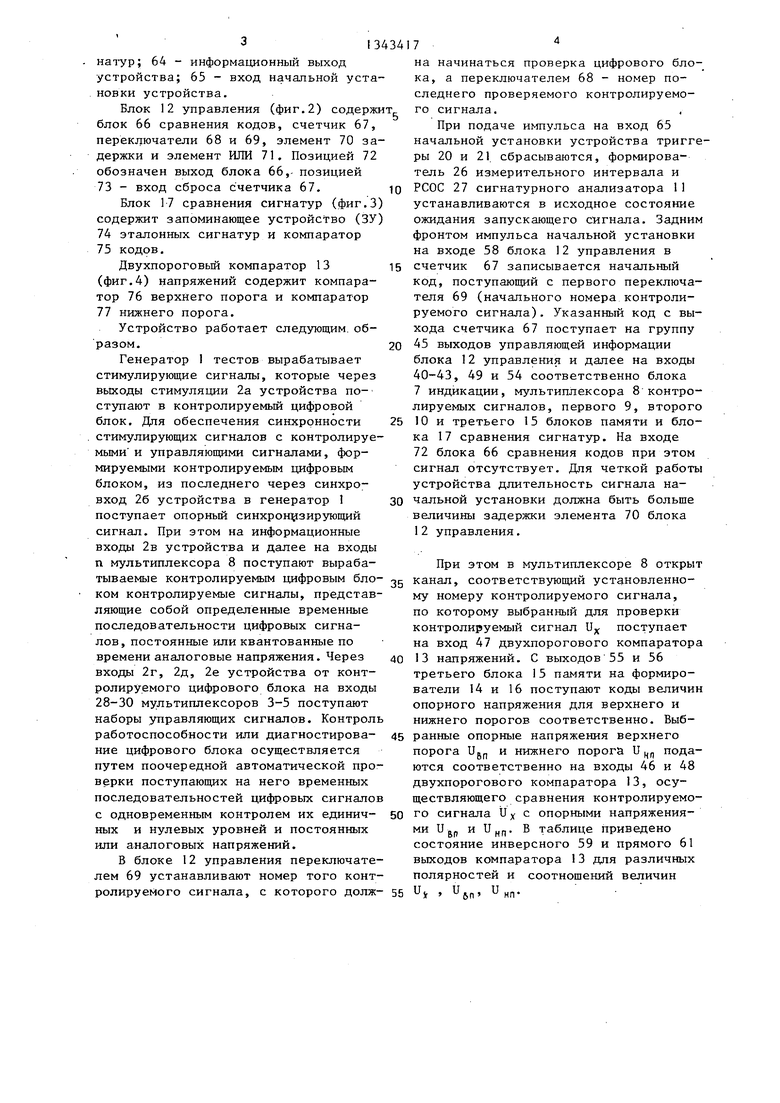

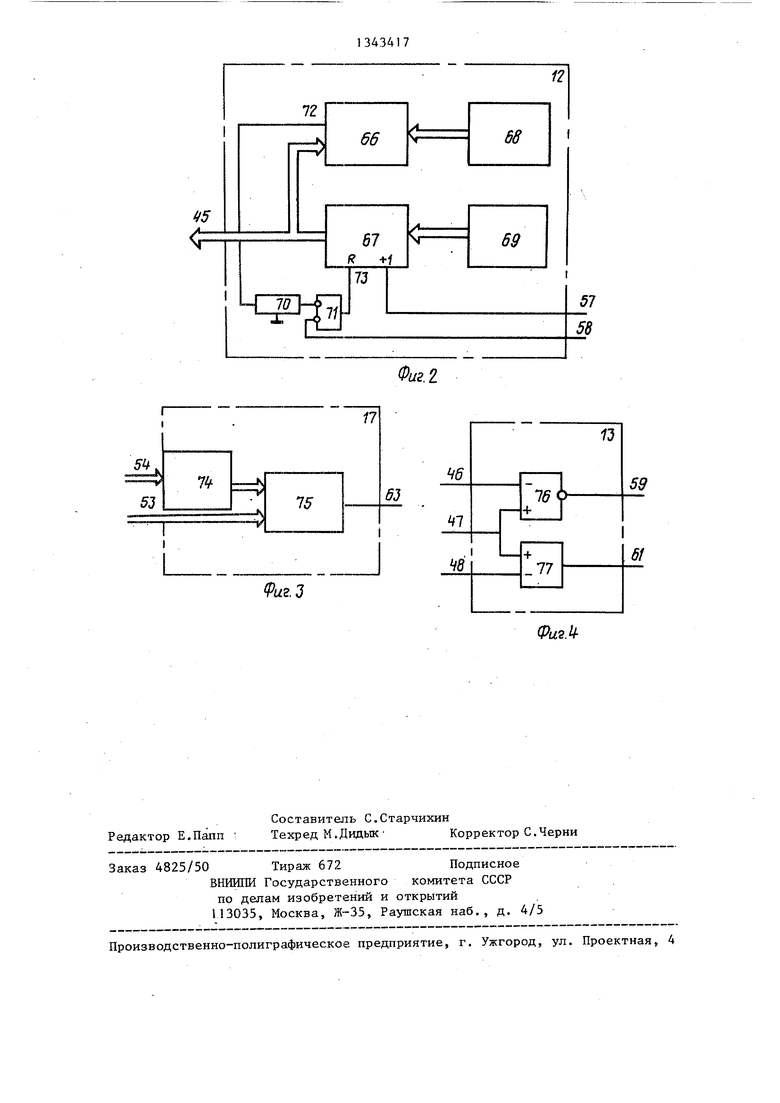

Блок 12 управления (фиг.2) содержи блок 66 сравнения кодов, счетчнк 67, переключатели 68 и 69, элемент 70 задержки и элемент ИЛИ 71. Позицией 72 обозначен выход блока 66,- позицией

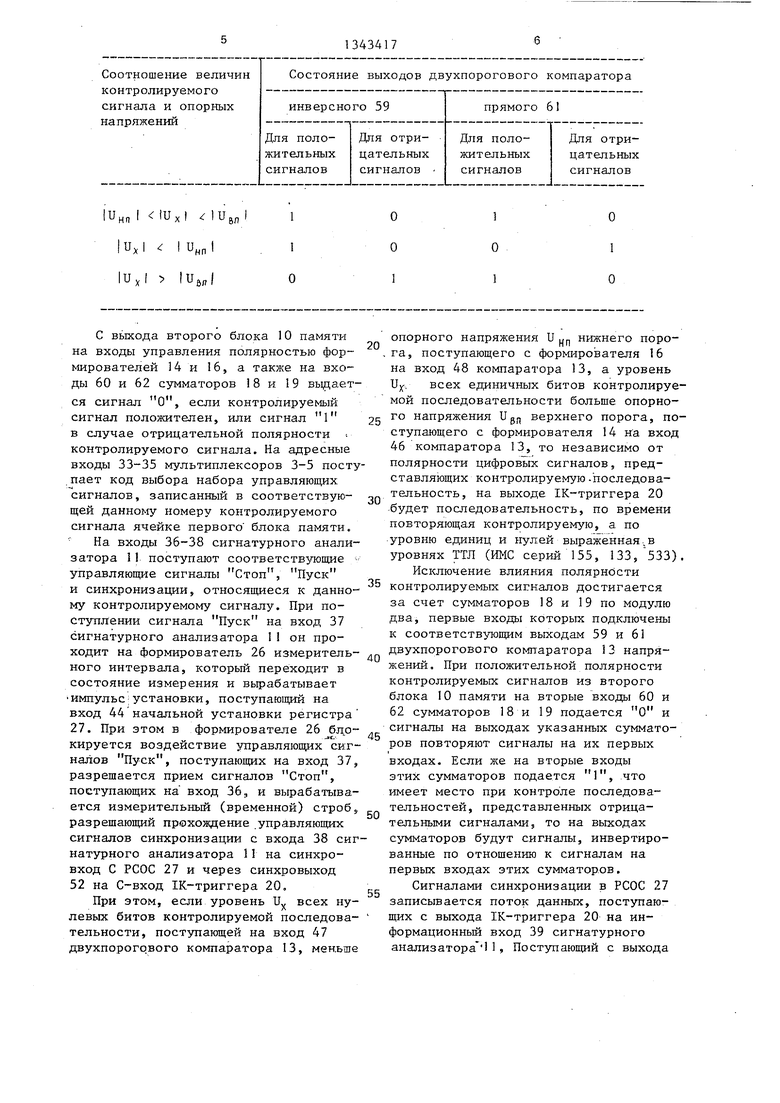

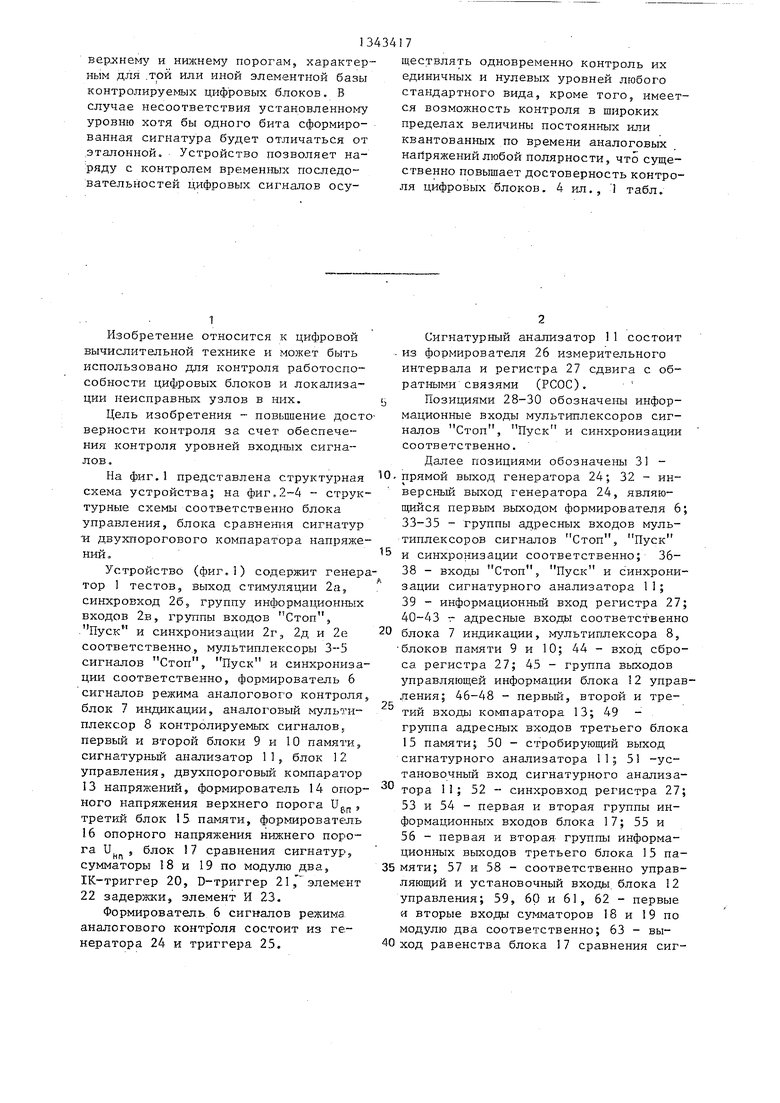

73- вход сброса счетчика 67. Блок 17 сравнения сигнатур (фиг.З)

содержит запоминающее устройство (ЗУ)

74эталонных сигнатур и компаратор

75кодов.

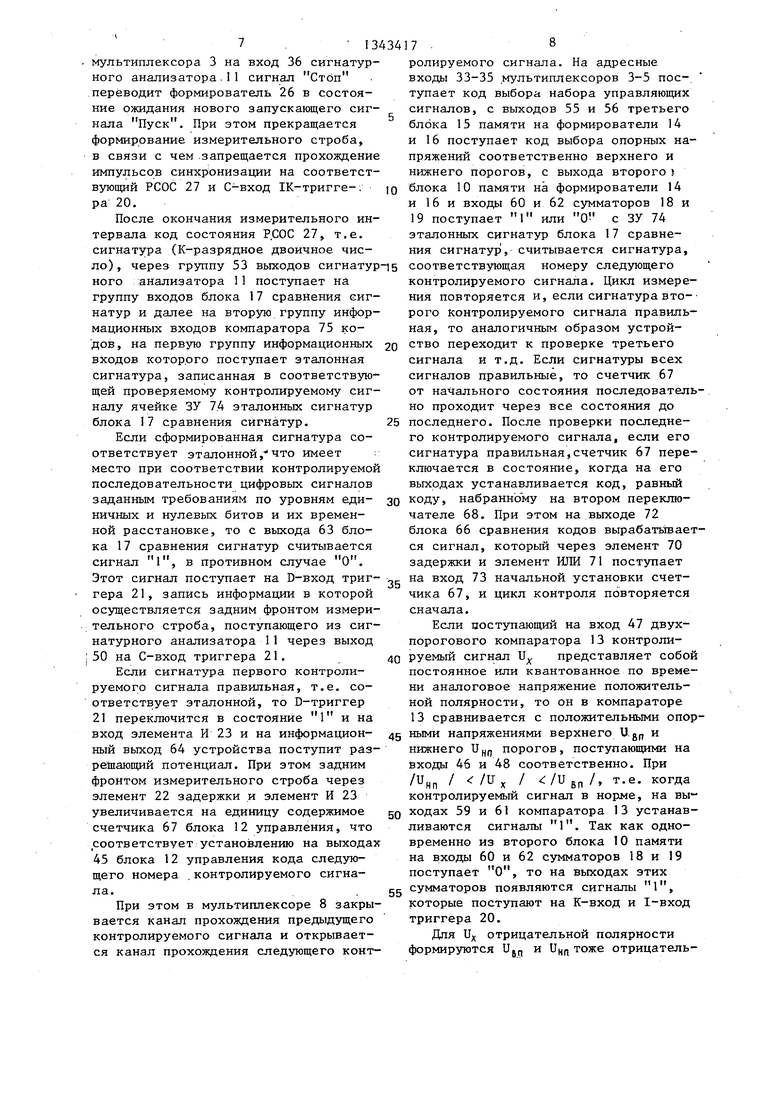

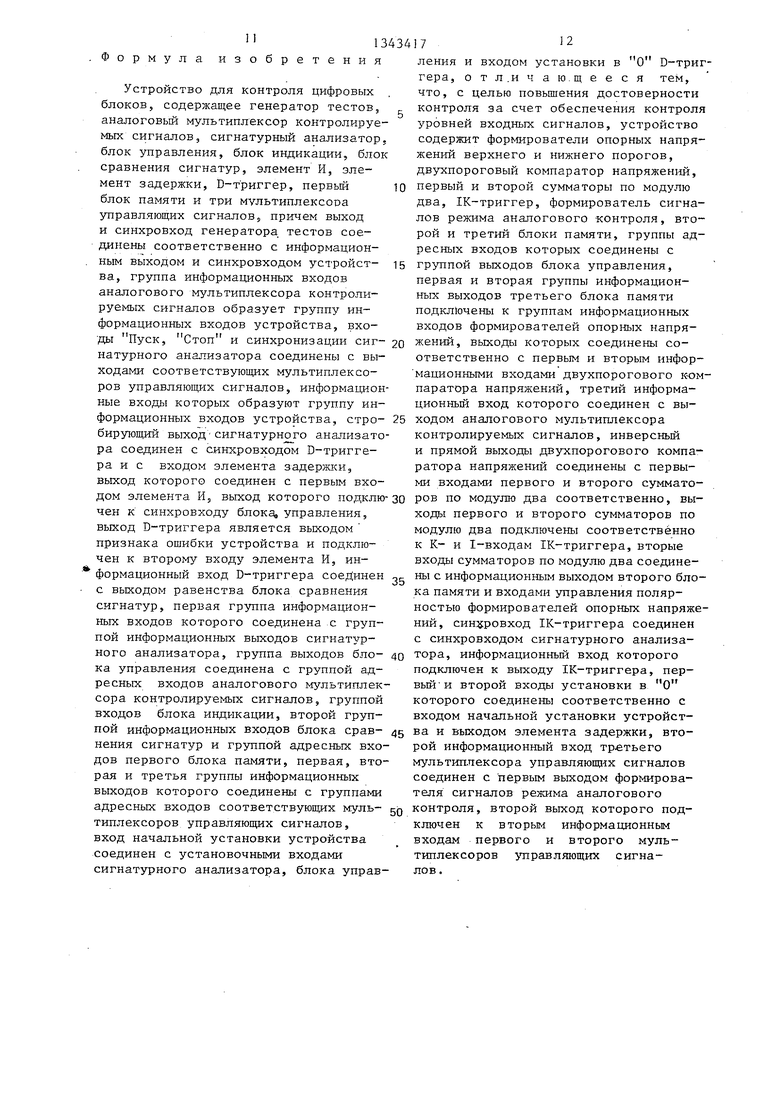

Двухпороговый компаратор 13 (фиг.4) напряжений содержит компаратор 76 верхнего порога и компаратор 77 нижнего порога.

Устройство работает следующим, образом.

Генератор I тестов вырабатывает стимулирующие сигналы, которые через выходы стимуляции 2а устройства поступают в контролируемый цифровой блок. Для обеспечения синхронности стимулирующих сигналов с контролируемыми и управляющими сигналами, формируемыми контролируемым цифровым блоком, из последнего через синхро- вход 26 устройства в генератор 1 поступает опорный синхронизирующий сигнал. При этом на информационные входы 2в устройства и далее на входы п мультиплексора 8 поступают вырабатываемые контролируемым цифровым блО-

ком контролируемые сигналы, представляющие собой определенные временные последовательности цифровых сигналов, постоянные или квантованные по времени аналоговые напряжения. Через входы 2г, 2д, 2е устройства от контролируемого цифрового блока на входы 28-30 мультиплексоров 3-5 поступают наборы управляющих сигналов. Контроль работоспособности или диагностирова- ние цифрового блока осуществляется путем поочередной автоматической проверки поступающих на него временных последовательностей цифровых сигналов с одновременным контролем их единич- ных и нулевых уровней и постоянных или аналоговых напряжений.

В блоке 12 управления переключателем 69 устанавливают номер того контролируемого сигнала, с которого долж-

на начинаться проверка цифрового блока, а переключателем 68 - номер последнего проверяемого контролируемого сигнала.

При подаче импульса на вход 65 начальной установки устройства триггеры 20 и 21 сбрасываются, формирователь 26 измерительного интервала и РСОС 27 сигнатурного анализатора 11 устанавливаются в исходное состояние ожидания запускающего сигнала. Задним фронтом импульса начальной установки на входе 58 блока 12 управления в счетчик 67 записывается начальный код, поступающий с первого переключателя 69 (начального номера контролируемого сигнала). Указанный код с выхода счетчика 67 поступает на группу 45 выходов управляющей информации блока 12 управления и далее на входы 40-43, 49 и 54 соответственно блока 7 индикации, мультиплексора В контролируемых сигналов, первого 9, второго 10 и третьего 15 блоков памяти и блока 17 сравнения сигнатур. На входе 72 блока 66 сравнения кодов при этом сигнал отсутствует. Для четкой работы устройства длительность сигнала начальной установки должна быть больше величины задержки элемента 70 блока

12управления.

При этом в мультиплексоре 8 открыт канал, соответствующий установленному номеру контролируемого сигнала, по которому выбранный для проверки контролируемый сигнал Ujf поступает на вход 47 двухпорогового компаратора

13напряжений. С выходов 55 и 56 третьего блока 15 памяти на формирователи 14 и 16 поступают коды величин опорного напряжения для верхнего и нижнего порогов соответственно. Выбранные опорные напряжения верхнего порога Ug и нижнего порога U подаются соответственно на входы 46 и 48 двухпорогового компаратора 13, осуществляющего сравнения контролируемого сигнала U х опорными напряжениями U р и . В таблице приведено состояние инверсного 59 и прямого 61 выходов компаратора 13 для различных полярностей и соотношений величин

и Uj,, и„,.

lu

нп

lUvl r lU

ВЛ

U, I I и„п

lUgJ

с вьпсода второго блока 10 памяти на входы управления полярностью формирователей 14 и 16, а также на входы 60 и 62 сумматоров 8 и 19 выдается сигнал О, если контролируемый сигнал положителен, или сигнал 1 в случае отрицательной полярности контролируемого сигнала. На адресные входы 33-35 мультиплексоров 3-5 поступает код выбора набора управляющих сигналов, записанный в соответствующей данному номеру контролируемого сигнала ячейке первого блока памяти.

На входы 36-38 сигнатурного анализатора 11 поступают соответствующие управляющие сигналы Стоп, Пуск и синхронизации, относящиеся к данному контролируемому сигналу. При поступлении сигнала Пуск на вход 37 сигнатурного анализатора I он проходит на формирователь 26 измерительного интервала, которьй переходит в состояние измерения и вьфабатывает импульс установки, поступаю1щй на вход 44 начальной установки регистра 27. При этом в формирователе 26 блр- кируется воздействие управляющих сигналов Пуск, поступающих на вход 37, разрешается прием сигналов Стоп, поступающих на вход 36, и вырабатывается измерительный (временной) строб} разрешающий прохождение управляющих сигналов синхронизации с входа 38 сигнатурного анализатора 11 на синхро- вход С РСОС 27 и через синхровыход 52 на С-вход 1К-триггера 20,

При этом, если уровень К всех нулевых битов контролируемой последовательности, поступающей на вход 47 двухпорого.вого компаратора 13, меньше

1

0

1

0

1

0

20

опорного напряжения U нижнего порога, поступающего с формирователя 16 на вход 48 компаратора 13, а уровень

Uv

всех единичных битов контролируе5

0

5

0

5

0

5

мой последовательности больше опорного напряжения Ugj, верхнего порога, поступающего с формирователя 14 на вход 46 компаратора 13, то независимо от полярности цифровых сигналов, представляющих контролируемую-последовательность, на выходе 1К-триггера 20 будет последовательность, по времени повторяющая контролируемую, а по уровню единиц и нулей выраженная,в уровнях ТТЛ (ИМС серий 155, 133, 533).

Исключение влияния полярности контролируемых сигналов достигается за счет сумматоров 18 и 19 по модулю два, первые входы которых подключены к соответствующим выходам 59 и 6 двухпорогового комп аратора 13 напряжений. При положительной полярности контролируемых сигналов из второго блока 10 памяти на вторые входы 60 и 62 сумматоров 18 и 19 подается О и сигналы на выходах указанных сумматоров повторяют сигналы на их первых входах. Если же на вторые входы этих сумматоров подается 1, что имеет место при контроле последовательностей, представленных отрицательными сигналами, то на выходах сумматоров будут сигналы, инвертированные по отношению к сигналам на первых входах этих сумматоров.

Сигналами синхронизации в РСОС 27 записывается поток данных, поступающих с выхода 1К-триггера 20 на информационный вход 39 сигнатурного анализатора 1 Поступающий с выхода

7 - 13 мультиплексора 3 на вход 36 сигнатурного анализатора.11 сигнал Стоп переводит формирователь 26 в состояние ожидания нового запускающего сигнала Пуск. При этом прекращается формирование измерительного строба, в связи с чем запрещается прохождение импульсов синхронизации на соответствующий РСОС 27 и С-вход 1К-тригге-. ра 20.

После окончания измерительного интервала код состояния РСОС 27, т.е. сигнатура (К-разрядное двоичное число), через группу 53 выходов сигнатур ного :анализатора 11 поступает на группу входов блока 17 сравнения сигнатур и далее на вторую группу информационных входов компаратора 75 кодов, на первую группу информационных входов которого поступает эталонная сигнатура, записанная в соответствующей проверяемому контролируемому сигналу ячейке ЗУ 74 эталонных сигнатур блока 17 сравнения сигнатур.

Если сформированная сигнатура соответствует эталонной, что имеет : место при соответствии контролируемой последовательности цифровых сигналов заданным требованиям по уровням еди- ничных и нулевых битов и их временной расстановке, то с выхода 63 блока 17 сравнения сигнатур считывается сигнал 1, в противном случае О. Этот сигнал поступает на D-вход триг-

гера 21, запись информации в которой осуществляется задним фронтом измерительного строба, поступающего из сигнатурного анализатора 11 через выход ;50 на С-вход триггера 21.

Если сигнатура первого контролируемого сигнала правильная, т.е. соответствует эталонной, то D-триггер 21 переключится в состояние 1 и на вход элемента И 23 и на информацион- ный выход 64 устройства поступит раз- рйпающий потенциал. При этом задним фронтом измерительного строба через элемент 22 задержки и элемент И 23 увеличивается на единицу содержимое счетчика 67 блока 12 управления, что соответствует установлению на выходах 45 блока 12 управления кода следующего номера .контролируемого сигнала..

При этом в мультиплексоре 8 закрывается канал прохождения предыдущего контролируемого сигнала и открывается канал прохождения следующего конт17 .8

ролируемого сигнала. На адресные входы 33-35 .мультиплексоров 3-5 пос-. тупает код выбора набора управляющих сигналов, с выходов 55 и 56 третьего блока 15 памяти на формирователи 14 и 16 поступает код выбора опорных напряжений соответственно верхнего и нижнего порогов, с выхода второго 5 блока 10 памяти на формирователи 14 и 16 и входы 60 и 62 сумматоров 18 и 19 поступает 1 или О с ЗУ 74 эталонных сигнатур блока 17 сравнения сигнатур , считывается сигнатура, соответствующая номеру следующего контролируемого сигнала. Цикл измерения повторяется и, если сигнатура второго Контролируемого сигнала правильная, то аналогичньм образом устройство переходит к проверке третьего сигнала и т.д. Если сигнатуры всех сигналов правильные, то счетчик 67 от начального состояния последовательно проходит через все состояния до последнего. После проверки последнего контролируемого сигнала, если его сигнатура правильная,счетчик 67 переключается в состояние, когда на его выходах устанавливается код, равный коду, набранному на втором переключателе 68. При этом на выходе 72 блока 66 сравнения кодов вырабатывается сигнал, которьш через элемент 70 задержки и элемент ИЛИ 71 поступает на вход 73 начальной установки счетчика 67, и цикл контроля повторяется сначала.

Если поступающий на вход 47 двух- порогового компаратора 13 контролируемый сигнал и представляет собой постоянное или квантованное по времени аналоговое напряжение положительной полярности, то он в компараторе 13 сравнивается с положительными опорными напряжениями верхнего Ugp и нижнего и, порогов, поступающими на входы 46 и 48 соответственно. При /и,,.. / /Uv / /и..,/, т.е. когда

нп

контролируемый сигнал в норме, на выходах 59 и 61 компаратора 13 устанавливаются сигналы 1. Так как одновременно из второго блока 10 памяти на входы 60 и 62 сумматоров 18 и 19 поступает О, то на выходах этих сумматоров появляются сигналы 1, которые поступают на К-вход и 1-вход триггера 20.

Для И отрицательной полярности формируются Uj,, и UHJ, тоже отрицательной полярности, в этом случае при

/и / /U , I /Ugn / на выходах 59 и 61 компаратора 13 устанавливаются сигналы О, но за счет того, что при этом на входы 60 и 62 сумматоров 18 и 19 из второго блока 10 памяти выдается 1, на выходах сумматоров 18 и 19 по модулю два и К- и 1-вхо- дах триггера 20 снова устанавливаются сигналы 1.

При контроле постоянных или квантованных по времени аналоговых напряжений в качестве сигналов Пуск, Стоп и синхронизации, управляющих работой сигнатурного анализатора 1I, используются выходные сигналы формирователя 6, которые поступают на один из заранее выбранных входов со- отЁетствующих мультиплексоров 4-5. При этом .управляющие сигналы синхронизации снимаются с инверсного выхода 32 генератора 24, а сигналы Пуск и Стоп - с выхода счетного триггера

на информационном входе 39 сигнатурного анализатора 11 изменится, а сформированные последним сигнатуры 00. . .01 1 для /Ux / /и бл /

или 00...000 для /и X/ /и нп / будут отличаться от эталонной. Таким образом, при проверке любого постоянного или аналогового напряже Q ния результирующая сигнатура может быть только трех видов; 00...010 для /UHH / /и, / /и ел /, 00...011 для /и// / и 00... 000 .для /и у / /и /, анализ которых позво15 ляет получать дополнительную информацию о состоянии контролируемого напряжения.

Если в процессе проверки сигнатура контролируемого сигнала оказывает2Q ся неправильной (отличной ,от эталон- ной),то на выходе 63 блока 17 сравнения сигнатур устанавливается сигнал О, которьш записывается в D-триггер 21, и на вход элемента И

25 формирователя 6.. В результате при 25 23 и на информационный выход 64 уст- проверке любого контролируемого сиг- ройства поступает запрещающий потенциал. Прохождение счетных импульсов через элемент И 23 на счетчик 67 ченала, представленного в виде постоянного или аналогового напряжения любой полярности, формирователем 26 сигнатурного анализатора 11 вырабаты- зо управления запрещено и на выходе 45 вается один и тот же измерительный блока 12 управления остается код норез управляющий вход 57 блока 12

строб, разрешающий прохождение только двух импульсов синхронизации на РСОС 27 и С-вход 1К-триггера 20. Так как при /и „п / ; /и X / /и 8л / на входах К и I триггера 20 стоит 1, то его состояние будет изменяться калодый раз при поступлении на С-вход импульса синхронизации. Таким образом, в течение измерительного интервала на входе 39 сигнатурного аналй-т, затора 1 будет определенная двоичная последовательность, в результате чего на выходе 53 сигнатурного анализатора будет формироваться сигнату- 45 цифровых и цифро-аналоговых блоков ра 00...010, одна и та же /щя всех позволяет за счет осуществления им

наряду с автоматическим контролем временных последовательностей цифровых сигналов методом сигнатурного ана- gQ лиза одновременного контроля их

единичных и нулевых уровней любых стандартных перепадов (ТТЛ, КМОП, ЭСЛ), а также обеспечения им возможности контроля в широких пределах посигналы на выходах 59 и 61 компарато- gg стоянных или квантованных-по времени ра 13 и соответственно на К- и I- аналоговых напряжений любой полярнос- входах триггера 20 будут в противофа- ти, существенно повысить достоверпостоянных или аналоговых U, находящихся в пределах установленных порогов. Указанная сигнатура должна быть записана в качестве эталонной в соот- ветствуюощх ячейках ЗУ 74 блока 17 сравнения сигнатур.

При несоответствии Ux норме, т.е. /Ux / /Ug, / или /и, / /инп /,

зе (О

1 или 1

О). В реность контроля цифровых и цифро-ана- . логовьпс блоков.

зультате вид двоичной последователь43417

ности

о

на информационном входе 39 сигнатурного анализатора 11 изменится, а сформированные последним сигнатуры 00. . .01 1 для /Ux / /и бл /

или 00...000 для /и X/ /и нп / будут отличаться от эталонной. Таким образом, при проверке любого постоянного или аналогового напряже Q ния результирующая сигнатура может быть только трех видов; 00...010 для /UHH / /и, / /и ел /, 00...011 для /и// / и 00... 000 .для /и у / /и /, анализ которых позво15 ляет получать дополнительную информацию о состоянии контролируемого напряжения.

Если в процессе проверки сигнатура контролируемого сигнала оказывает2Q ся неправильной (отличной ,от эталон- ной),то на выходе 63 блока 17 сравнения сигнатур устанавливается сигнал О, которьш записывается в D-триггер 21, и на вход элемента И

управления запрещено и на выходе блока 12 управления остается код

рез управляющий вход 57 блока 12

мера сигнала, который классифицирован как неисправный. Блок 7 индицирует номер этого контролируемого сигнала или непосредственно номер соответствующей отказавшей части контролируемого блока. Таким образом, в случае неработоспособности контрлируемого цифрового блока обеспечивается оперативная информация о месте повреждения, вплоть до номеров отказавших частей (узлов) или микросхем с целью их замены.

Использование предложенного устройства для контроля и диагностирования

ность контроля цифровых и цифро-ана- . логовьпс блоков.

13434

Формула изобретения

Устройство для контроля цифровых блоков, содержащее генератор тестов, аналоговьй мультиплексор контролируемых сигналов, сигнатурный анализатор, блок управления, блок индикации, блок сравнения сигнатур, элемент И, элемент задержки, D-т риггер, первьш ю блок памяти и три мультиплексора управляющих сигналов, причем выход и синхровход генератора тестов соединены соответственно с информационным выходом и синхровходом устройст- 15 на, группа информационных входов аналогового мультиплексора контролируемых сигналов образует группу информационных входов устройства, вхо- ды Пуск, Стоп и синхронизации сиг- 20 натурного анализатора соединены с выходами соответствующих мультиплексоров управляющих сигналов, информационные ВХОД1) которых образуют группу информационных входов устройства, стро- 25 бирующий выход сигнатурншг о анализатора соединен с синхровходом D-тригге- ра и с входом элемента задержки, выход которого соединен с первым входом элемента И, выход которого подклю-зо чек к синхровходу блокав управления, выход D-триггера является выходом признака ошибки устройства и подключен к второму входу элемента И, информационный вход D-триггера соединен с с выходом равенства блока сравнения сигнатур, первая группа информационных входов которого соединена с группой информационных выходов сигнатурного анализатора, группа выходов бло- 40 ка управления соединена с группой адресных входов аналогового мультиплексора контролируемых сигналов, группой входов блока индикации, второй группой информационных входов блока срав- 45 нения сигнатур и группой адресных входов первого блока памяти, первая, вторая и третья группы информационных выходов которого соединены с группами адресных входов соответствуюпщх муль- gQ типлексоров управляющих сигналов, вход начальной установки устройства соединен с установочными входами сигнатурного анализатора, блока управ1712

ления и входом установки в О D-триг гера, отл.ичаю.щееся тем, что, с целью повьппения достоверности контроля за счет обеспечения контроля уровней входных сигналов, устройство содержит формирователи опорных напряжений верхнего и нижнего порогов, двухпороговый компаратор напряжений, первый и второй сумматоры по модулю два, 1К-триггер, формирователь сигналов режима аналогового контроля, второй и третий блоки памяти, группы адресных входов которых соединены с группой выходов блока управления, первая и вторая группы информационных выходов третьего блока памяти подключены к группам информационных входов формирователей onopiuix напряжений, выходы которых соединены соответственно с первым и вторым инфор- мационными входами двухпорогового к-ом паратора напряжений, третий информационный вход которого соединен с выходом аналогового мультиплексора контролируемых сигналов, инверсный и прямой выходы двухпорогового компаратора напряжений соединены с первыми входами первого и второго сумматоров по модулю два соответственно, выходы первого и второго сумматоров по модулю два подключены соответственно к К- и 1-входам 1К-триггера, вторые входы сумматоров по модулю два соединены с информационным выходом второго блока памяти и входами управления полярностью формирователей опорных напряжений, син5 ровход 1К-триггера соединен с синхровходом сигнатурного анализатора, информационный вход которого подключен к выходу 1К-триггера, первый и второй входы установки в О которого соединены соответственно с входом начальной установки устройства и выходом элемента задержки, второй информационный вход третьего мультиплексора управляющих сигналов соединен с первым выходом формирователя сигналов режима аналогового контроля, второй выход которого подключен к вторым информационным входам первого и второго мультиплексоров управляющих сигналов .

Редактор Е.Папп

Составитель С.Старчихин

Техред М.Дидык- Корректор С.Черни

Заказ 4825/50 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фи2Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля радиоэлектронных блоков | 1987 |

|

SU1531100A1 |

| Сигнатурный анализатор | 1987 |

|

SU1429118A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля работоспособности цифровых блоков и локализации неисправных узлов в них. Целью изобретения является повьшение достоверности контроля за счет обеспечения контроля уровней входных сигналов. Устройство содержит генератор 1 тестов, группы 2 входов-выходов, мультиплексоры 3, 4, 5, формирователь 6 сигналов режима аналогового контроля, блок 7 индикации, аналоговый мультиплексор 8 контролируемых сигналов, блоки памяти 9, 10, сигнатурный анализатор 11, блок 12 управления, двух- пороговый компаратор 13 напряжений, формирователь 14 опорного напряжения верхнего порога, блок 15 памяти, формирователь 16 опорного напряжения нижнего порога, блок 17 сравнения сигнатур, сумматоры 18, 19 по модулю два, IК-триггер 20, D-триггер 21, .элемент 22 задержки, элемент И 23. В предлагаемом устройстве при контроле временных последовательностей цифровых сигналов методом сигнатурного анализа одновременно осуществляется контроль уровня цифровых сигналов по Ф (Л

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-07—Публикация

1986-04-07—Подача