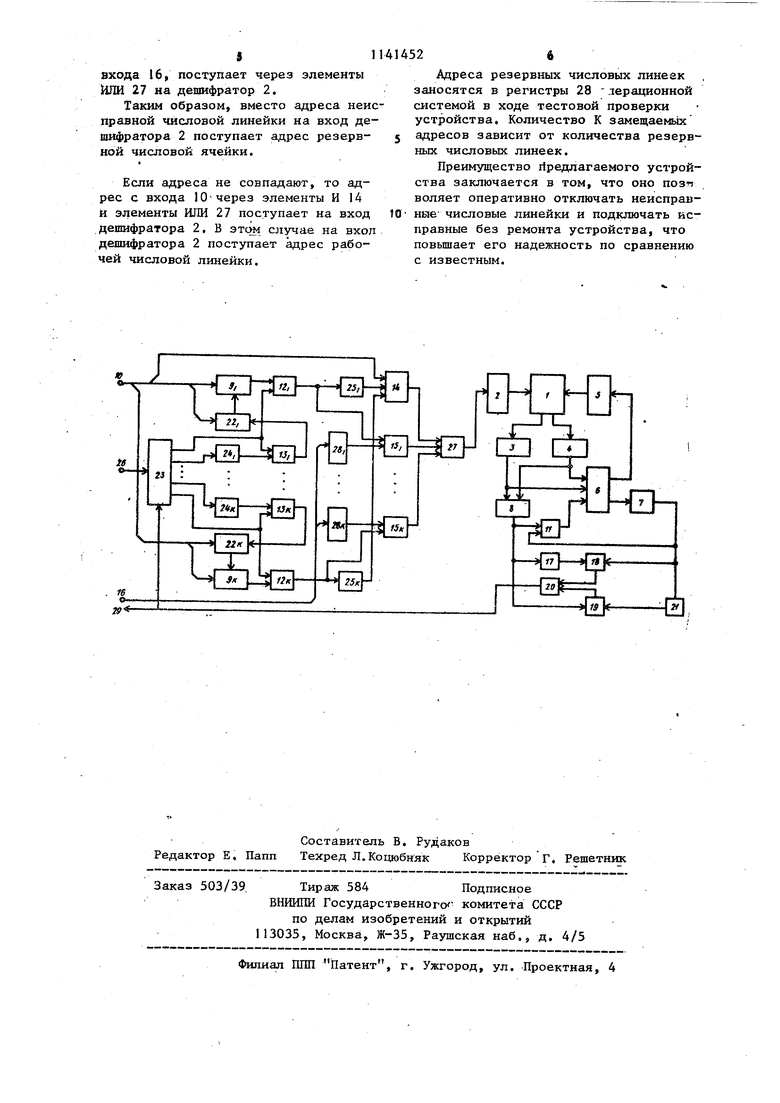

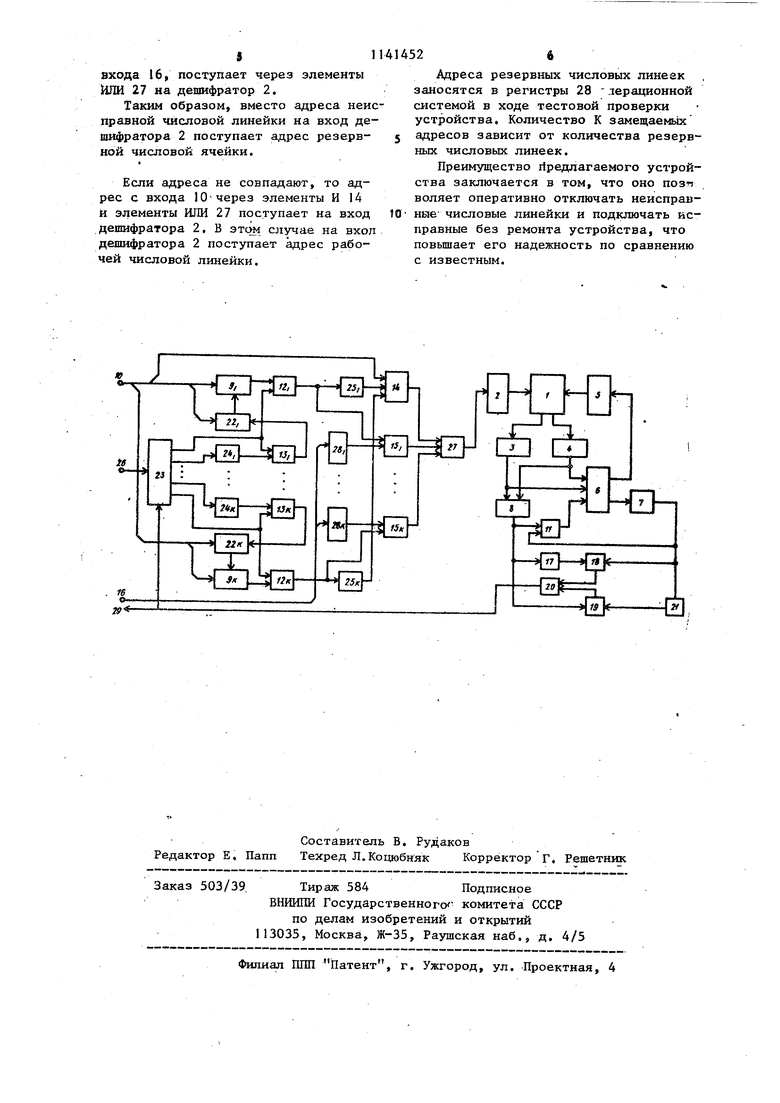

Изобретение относится к вычислительной технике, в частности к оперативньм запоминаннцим устройствам. По основному авт. св. № 894798 известно устройство, содержащее накопитель, входы которого соединены соответственно с выходами формирователей тока записи и дешифратора адреса, входы которого являются входами устройства, первую группу усилителей считывания, входы которых подключенык одним из выходов накопителя, сруппу элементов И, регистр числа, счетные входы которого подключены к выходам элементов И группы, а выходы соответственно к входам формирователей тока записи и блока конт роля, выход которого соединен с первым входом первогоэлемента И и управляющими входами элементов И группы, группу элементов ЭКВИВАЛЕНТНОСТЬ элемент И-НЕ, второй элемент И, элемент ИЛИ, элемент НЕ и вторую группу усилителей считывания, входы которых подключены к другим выходам накопителя, а выходы соединены соответственно с информационными входами регистра числа и входами элементов ЭКВИВАЛЕНТНОСТЬ группы, выходы которых подключены к входу . элемента И-НЕ, первому входу второг элемента И и к информационным входам элементов И группы, выход элемента И-НЕ подключен к второму входу Первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, а выход является контрольным выходом устройства, второй вход второго элемента И соединен с выходом элемента НЕ, вход которого подключен к выходу блока контроля, а также тем, что накопитель выполнен из числовых .линеек на магнитных сердечниках, прошитых числовыми обмотками, разрядными обмотка ми считывания и записи,- причем одноименные разрядные обмотки считывания, проходящие соответственно через рабочие и стабилизирующие магнитные сердечники- накопителя, соединены последовательно н подключены соответственно к выходам накопителя, Cl Недостатком известного устройства является его низкая надежность, например при выходе из строя одной или более числовых линеек устройств из строя. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в оперативное запоминающее уст-. ройство типа 2D с обнаружением и исправлением ошибок введены регистр сдвига, элементы задержки, группы регистров адреса, группа дополнительных элементов ЭКВИВАЛЕНТНОСТЬ, группы дополнительных элементов И с первой по четвертую, группа элементов НЕ и группа элементов ИЛИ, причем перпервые входы дополнительных элементов ЭКВИВАЛЕНТНОСТЬ группы, регистров адреса первой группы и одни из входов Дополнительных элементов И третьей группы являются первым адресным входом устройства, вторьш адресным входом которого являются входы регистров адреса второй группы, а управляющим входом является первый вход регистра сдвига, второй вход которого соединен с выходом элемента ИЛИ, один из выходов регистра . сдвига подключены к первым входам до полнительных элементов И первой группы и дополнительных элементов И второй группы, выходы которых соединены с вторыми входами регистров адреса первой группы, выходы которьк соединены с вторыми входами дополнительных элементов ЭКВИВАЛЕНТНОСТЬ группы, выходы которых соединены с вторыми входами дополнительных элементов И первой группы, выходы которых подключены к входам элементов НЕ группы, выходы которых соединены с другими входами дополнительных элементов И третьей группы, одни из входов дополнительных элементов И четвертой группы подключены к выходам дополнительных элементов И первой груп ;1Ы, другие - к выходам регистров адреса, второй группы, выходы дополнительных элементов И третьей и четвертой групп через элементы ИЛИ группы подключены к входам дешифратора адреса, вторые входы дополнительных элементов И второй группы через элементы задержки соединены с другими выходами регистра сдвига. На чертеже показана структурная схема предлагаемсГго устройства. Устройство содержит накопитель 1, дешифратор 2 адреса, первую 3 и вторую 4 группы усилителей считывания, формирователи. 5 тока записи, регистр 6 числа, блок 7 контроля, группу элементов ЭКВИВАЛЕНТНОСТЬ 8, 3 группу дополнительных элементов ЭКВИВАЛЕНТНОСТЬ j, первый вход 10, группу элементов И 1 1., первую группу дополнительных элементов И , вторую группу дополнительных элементов И , третью группу дополнительных элементов И , четвертую группу дополнительных элементов И ,, второй адресный вход 16, элемент И-НЕ 17, первый 18 и второй 19 элементы И, элемент ИЛИ 20, элемент НЕ 21, первую группу регистров адреса, регистр 23 сдвига, элементы задержки группу элементов НЕ 25 -2Ъ, управляющий вход 26, группу элементов ИЛИ 27, вторую группу регистров (j адреса, выход 29. Устройство работает следующим образом. Адрес, по которому необходимо произвести считывание числа, поступает с входа 10 через элементы-И 14 и элементы ИЛИ 27 на дешифратор 2, дешифруется, в результате чего выбирается числовая линейка, соответствующая ячейке памяти накопителя 1, из которой необходимо считать информацию. Сигналы с накопителя 1, усиленные усилителями 3 и 4, поступают одновременно на информационные входы регистра 6 и на входы элементов ЭКВИВАЛЕНТНОСТЬ 8. Неисправность, возникающая в одно или нескольких разрядах накопителя 1 обнаруживается при считывании информации. Факт ее возникновения регистр руется блоком 7 контроля, а место элементами ЭКВИВАЛЕНТНОСТЬ 8. При наличии управляющего сигнала на выхо де блока 7 контроля производится исправление всех ошибок путем инвертирования тех разрядов регистра 6, в которых зафиксирована ошибка. При возникновении ошибки сигнал с блока 7 поступает на первый вход пер вого элемента И 18. Если на выходах элементов ЭКВИВАЛЕНТНОСТЬ 8 сигнала нет, то на выходе элемента И-НЕ 17 возникает сигнал, который поступает на второй вход первого элемента И 18 с выхода которого он поступает на первый вход элемента ИЛИ 20 и на выходе 29 появляется сигнал ошибки, св детельствующий о том, что обнаружена неисправимая ошибка. Аналогичный сигнал выдается и в случае, если блок 7 контроля ошибки 524 не обнаружит. Тогда на выходе элемента НЕ 21 появляется сигнал, поступающий на второй вход второго элемента И 19, если на выходах элементов ЭКВИВАЛЕНТНОСТЬ 8 появляется сигнал, то он проходит через первый вход второго элемента И i 9 и с его выхода поступает на второй вход элемента . ; ИЛИ 20. Исходное состояние регистра 23 сдвига - нулевое состояние. По сигналам ошибки с выхода элемента ИЛИ 20 nepBbiii триггер регистра 23, а затем и последующий (по числу ошибок) устанавливаются в единичное состояние (триггеры не показаны), что означает подключение соотвеп ствующих резервных числовых линеек и отключение неисправных, при считывании информации из которых обнаружены ошибки. Рассмотрим процесс замены адреса с числовой линейки. После установления какого-либо триггера регистра 23 сдвига, например первого,в единичное состояние, сигнал с единичного выхода триггера проходит через элемент И 13 на вход регистра 22 адреса и разрешает запись в него адреса неисправной числовой линейки с вхаДа 10 устройства и одновременно поступает на вход элемента И 12 , а сигнал с нулевого выхода первого триггера регистра 23 сдвига, проходя через элемент 24 задержки (с временем задержки, равным времени записи информации в регистр 22)и элемент И 13., запрещает запись информации в регистр 22 адреса. Таким образом, адрес неисправной числовой ячейки оказывается записанным в регистр 22 адреса. При поступлении на вход 10 адреса числа, хранящегося в накопителе 1, этот адрес сравнивается в соответствующих элементах ЭКВИВАЛЕНТНОСТЬ 9 с адресами, записанными в регистрах 22 адреса. При совпадении поступившего адреса, например, с адресом в регистре 22 на выходе К-го элемента И 12| имеется сигнал 1, тогда на выходе К-го элемента НЕ 25 имеется О, адрес с входа 10 не попадает а дешифратор 2. В то же время сигнал 1 с выхода К-го элемента И 12, перой группы поступает на элементы 15| и адрес резервной числовой инейки с регистра 28, куда он долен быть заблаговременно записан с 5 входа 16, поступает через элементы ИЛИ 27 на дешифратор 2. Таким образом, вместо адреса неи правной числовой линейки на вход де шифратора 2 поступает адрес резервной числовой ячейки. Если адреса не совпадают, то адрес с входа 10через элементы И 14 и элементы ИЛИ 27 поступает на вход дешифратора 2, В этсж случае на вхо дешифратора 2 поступает адрес рабочей числовой линейки. 26 Адреса резервных числовых линеек заносятся в регистры 28 лерационной системой в ходе тестовой проверки устройства. Количество К замещаемых адресов зависит от количества резервньк числовьк линеек. Преимущество йредлагаемого устройства заключается в том, что оно позп воляет оперативно отключать неисправные числовые линейки и подключать исправные без ремонта устройства, что повьш1ает его надежность по сравнению с известным.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство типа 2Д с обнаружением и исправлением ошибок | 1980 |

|

SU894798A1 |

| Оперативное запоминающее устройство типа @ с обнаружением и исправлением ошибок | 1981 |

|

SU999114A1 |

| Многоканальный интерполяционный измеритель временных интервалов | 1982 |

|

SU1027695A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

ОПЕРАТИВНОЕ: ЗАПОМИНАМЦЕЕ УСТРОЙСТВО ТИПА 2D С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК по авт. св. № 894798, отличающееся тем, что, с целью повышения надежности устройства, в него введены регистр сдвига, элементы задержки, группы регистров адреса, группа дополнительных элементов ЭКВИВАЛЕНТНОСТЬ, группы дополнительных элементов И с первой по четвертую, группа элементов НЕ и группа .элементов ИЛИ, причем первые входы дополнительных элементов ЭКВИВАЛЕНТНОСТЬ труппы, регистров адреса первой группы и одни из входов дополнительных элементов И третьей.группы являются первым адресным входом устройства, вторым адресным входом которого являются входы регистров адреса второй группы, а управляющим входом является первый вход регистра сдвига, второй вход которого соединен с выходом элемента ИЛИ, одни из выходов регистра сдвига подключены к первым входам дополнительных .элементов И первой группы и дополнительных элементов И второй группы, выходы которых соединены с. вторыми входами регистров адреса первой группы, выходы которых соединены с вторыми входами дополнительных элементов ЭКВИВАЖНТНОСТЬ группы, выходы которых соединены с вторыми входами дополнительных элементов И первой группы, выходы которых подключены к входам элементов НЕ группы, выходы которых соединены с другими входами дополнительных элементов И третьей группы, одни из входов дополнительных элементов И четвертой группы подключены к выходам дополнительных элементов И первой группы, другие - к выходам регистров адреса второй группы, выходы до.полнительных элементов И третьей и 4 четвертой групп через элементы ИЛИ группы подключены к входам дешифра1 тора адреса, вторые входы дополнительных элементов И второй группы через элементы задержки соединены с другими выходами регистра сдвига.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оперативное запоминающее устройство типа 2Д с обнаружением и исправлением ошибок | 1980 |

|

SU894798A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1985-02-23—Публикация

1983-11-16—Подача