(54) ОПЕРАТИВНОЕ ЗАПОМШ1АЮЩЕЕ УСТРОЙСТВО ТИПА 2Д С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство типа 2 @ с обнаружением и исправлением ошибок | 1983 |

|

SU1141452A2 |

| Оперативное запоминающее устройство типа @ с обнаружением и исправлением ошибок | 1981 |

|

SU999114A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249591A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1984 |

|

SU1215139A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037342A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

Изобретение относится к эапоминаюиип устройствам.

Известно оперативное запоминающее устройство, содержащее накопитель, блоки выбора ащ1еса, усилители считывания, блоки контроля 11.

. Недостатками устройства являются большие аппаратурные затраты и низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является оперативное запоминающее устройство с обнаружением и исправлением ошибок, содержащее накопитель, входы которого соединены соответственно с выходами дешифратора адреса и формирователей тока записи, первую группу усилителей считьюания, регистр числа, счетные входы которого подключены к выходам группы элементов И, а выходы - к входам фор1угарователей тока записи, блок контроля, выход которого подключен к первому входу первого элеиданта И 21.

Недостатками устройства являются гшзкое быстродействие вследствие того, что для исправления ошибки требуется проводить считывание записанной в предыдущем цикле .инфор мащ1и, а также невозможность исправлять ошибки, если вьтолняется толысо считьгоаниеиз накопителя.

Цель изобретения - п(шыщение быстродействия устройства.

Поставленная цель достигается тем, что в оперативное запомишющее устройство типа 2 Д с обнаружением и исправлением ошибок, содержащее накопитель, входы которого соедиtoнены соответственно с выходдмн формирователей тока записи и дешифратора адреса, вхо ды которого являются входами устройства, первую группу ушлителей считывания, входы которых подключены к одним из выходов наISкопителя, группу элементов И, регистр числа, счетные входы которого подключены к выходам злементов И группы, а выходы - соответственно ко входам формирователей тока

записи и блоки контроля, выход которого €О20

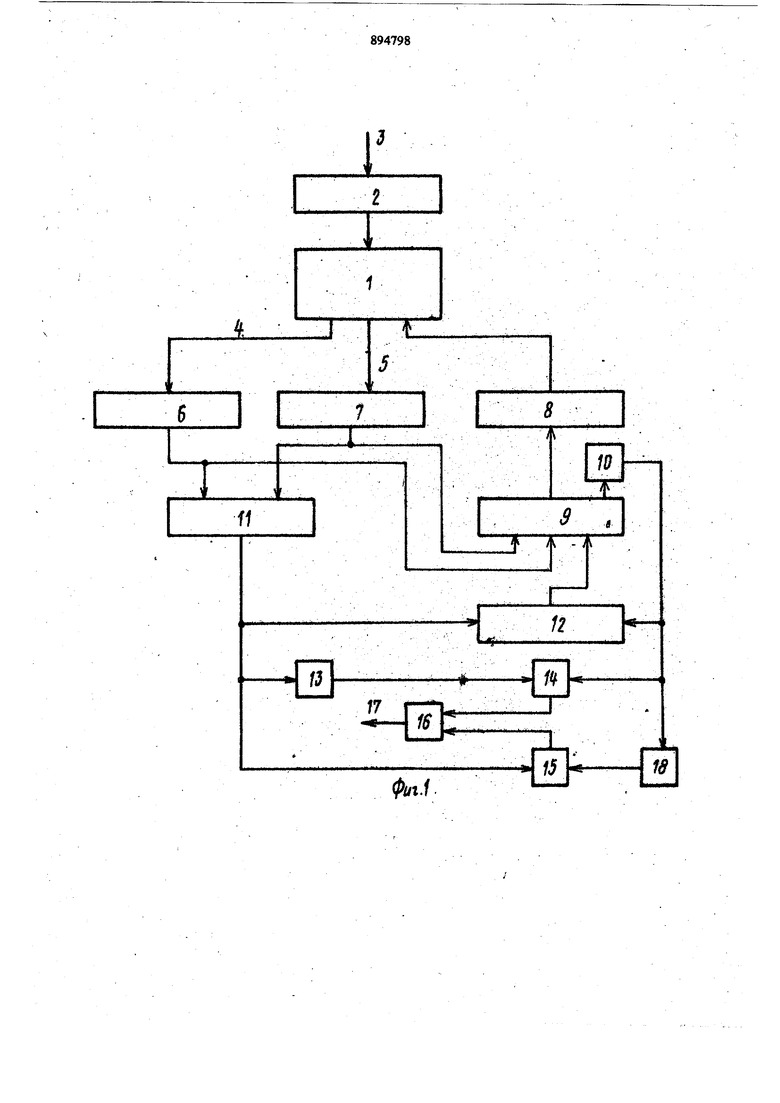

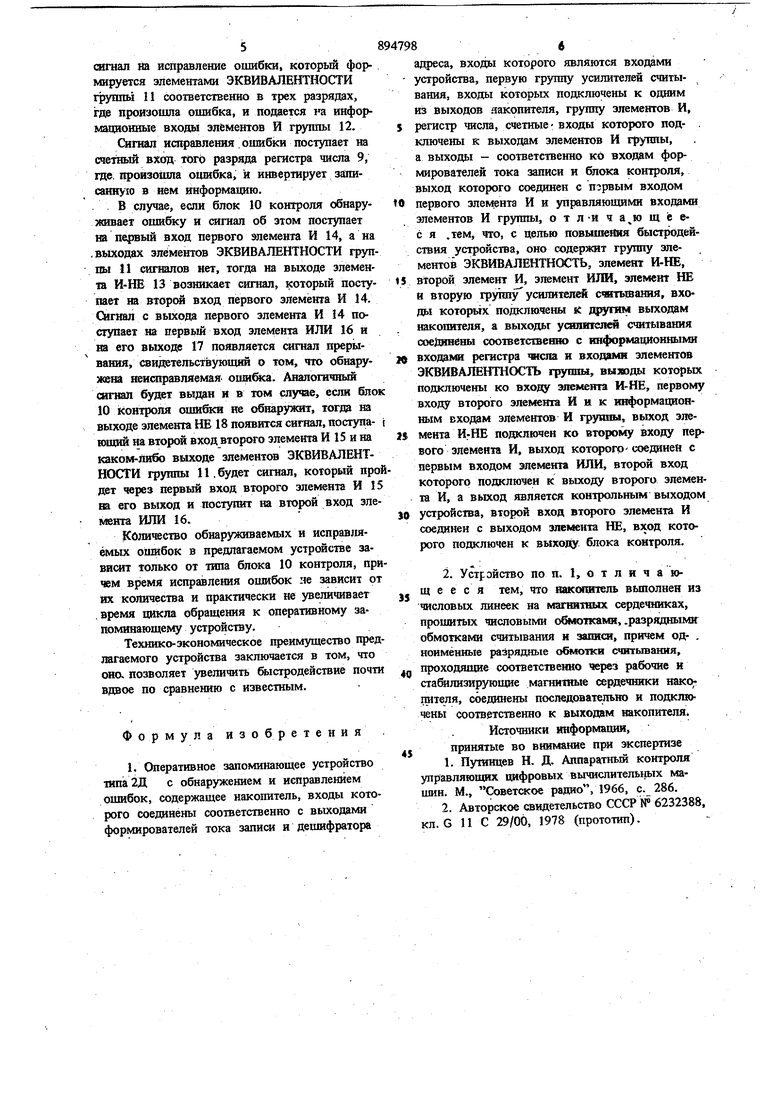

;единец с первым входом первого элемента Н н управляющими входами злементо1 И. группы, введены грутша элементов ЭКВИВАЛЕНТНОСТЬ, элемент И-НЕ; второй элемент И, элб мент ИЛИ, элемент НЕ и вторая группа усилителей считьюания, входы которых подклю ны к другим выходам накопителя, а выходы соединены соответственно с информашюнными входами регистра числа и входами элементов ЭКВИВАЛЕНТНОСТЬ группы, выходы которых подключены ко входу элемента И-НЕ первому входу второго элемента И и к информационным входам элементов И группы, выход элемента И-НЕ подключен ко второму входу первого .элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, а выход является контрольным выходом устройства, второй вход второго элемента И соединен с выходом элемента НЕ, вход которого подключен к выходу блока контроля. При этом накопитель делесообразно вьшол нить-из числовых линеек на магнитных сердеч никах, прошитых числовыми обмотками, разрядными обмотками считьшания и записи, при чем одноименные разрядные обмотки счшъша1ШЯ, проходящие соответственно через рабочие и стабилизирующие магнитные сердечники чисйовых линеек накопителя, соединены последовательно и подключены соотвйственно к выходам накопителя. , На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - принципиальная схема, числовой линейки накопителя Устройство содер жт накопитель 1, дешифратор 2 адреса со входами 3. Устройство содержит пе|шую 6 и вторую 7 группы усилителей, формирователи 8 тока записи, регистр 9 числа, блок 10 контроля, группу элементов ЭКВИВАЛЕНТНОСТЬ 11, группу элементов И 12, элемент И-НЕ 13, первый 14 и второй 15 элементы И, элемент ИЛИ 16 с выходом 17 и элемент НЕ 18, Входа накопителя 1 соединены соответственно с выходами формирователей 8 тока записи и дешифратора 2 адреса, входы 3 которого являются входами устройства. Входы уш лителей первой 6 и второй 7 групп подключены соответственно к одним 4 и другим 5 выходам накопителя 1. Счетные входы регистра 9 числа соединены с выходами элементов И группы 12, а выходы - соответственно со входами формирователей 8 тока записи и блока 10 контроля, выход которого подключен к Первому входу первого Элемента И 14 и управляющим входам элементов И группы 12, Выходы усилителей считьшания первой 6 и второй 7 групп соединены соответсгаенно с ин формационными входами регистра 9 числа и входами элементов ЭКВИВАЛЕНТНОСТЬ группы II, выходы которых подключены .ко входу элемента И-НЕ 13, первому входу второго 84 элемента И 15 и информационньгм входам элементов И группы 12. Выход элемента И-НЕ 13 подключен ко второму входу первого элемента И 14, выход которого соединен с первым входом элемента ИЛИ 16, второй вход которого подключен к выходу второго элемента И 15, а вь1хрд 17 является контрольным выходом устройства. Второй вход второго элемента И, 15 соединен с выходом элемента НЕ 18, вход которого подключен к выходу бло- ка 10 контроля. При этом накопитель 1 вьшолнен из числовых линеек на магнитных сердечниках 19 и 20, прошитых числовыми обмотками 21, разрядными обмотками 22 считывания и записи 23 причем одноименные разрядные обмотки 22 считьгоания, проходящие соответственно через рабочие 19 и стабилизирующие 20 магнитные сердечники числовых линеек накопителя 1, соединены последовательно и подключены соответственно к выходам 4 и 5 накопитейя 1. БЛОК 10 контроля может быть построен любым из известных методов,; например, п{ж контроле по модулю два блок 10 контроля будет фиксировать факт ошибки в нечетном числе разрядов,. Устройство работает следующим образом. Неисправность, воз1шкшая в одном или нескольких разрядах накопителя 1 обнаруживается при считьшании информации, причем факт ее возникновения регистрируется блоком 10 контроля, а место - элементалщ ЭКВИВАЛЕНТНОСТИ группы 11, При наличии управляющего сигнала на выходе блока контроля производится исправление всех опшбок путем инвертирования тех разрядов регистра числа, в которых была зафиксирована ошибка. А/фес, по которому необходимо произвести считывание числа, дешифрируется дешифратором 2, в результате чего выбирается числовая линейка, соответствующая ячейке памяти накопителя 1, из которой необходимо считать информацию. В разрядных обмотках 22 считывания рабочих сердечников 19 и стабилизирующих сердечников 20 соответственно индуктируются ЭДС, соответствующие кодам 1 и О. Эти шгналы, усиленные соответственно усилителями считьшания первой 6 и ыорой 7 групп поступают одновременно на информационные входы соответствующих разрядов регистра 9 и на входы элементов ЭКВИВАЛЕНТНОСТИ группы 11,: Процесс исправления ошибок при считыJeaiDffl информации осуществляется следующим образом. При возникновении ошибки на выходе Йтока 10 контроля появляется сигнал сбоя, который поступает на управляющие входы элементов И группы 12, что позволяет выдать шгнал на исправление ошибю, который формируется элементами ЭКВИВАЛЕНТНОСТИ rpjrnnbi 11 соответственно в трех разрядах, где произошла оишбка, и подается на инфорилациоиные входы злЁментов И гругаты 12. Сигнал исправления; ошибки поступает на счетный вход того разряда регистра чиста 9, где. произошла ошибка, и инвертирует записанную в нем информацию. В случае, если блок 10 контроля обнаруживает ошибку и сигнал об зтом поступает на первый вход первого элемента И 14, а на .выходах элементов ЭКВИВАЛЕНТНОСТИ групШ|1 11 сигвЕшов нет, тогда на выходе элемента И-ГО 13 возникает сигнал, который поступает на вторс вход первого элемента И 14. Сигнал с выхода первого элемента И 14 поступает на первьш вход элемента ИЛИ 16 и на его выходе 17 появляется сигнал прерывания, овидетельствуюший о том, что обнаружена ненсправляемая- ошибка. Аналопшшй Сигнал будет выдан и в том случае, если бло Ю Контроля ошибки не обнаружит, тогда на выходе элемента НЕ 18 появится сигнал, поступающий 1ю второй вход второго элемента И 15 и на каком-либо выходе элементов ЭКВИВАЛЕНТНОСТИ группы И,будет сигнал, который про дет через первый вход второго элемента И 1 на его выход и поступит на второй вход эле мента ИЛИ 6. Количество обнаруживаемых и исправзмёмых ошибок в предлагаемом устройстве зависит только от типа блока 10 контроля, при чем время исправления ошибок не зависит от их количества и практически не увеличивает .время цикла обращения к оперативному запоминаюшему устройству. Технико-экономическое преимущество пред лагаемого устройства заключается в том, что она позволяет увеличить & 1стродействие почти вдвое по сравнению с известным. Формула изобретения 1. Оперативное запоминающее устройство типа2Д с обнаружением и исправлением ошибок, содержащее накопитель, входы которого соединены соответственно с выходами формирователей тока записи и дешифратора адреса, входы которого являются входами устройства, первую группу усилителей считывания, входы которых подключены к одним из выходов .чакопителя, группу элементов И, регистр числа, счетные- входы которого под- . ключены к выходам элементов И группы, а выходы - соответственно ко входам формирователей тока записи и блока контроля, выход которого соединен с порвым входом первого элемента И и управляющими входами элементов И группы, отл-ича ющеес я .тем, что, с целью повышения быстродействия устройства, оно содержит группу элементов ЭКВИВАЛЕНТНОСТЬ, элемент И-НЕ, второй элемент И, элемент ИЛИ, элемент 1Ш и вторую группуусилителей считьшания, входы которьтх подключены к другим выходам иакошпеля, а выходы усаяшслей считывания соединены соответсгаенно с информациоиными входами регистра шспа и входами элементов ЭКВИВАЛЕНТНОСТЬ группы, выходы которых подключены ко входу элеменга И-НЕ, первому входу второго элемента И и к информационным входам элементов И грзпшы, выход элемента И:НЕ подключен ко второму входу первого элемента И, выход которого- соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, а выход является контрольным выходом устройства, второй вход BTqporo элемента И соединен с выходом элемента НЕ, вход которого подключен к выходу блока контроля. 2. Устройство по п. 1, о т л и ч а ющ е е с я тем, что накопитель выполнен из числовых линеек на магнитных сердечниках, прошитых числовыми обмотками, .разрядными обмотками считывания и записи, причем од- . ноимёнш 1е разрядные обмотки считывания. проходящие соответственно через рабочие и стаа1лнзирующие магнишые сердечники накопителя, соединены последовательно и подключены соответственно к выходам накопителя. Источники информашш, принятые во внимание при экспертизе 1.Путинцев Н. Д. Аппаратный контроля управляющих цифровых вычислителышх мащин. М., Советосое радио, 1966, с. 286. 2.Авторское свидетельство СССР № 6232388, кл. G 11 С 29/00, 1978 (прототип).

Puz.Z

Авторы

Даты

1981-12-30—Публикация

1980-04-04—Подача