Изобретение относится к вычислительной технике и предназначено для управления обменом информацией в вычислительных системах, которые могут быть использованы для управления технологическими процессами, автоматическими линиями, робототехническими комплексами.

Целью изобретения является повьапе- ние быстродействия и упрощение устройства.

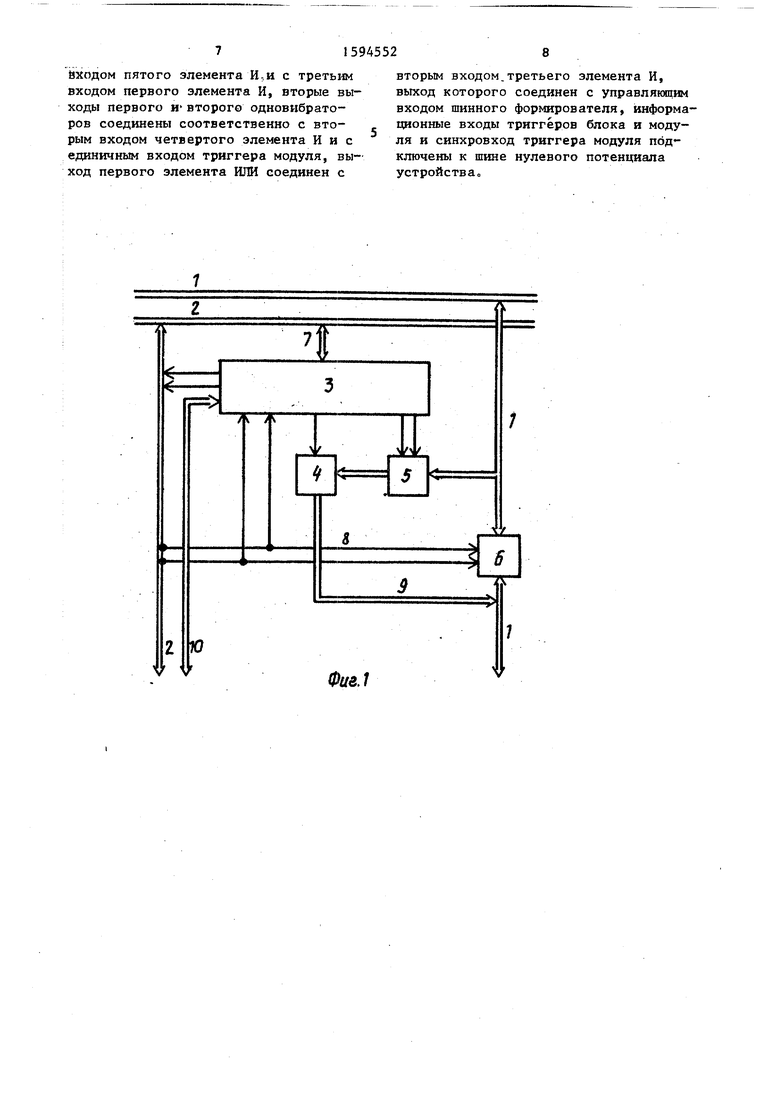

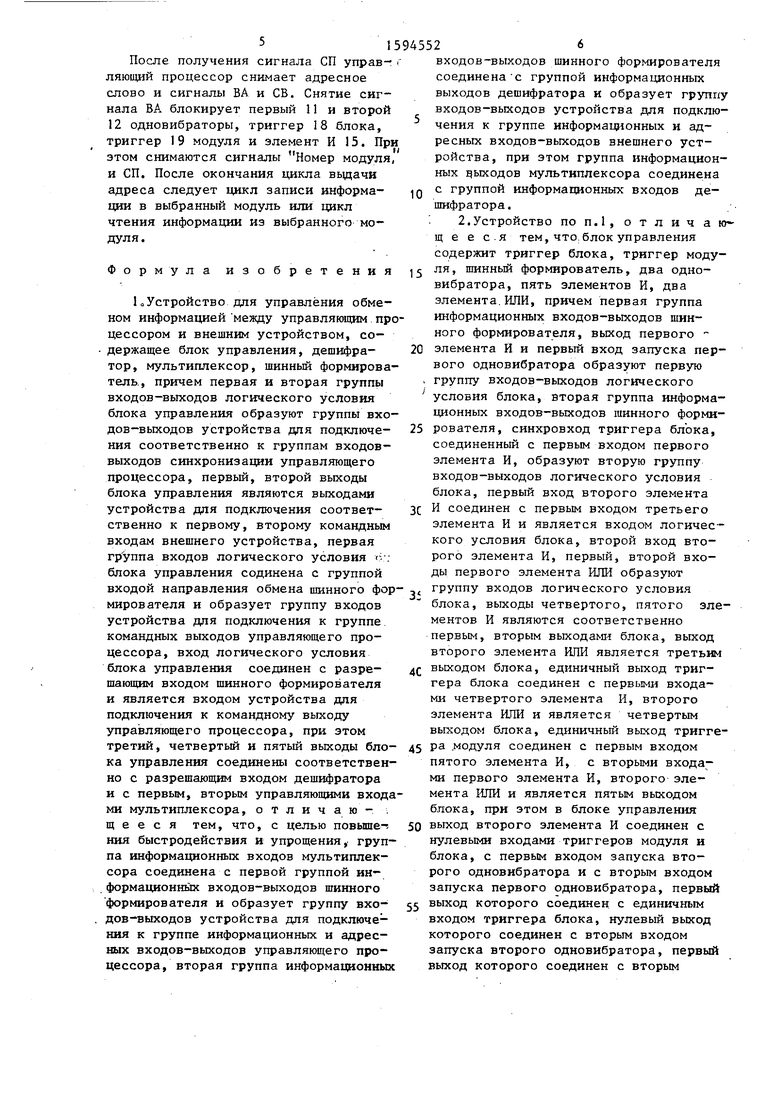

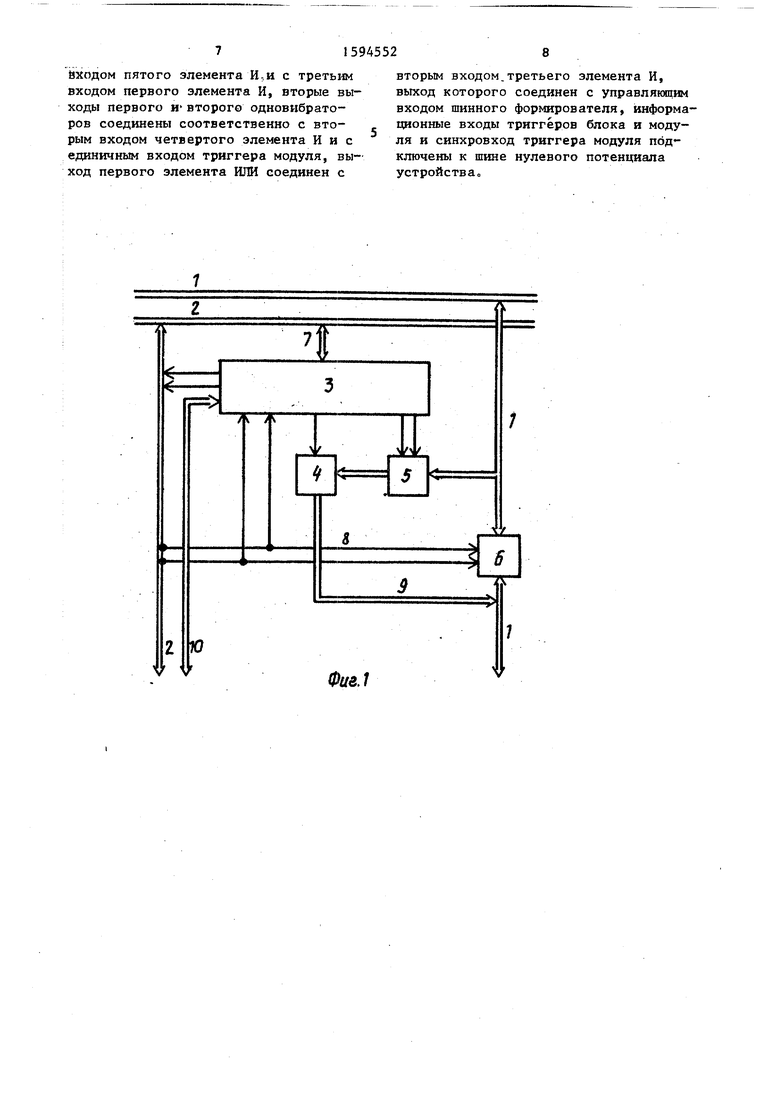

На фиг. представлена структурная схема устройства сопряжения; на фиг.2 - структурная схема блока управления обмена.

Устройство содержит (фиг.1) вхо- ды-выходы 1 данных адреса, входы-выходы 2 управления, блок 3 управления, дешифратор 4, мультиплексор 5, шинный формирователь 6, входы и выходы 7-10.

Блок управления 3 обмена (фиг.2) содержит одновибраторы и J2, элементы И 13-17, триггер 18 блока, триггер 19 модуля, элементы ИЛИ 20- 21 и шинный формирователь 22.

Устройство для сопряжения работает следующим образом.

Обмен информацией между процессором (не показан) и внешними устройствами, в качестве которых могут быть блоки ввода-вьшода (не показаны), . происходит в асинхронном режиме о Цикл обмена информацией начинается с вьздачи адреса.

Процессор вьщает сигнал Выдача адреса (ВА) и сигнал Ввод-вьшод (ВВ), указывающий на то, что происходит обмен информацией между процессором и блоками ввода-вьшода, а на входы-выходы 1. данных адреса - адел

4;;:

сл

Сд

ю

pei-H(ie. слово, которое поступает на вход мультиплексора 5.

Сигнал ВА поступает на вход элемента И 16 блока 3 управления, а на другой вход подается сигнал ВВ. Выходной сигнал элемента И 16 снимает блокировку первого 11, второго 12 одновибраторов, триггера 18 блока и триггера 19 модуля.JQ

Запуск первого 11 одновибратора осуществляется сигналом Синхронизация ньщачи (СВ), который сопровождает адресное слово, вьщаваемое управляющим процессором.15

На прямом выходе первого 11 одно- вибратора появляется импульс, который своим передним фронтом устанавливает триггер 18 блока в состояние 1. Сигнал с прямого выхода триггера 18 20 блока поступает на входы элемента ИЛИ 20, элемента И 13 и на первый : вход мультиплексора 5, на группе входов которого уже присутствует гщ- ресное слово.25

По сигналу Номер блока мультиплексор 5 выбирает из адресного слова с шестого по девятый разряды, соответствующие номеру выбираемого

ляющим процессором и выбранным блоком ввода-вывода. После этого в выбранном блоке ввода-вывода формируется сигнал Синхронизация приема (СП), который поступает на вход триггера 18 блока и переводит его в исходное состояние. При этом снимается блокировка с мультиплексора 5, блокируется элемент И 13, снимается сигнал Номер блока, а следовательно, и сигнал СП. Выбор блока ввода-вывода осуществлен.

Сигнал с инверсного выхода тригге ра 18 блока запускает второй одно- вибратор 12, импульс на прямом выходе которого своим передним фронтом устанавливает триггер 19 модуля в состояние 1. Сигнал с выхода триггера 19 модуля поступает на входы элементов ИЛИ 20, И 14 и 15 и на вт,орой вход мультиплексора 5, который выбирает из адресного слова с третьего по пятый разряды, соответ-. ствующие номеру выбираемого модуля Как и в цикле выбора номера блока, сигнал с выхода элемента ИЛИ 20 разрешает дешифрацию информации, посту- пивщей на адресные входы дешифрато-

блока. Выбранная информация с выходов JQ ра 4. С выхода дешифратора 4 сигнал

35

40

мультиплексора 5 поступает на входы дешифратора 4, на управляющий вход которого поступает сигнал с выхода элемента ИЛИ 20, разрешая дешифра щю информации. С выхода дешифратора 4 сигнал, несущий информацию о номере выбранного блока, поступает на соответствующий номеру блок ввода-вьшода. Блоки ввода-вьюода подключаются таким образом, что каждый блок, имегощий определенный номер от О до 15, подключен к соответствующим выходам дешифратора 4, имеюшцм такой же номер. Сигнал выбора блока поступает на вход триггера подключения блока ввода-вьшода (не показан). На синхровход этого триггера поступает сигнал Номер блока с элемента И 13, при этом задержка сигнала Номер блока относительно сигнала, несущего, информацию о номере блока, определяется длительностью блокирующего импульса, поступающего на вход элемента И 13 с инверсного выхода первого -одновибратора 11. Наличие этих двух сигналов на входах триггера подключения блока

45

50

с дешифрированным номером модуля поступает в выбранньй блок ввода- вьшода на вход регистра номера модуля (не показан). Информация в регистр номера модуля записьшается с приходом на его синхровход сигнала Номер модуля, поступающего с выхода элемента И 14. Задержка сигнала Номер модуля относительно информационного сигнала определяется длител ностью блокирующего импульса, поступающего на вход элемента И 14 с инверсного выхода второго одновибрато- ра 12. Блок ввода-вывода формирует сигнал СП, указьшающий на то, что модуль выбран Этот сигнал подается в блок 3 управления обменом на вход элемента И 15, который вьщает сигнал СП, извещающий управляющий процессор о том, что выдача адреса окончена.

Блокировка сигнала СП, вырабатываемого блоком ввода-вьшода после приема номера блока, осуществляется сигналом с вьпсода триггера 19 модуля так как выбор номер блока еще не является окончанием цикла выдачи ад реса

ввода- вывода устанавливают его в состояние 1, давая тем самым разрешение на обмен информацией между управ-.

ляющим процессором и выбранным блоком ввода-вывода. После этого в выбранном блоке ввода-вывода формируется сигнал Синхронизация приема (СП), который поступает на вход триггера 18 блока и переводит его в исходное состояние. При этом снимается блокировка с мультиплексора 5, блокируется элемент И 13, снимается сигнал Номер блока, а следовательно, и сигнал СП. Выбор блока ввода-вывода осуществлен.

Сигнал с инверсного выхода триггера 18 блока запускает второй одно- вибратор 12, импульс на прямом выходе которого своим передним фронтом устанавливает триггер 19 модуля в состояние 1. Сигнал с выхода триггера 19 модуля поступает на входы элементов ИЛИ 20, И 14 и 15 и на вт,орой вход мультиплексора 5, который выбирает из адресного слова с третьего по пятый разряды, соответ-. ствующие номеру выбираемого модуля Как и в цикле выбора номера блока, сигнал с выхода элемента ИЛИ 20 разрешает дешифрацию информации, посту- пивщей на адресные входы дешифрато-

Q ра 4. С выхода дешифратора 4 сигнал

5

0

45

50

с дешифрированным номером модуля поступает в выбранньй блок ввода- вьшода на вход регистра номера модуля (не показан). Информация в регистр номера модуля записьшается с приходом на его синхровход сигнала Номер модуля, поступающего с выхода элемента И 14. Задержка сигнала Номер модуля относительно информационного сигнала определяется длительностью блокирующего импульса, посту ; пающего на вход элемента И 14 с инверсного выхода второго одновибрато- ра 12. Блок ввода-вывода формирует сигнал СП, указьшающий на то, что модуль выбран Этот сигнал подается в блок 3 управления обменом на вход элемента И 15, который вьщает сигнал СП, извещающий управляющий процессор о том, что выдача адреса окончена.

Блокировка сигнала СП, вырабатываемого блоком ввода-вьшода после приема номера блока, осуществляется сигналом с вьпсода триггера 19 модуля, так как выбор номер блока еще не является окончанием цикла выдачи ад реса

После получения сигнала СП управ- ляющий процессор снимает адресное слово и сигналы ВА и СВ. Снятие сигнала ВА блокирует первый 11 и второй 12 одновибраторы, триггер 18 блока, триггер 19 модуля и элемент И 15. При этом снимаются сигналы Номер модуля, и СП. После окончания цикла выдачи адреса следует цикл записи информации в выбранный модуль или цикл чтения информации из выбранного модуля.

Формула изобретения

1 о Устройство для управления обменом информацией между управляющим процессором и внешним устройством, содержащее блок управления, дешифратор, мультиплексор, шинный формирователь, причем первая и вторая группы входов-выходов логического условия блока управления образуют группы входов-выходов устройства дпя подключения соответственно к группам входов- выходов синхронизации управляющего процессора, первый, второй выходы блока управления являются выходами устройства для подключения соответственно к первому, второму командным входам внешнего устройства, первая гр уппа входов логического условия г--: блока управления содинена с группой

0

входов-выходов шинного формирователя соединена С группой информационных выходов дешифратора и образует группу входов-выходов устройства для подключения к группе информационных и адресных входов-выходов внешнего устройства, при этом группа информационных выходов мультиплексора соединена с группой информационных входов дешифратора. 2. Устройство по п.1, отличаю- щ е е с. я тем, что. блок управления содержит триггер блока, триггер моду- ля, шинный формирователь, два одно- вибратора, пять элементов И, два элемента.ИЛИ, причем первая группа информационных входов-выходов шинного формирователя, выход первого элемента И и первый вход запуска первого одновибратора образуют первую группу входов-выходов логического условия блока, вторая группа информационных входов-выходов шинного формирователя, синхровход триггера блока, соединенный с первым входом первого элемента И, образуют вторую группу входов-выходов логического условия блока, первый вход второго элемента И соединен с первым входом третьего элемента И и является входом логического условия блока, второй вход второго элемента И, первый, второй входы первого элемента ИЛИ образуют

0

5

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1984 |

|

SU1208558A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для сопряжения процессора с абонентами | 1986 |

|

SU1361529A1 |

Изобретение относится к вычислительной технике и предназначено для управления обменом информацией в вычислительных системах, которые могут быть использованы для управления технологическими процессами, автоматическими линиями, робототехническими комплексами. Целью изобретения является повышение быстродействия и упрощение. Устройство содержит блок управления, дешифратор, мультиплексор, шинный формирователь. 1 з.п. ф-лы, 2 ил.

входой направления обмена шинного фор- , группу входов логического условия

-Jw ,

мирователя и образует группу входов устройства для подключения к группе командных выходов управляющего процессора, вход логического условия блока управления соединен с разрешающим входом шинного формирователя и является входом устройства для подключения к командному выходу управляющего процессора, при этом

блока, выходы четвертого, пятого ментов И являются соответственно первым, вторым выходами блока, вых второго элемента ИЛИ является трет д(- вьпсодом блока, единичный выход три гера блока соединен с первыми вход ми четвертого элемента И, второго элемента ИЛИ и является четвертым выходом блока, единичный выход три

третий, четвертый и пятый выходы бло- 45 Р модуля соединен с первым входом

ка управления соединены соответственно с разрешающим входом дешифратора и с первым, вторым управляющими входами мультиплексора, отличаю- ; щ е е с я тем, что, с целью повьш1е-. ВИЯ быстродействия и упрощения, группа информационных входов мультиплексора соединена с первой группой информационных входов-выходов шинного формирователя и образует группу вхо- дев-выходов устройства для подключения к группе информационных и адресных входов-вькодов управляющего процессора, вторая группа информациоиных

,

блока, выходы четвертого, пятого элементов И являются соответственно первым, вторым выходами блока, выход второго элемента ИЛИ является третьим вьпсодом блока, единичный выход триггера блока соединен с первыми входами четвертого элемента И, второго элемента ИЛИ и является четвертым выходом блока, единичный выход триггепятого элемента И, с вторыми входами первого элемента И, второго элемента ИЛИ и является пятым выходом блока, при этом в блоке управления

выход второго элемента И соединен с нулевыми входами триггеров модуля и блока, с первым входом запуска второго одновибратора и с вторым входом запуска первого одновибратора, первый

выход которого соединен с единичным входом триггера блока, нулевый выход которого соединен с вторым входом запуска второго одновибратора, первый ыход которого соединен с вторым

йходом пятого элемента И,и с третьим входом первого элемента И, вторые выходы первого И второго одновибрато- ров соединены соответственно с вторым входом четвертого элемента И и с единичным входом триггера модуля, выход первого элемента ИЛИ соединен с

Фиг.1

вторым входом.третьего элемента И, выход которого соединен с управляющим входом шинного формирователя, информационные входы триггеров блока и модуля и синхровход триггера модуля подключены к шине нулевого потенциала устройства

| Патент США № 4115856, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1984 |

|

SU1208558A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-07-05—Подача