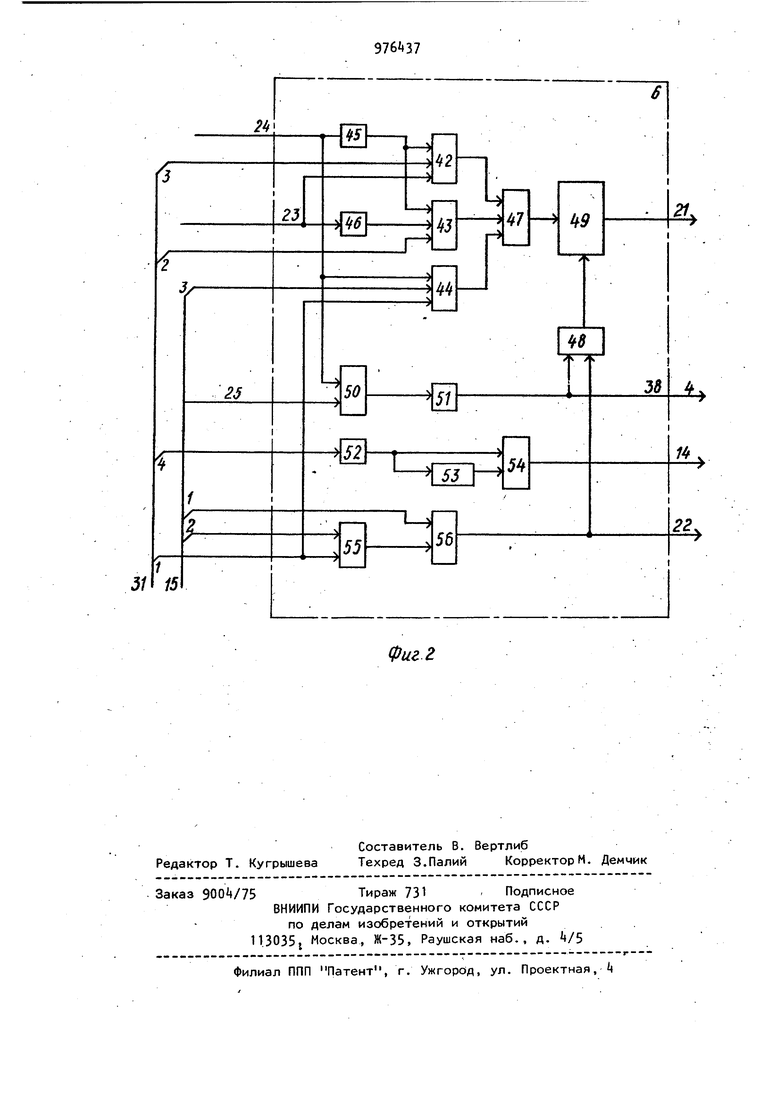

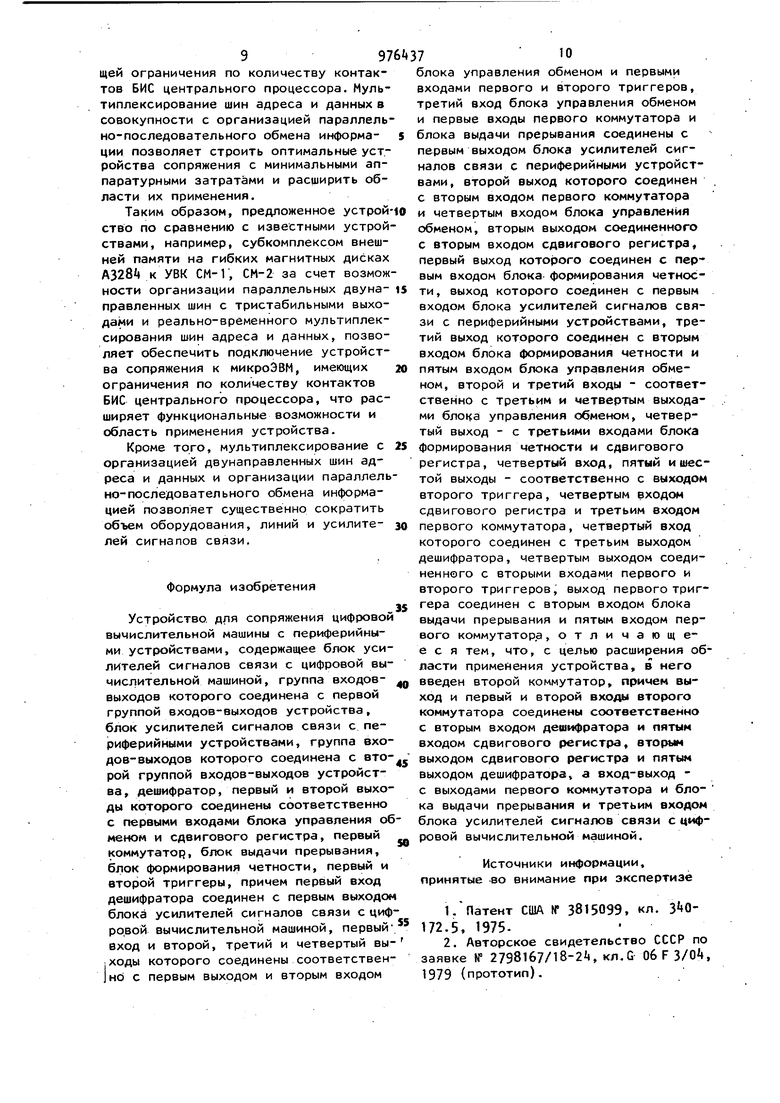

нен с вторым входом сдвигового регист ра, первый выход которого соединен с первым входом блока формирования четности, выход которого соединен с первым входом блока усилителей сигналов связи с периферийными устройствами, третий выход которого соединен с вторым входом блока формирования четности и пятым входом блока управления обменом, третий и четвертый выходы которого соединены с вторым и третьим входами блока усилителей сигналов связи с периферийными устройствами, четвертый выход последнего соединен с третьим входом блока формирования четности и третьим входом сдвигового регистра, четвертый вход последнего соединен с пятым вь xoдoм блока усилителей сигналов связи с периферийными устройствами, четвертый вход и шестой выход которого соединены соответствен но с выходом второго триггера и треть им входом первого коммутатора, четвер тый вход которого соединен с третьим выходом дешифратора, четвертый выход которого соединен с первыми входами первого и второго триггеров, второй вход которого соединен с третьим выходом блока,усилителей сигналов связи с ЦВМ, четвертый выход которого соединен с вторым входом первого триггера , выход которого соединен с вторым входом блока выдачи прерывания и пятым входом первого коммутатора 2} Недостатком этого устройства является ограниченная область применения. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, что в устройство, содержащее-блок усилителей сигналов связи с цифровой вычислительной машиной, группа входоввыходов которого соединена с первой группой входов-выходов устройства, блок усилителей сигналов связи спери ферийными устройствами, группа входов выходов которого соединена с второй группой входов-выходов устройства, дешифратор, первый и второй выходы которого соединены соответственно с первыми входами блока управления обменом и сдвигового регистра, первый коммутатор, блок выдачи прерывания, блок формирования четности, первый и второй триггеры, причем первый вход дешифратора соединен с первым выходом блока усилителей сигналов связи с цифровой вычислительной машиной, первый вход и второй, третий и четвертый выходы которого соединены соответственно с первым выходом и вторым входом блока управления обменом и первыми входами первого и второго триггеров, третий вход блока управления обменом и первые входы первого коммутатора и блока выдачи прерывания соединены с первым выходом блока усилителей сигналов связи с периферийными устройствами, второй выход которого соединен с вторым входом первого коммутатора и четвертым входом блока управления обменом, вторым выходом соединенного с вторым..входом сдвигового регистра, первый выход которого. соединен с первым входом блока формирования четности, выход которого соединен с первым входом блока усилителей сигналов связи с периферийными устройствами, третий выход которого соединен с вторым входом блока формирования четности и пятым входом блока управления обменом, второй и третий входы - соответственно с третьим и четвертым вь1ходами блока управления обменом, четвертый выход - с третьими входами блока формирования четности и сдвигового регистра, а четвертый вход,.пятый и шестой выходы - соответственно с выходом второго триггера, четвертым входом сдвигового регистра и третьим входом первого коммутатора, четвертый вход которого соединен с третьим выходом дешифратора, четвертым выходом соединенного с вторыми входами первого и второго триггеров, выход первого триггера соединен с вторым входом блока выдачи прерывания и пятым входом первого коммутатора, введен второй KOMMytaTop, причем выход и первый и второй входы второго коммутатора соединены соответственно с вторым входом дешифратора и пятым входом сдвигового регистра, вторым выходом сдвигового регистра и пятым выходом . дешифратора, а вход-выход - с выходами первого коммутатора и блока выдачи прерывания и третьим входом блока усилителей сигналов связи с цифровой вычислительной машиной. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема блока управления обменом. Устройство содержит блок Г усилителей сигналов связи с вычислительной машиной, блок 2 усилителей сигналов связи с периферийными устройствами, дешифратор 3, сдвиговый регистр k, первый коммутатор 5, блок 6 управления обменом, первый триггер 1, второй триггер 8, блок 9 выдачи прерывания, блок 10 формирования четности, второй коммутатор 11, выход 12 второго коммутатора 11, соединенный с входом 13 сдвигового регистра 4, первый вход 14, второй-четвертый и первый выходы , второй вход 19 блока 1 усилителей сигналов связи с вычислительной машиной, шестой выход 20, второй, третий входы 21 и 22, третий, первый и второй выходы 23-25, четвертый и первый входы 26 и 27, четвертый и пятый выходы 28.и 29 блока 2 усилителей сигналов связи с периферийными устройствами, четвертый, первый, третий, пятый и второй выходы 30-34, второй вход 35 дешифратора 3 адреса, выходы 36 и 37 сдвигового регистра 4, выход 38 блока 6 управления обменом, выход 39 первого триггера 7, группы 40 и 41 входов-выходов устройства. Блок 6 управления обменом включает в себя элементы И 42-44, элементы НЕ 45 и 46, элементы ИЛИ 47 и 48, триггер 49, элемент ИЛИ 50, элементы НЕ 51 и 52, элемент 53 задержки, элементы И 54 и 55. элемент ИЛИ 5б. Устройство работает следующим образом. Программный обмен информацией между оперативной памятью ЦВМ и периферийными устройствами осуществляется под управлением программы ЦВМ. При работе в программном режиме в устройстве использованы два поля сдвигового регистра 4 адресуемых со стороны мини шины поля команд и состояния поля дан ных. Программным путем можно загружать и считывать информацию из сдвигового регистра 4. Обращение к любому полю регистра 4 производится следующим образом. Процессор выставляет на линии адре са адрес поля. Затем выдается сигнал синхронизации мини-шины. Блок 3 дешиф рирует адрес, поступающий в него с выхода 18 (старшие разряды) и с входавыхода 19 (младшие 8 разрядов) через второй коммутатор 11 по входу 35, и запоминает, его. Потом .на линии кода операции выставляется код чтения, либо записи. После чего дешифратор 3 выставляет соответствующий сигнал на выходе 34 обращения к полям регистра 4. При записи 8-разрядная информация в сдвиговый регистр 4 поступает с входа-выхода 19 через второй коммутатор 11, при чтении информация из регистра 4 по выходу 37 поступает на группу входов-выходов 4О по входу-выходу 19 через второй коммутатор 11 параллельно. Направление передачи информации через второй коммутатор 11 определяет управляющий сигнал, поступающий с дешифратора 3 по выходу 33 и определяемый кодом операции. Дешифратор 3 сигнализирует блоку 6 о выполнении операции по выходу 31, после чего блок 6 вырабатывает ответный синхронизирующий сигнал, поступающий на группу входов-выходов 40 с входа 14. Процессор, приняв этот сигнал, заканчивает операцию протокола обмена. Если производится обращение к регистру периферийного устройства, дешифратор 3 дешифрирует адрес данного периферийного устройства, принимаемый с выходов 18 и 19 через второй коммутатор 11 по входу 35 и запоминает его. Затем процессор выставляет код операции по выходу 18, а дешифратор 3 формирует сигнал по выходу 34 и по выходу 31 запускает блок 6. Блок 6 сигналов по выходу 38 разрешает занесение в сдвиговый регистр 4 номер периферийного устройства и кода операции , поступающий через второй коммутатор 11 с входа-выхода 19. При этим блок 6 сигналом Управление по входу 24 через блок 2 сообщает,периферийному., устройству о готовности принятой информации к передаче на периферийное устройство. Регистр команд и состояНИИ и регистр данных периферийного устройства реализации на общем 8-разрядном сдвиговом регистре. Направление передачи информации между устройством сопряжения и периферийными устройствами определяется сигналом Направление по выходу 23 блока 2. Нулевое значение сигнала Направление означает передачу информации из устройства сопряжения, единичное - в устройство сопряжения из периферийного устройства. Единичное значение сигнала Конец операции по выходу 24 указывает на то, что периферийное устройство не работает и ждет команду от процессора ЦВМ. Для передачи кода команды, занесенного в сдвиговый регистр 4, на периферийное устройство необходимо, чтобы сигнал Направление по выходу 23 был нулевым, а сигнал Конец операции по выходу 24 был единичным. Периферийное устройство в ответ на сигнал Управление по входу 22 блока 2 преобразу7 9 ет информацию, записанную в параллель ном коде в сдвиговом регистре 4, в последовательную. Последовательная ин формация с выхода 36 сдвигового регис тра k, проходя через блок 10 формирования четности, поступает по входу 27 блока 2 на периферийное устройство, которое формирует имаульсные сигналы Сдвиг по выходу 28 блока 2 для приема кода команды и бита четности конт роля передачи информации. После этого периферийное устроиство выставляет нулевой сигнал Конец операции по выходу 24 блока 2 и формирует единичный сигнал Требование по выходу 25 блока 2, который поступает в блок управления обменом. Сигналом 38 блока 6 правления обменом разрешается параллельная загрузка информаций по входу-выходу 19 блока 1 через второй коммутатор 11 в сдвиго вый регистр k, а сигналом Управление по входу 22 блока 2 периферийному устройству сообщается о готовности информации к передаче. Периферийное устройство снова формирует сигналы Сдвиг по выходу 28 блока 2 для приема байта информации, затем выставляет сигнал Требование по выходу 25. Этот обмен происходит до Tfcx пор, пока не будет передано заданное число байтов информации, (например, 128) или из процессора не поступит сигнал Конец блока записи по входу 17 блока 1 и синхронизирующий сигнал по выходу 30 дешифратора 3. Состояние второго триггера 8 анализируется периферийным устройством по входу 2б блока 2. По, окончании о бмена периферийное устройство выставляет единичный сигнал Конец операции по выходу 2k блока 2. Если- кодом команды задается пере-: дача информации из периферийного устройства в процессор, то периферийное устройство формирует единичный сигнал Направление по выходу 23 блока 2, который блокирует выход блока 10 формирования четности, сигнал по выходу 38 блока 6 разрешает преобразование последовательной информации, поступающей по выходу 29 блока 2, в параллельную на сдвиговом регистре k. При этом периферийное устройство формирует импульсные сигналы Сдвиг. Сформированная информация параллельным кодом-со сдвигового регистра k по выходу 37 передается в процессор через второй коммутатор 11 по входу 19 бло37 .8 ка 1. При этом по выходу 30 дешифратор 3 формирует нулевой сигнал, который разрешает передачу информации со сдвигового регистра k по выходу 37 через второй коммутатор 11. Перед передачей следующего байта периферийное устройство формирует единичный сигнал Требование по выходу 25 блока 2, если надо передать еще один байт, или единичный сигнал Конец операции по выходу 2 блока 2; если выполнение операции закончено. В режиме автоматической обработки запросов устройство работает следующим образом. Первый триггер 7 программно устанавливается от ЦВМ при появлении синхронизирующего сигнала с выхода 30 дешифратора 3. Если периферийное устройство закончило выполнение заданной команды, то оно формирует единичный сигнал Конец операции по выходу 2k блока 2. При совпадении единичных сигналов Конец операции и сигнала на выходе 39 первого триггера 7 блок 9 выдачи прерывания формирует вектор i прерывания - адрес ячейки памяти ЦВМ, хранящей начальный адрес программы, и передает его в процессор по входу 19 сообщая ему, что периферийное устройство закончило выполнение заданной команды. В исходное состояние периферийные устройства устанавливаются сигналом Сброс на вход 21 блока 2, выработанным блоком 6. При этом процессор выдает общий или программный сброс по выходу 15 блока 1, который поступает на блок 6. По сигналу с выхода 32 дешиф,ратор 3 в процессор через первый коммутатор 5 по входу 19 передаются признаки состояний: сигнал Конец операции по выходу 2k, сигнал .Требование по выходу 25, сигнал Ошибка по выходу 20 блока 2 и состояние первого триггера 7. Коммутатор 11 может быть построен на двух ИМС типа К 589 АП26, позволяющих организацию приема и выдачи информации с параллельных двунаправленных шин с тристабильными выходами, реально-временного мультиплексирования шин адреса и данных. Последнее сокращает количество линий и усилителей сигналов связи протокола обмена с периферийными устройствами, что является обязательным Требованием для устройств сопряжения с микро-ЭВМ, имеющей ограничения по количеству контактов БИС центрального процессора. Мультиплексирование шин адреса и данных в совокупности с организацией параллель но-последовательного обмена информации позволяет строить оптимальные устройства сопряжения с минимальными аппаратурными затратами и расширить области их применения. Таким образом, предложенное устрой ство по сравнению с известными устрой ствами, например, субкомплексом внешней памяти на гибких магнитных дисках А328Ц к УВК СМ-Г, СМ-2 за смет возмож ности организации параллельных двунаправленных шин с тристабильными выходами и реально-временного мультиплексирования шин адреса и данных, позволяет обеспечить подключение устройства сопряжения к микроЭВМ, имеющих ограничения по количеству контактов БИС центрального процессора, что расширяет функциональные возможности и область применения устройства. Кроме того, мультиплексирование с организацией двунаправленных шин адреса и данных и организации параллель но-последовательного обмена информацией позволяет существенно сократить объем оборудования, линий и усилителей сигналов связи. Формула изобретения Устройство, для сопряжения цифровой вычислительной машины с периферийными устройствами, содержащее блок усилителей сигналов связи с цифровой вычислительной машиной, группа входоввыходов которого соединена с первой группой входов-выходов устройства, блок усилителей сигналов связи с. периферийными устройствами, группа входов-выходов которого соединена с второй группой входов-выходов устройства, дешифратор, первый и второй выходы которого соединены соответственно с первыми входами блока управления об меном и сдвигового регистра, первый коммутатор, блок выдачи прерывания, блок формирования четности, первый и второй триггеры, причем первый вход дешифратора соединен с первым выходом блока усилителей сигналов связи с циф ровой вычислительной машиной, первый вход и второй, третий и четвертый выходы которого соединены соответственно) с первым выходом и вторым входом блока управления обменом и первыми входами первого и второго триггеров, третий вход блока управления обменом и первые входы первого коммутатора и блока выдачи прерывания соединены с первым выходом блока усилителей сигналов связи с периферийными устройствами, второй выход которого соединен с вторым входом первого коммутатора и четвертым входом блока управления обменом, вторым выходом соединенного с вторым входом сдвигового регистра, первый выход которого соединен с первым входом блока формирования четности, выход которого соединен с первым входом блока усилителей сигналов связи с периферийными устройствами, третий выход которого соединен с вторым входом блока формирования четности и пятым входом блока управления обменом, второй и третий входы - соответственно с третьим и четвертым выходами блока управления обменом, четвертый выход - с третьими входами блока формирования четности и сдвигового регистра, четвертый вход, пятый и шестой выходы - соответственно с выходом второго триггера, четвертым входом сдвигового регистра и третьим входом первого коммутатора, четвертый вход которого соединен с третьим выходом дешифратора, четвертым выходом соединенного с вторыми входами первого и второго триггеров, выход первого триггера соединен с вторым входом блока выдачи прерывания и пятым входом первого коммутатора,отличающее с я тем, что, с целью расширения области применения устройства, в него введен второй коммутатор, причем выход и первый и второй входы второго коммутатора соединены соответственно с вторым входом дешифратора и пятым входом сдвигового регистра, вторым выходом сдвигового регистра и пятым выходом дешифратора, а вход-выход с выходами первого коммутатора и бпока выдачи прерывания и третьим входом блока усилителей сигналов связи с цифровой вычислительной машиной. Источники информации, принятые -ВО внимание при экспертизе 1/Патент США № 38150Э9, . З О172.5. 19752. Авторское свидетельство СССР по заявке № 2798167/18-2 1, кл.G Об F З/О, 1979 (прототип).

itO .

М

Фиг г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1979 |

|

SU955013A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198530A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения электронных вычислительных машин | 1981 |

|

SU1013938A1 |

| Устройство для сопряжения цифровой вы-чиСлиТЕльНОй МАшиНы C пЕРифЕРийНыМи уСТРОй-СТВАМи | 1979 |

|

SU840874A1 |

Авторы

Даты

1982-11-23—Публикация

1981-05-18—Подача