1

;(21) 4273070/24-24

(22) 29.05.87

(46) 07.09.89. Бкш. № 33

(72) В.Н.Куценко, Н.В.Косинов

и И.В.Стахова

(53)681.3(088.8)

(56)Измерения и контроль в микроэлектронике. - М.: Высшая школа,

1984,с. 338-343.

Приборы и системы управления,

1985,№ 6, с. 26, рис. 1.

(54)СИГНАТУРНЫЙ АНАГИЗАТОР ДЛЯ КОНТРОЛЯ УСТРОЙСТВ ПАМЯТИ

(57)Изобретение относится к вычислительной технике и может использоваться для контроля и диагностики устройств памяти. Цель - повьпиение достоверности контроля. Анализатор содержит формирователь 1 управляющих сигналов, блок 2 сжатия данных, генератор 3 псевдослучайной тестовой последовательности, счетчик 4, элемент 5 задержки, узел 6 синхронизации записи/чтения, м льтиплексор 7, узел 8 адресаций, демультиплексор 9, блок 10 индикации. Анализатор позволяет обнаружить все отказы запогчинающего устройства типа Залипание 1 и Зали- пание О. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU968856A1 |

Изобретение относится к вычислительной технике и может использоваться для контроля и диагностики устройств памяти. Цель - повышение достоверности контроля. Анализатор содержит формирователь 1 управляющих сигналов, блок 2 сжатия данных, генератор 3 псевдослучайной тестовой последовательности, счетчик 4, элемент 5 задержки, узел 6 синхронизации записи/чтения, мультиплексор 7, узел 8 адресаций, демультиплексор 9, блок 10 индикации. Анализатор позволяет обнаружить все отказы запоминающего устройства типа "залипание 1" и "залипание 0". 3 ил.

г

(Л

iiZ.i

10

31506449

Изобретение относится к вычисли- , тельной и электроизмерительной технике и может быть использовано ппА контроля и диагностики устройства па- мяти.

Цель изобретения повьпиение достоверности контроля.

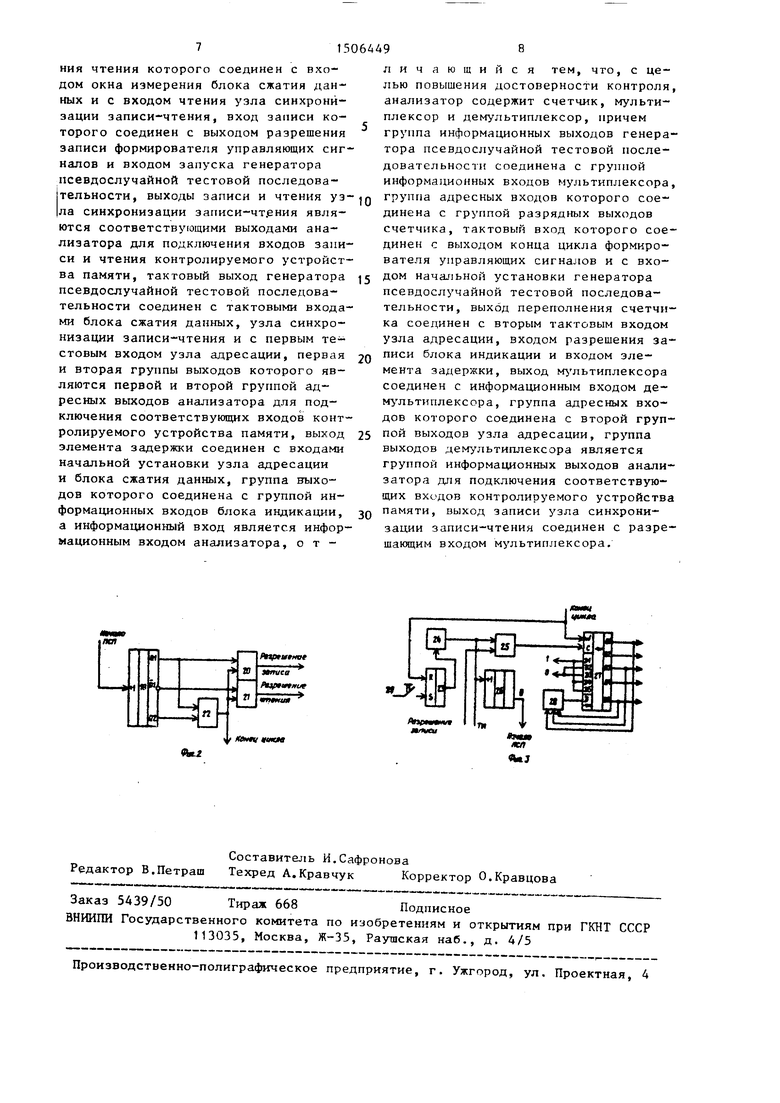

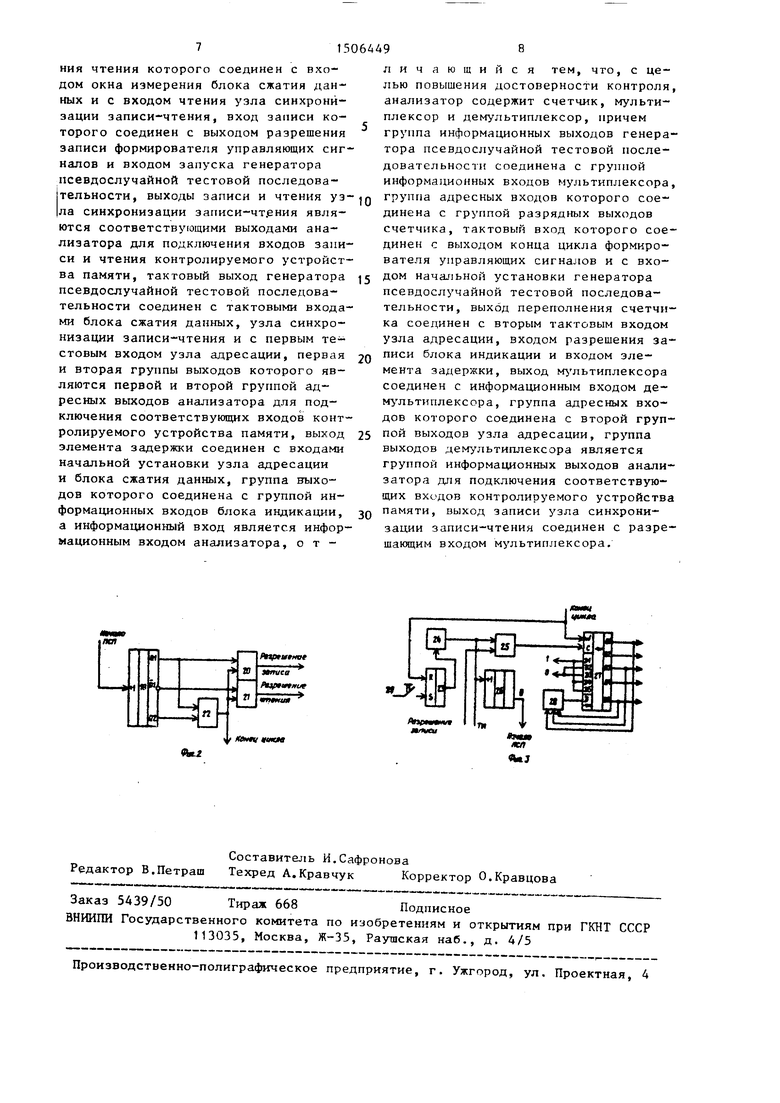

На фиг. 1 показана структурная схема анализатора; на фиг. 2 - схема формирователя управлякхцих сигналов; на фиг. 3 - схема генератора псевдослучайной тестовой последовательности.

Анализатор содержит формирователь 1 управляющих сигналов, блок 2 сжатия данных, генератор 3 псевдослучайной тестовой последовательности, счетчик 4, элемент 5 задержки, узел 6 синхронизации записи-чтения, мульти- 20 плексор 7, узел 8 адресации, дем ль15

тананливается в единичное состояние, запуская генератор 24 импульсов, сигналы с которого поступают на узел 8 адресации и считаются на т-разрядном счетчике 26 генератора 3, при переполнении которого появляется сигнал Начало ПСП. Одновременно в узле адресации устанавливается нулевое значение адреса ячейки и адрес первой линейки испытуемого элемента памяти. Сигнал Начало ПСП поступает на счетчик 19 формирователя 1 управляющих сигналов, устанавливая его в значение (10) . При этом на выходе сумматора 22 появляется единичный сигнал Конец цикла, разрешающий прохождение сигнала Разрешение записи с прямого выхода первого разряда счетчика 19 через первый элемент И 20 на узел 6 синхронизации, который раз решает работу испытуемого элемента памяти D режиме записи и разрешает работу мультиплексора 7, на адресные

12 и 13, формирова-25 входы которого поступают сигналы со

счетчика 4.

Разрядность счетчика 4 определяется требуемой вероятностью контроля г зависит от максимальной длины серии, анали- 30 формируемой генератором псевдослучайной последовательности. Для обеспечения полного контроля запоминающих устройств сигнатурным анализатором с порождающим полиномом его генератора

типлексор 9, блок 10 индикации, контролируемое устройство 11 памяти.

В состав блока 2 сжатия данных входят элементы И тель 14 сигнатур.

В состав блока 10 индикации входят буферный регистр 15, преобразователь 16 и индикатор 17. На чертеже показан информационный вход 18 затора.

I Формирователь 1 управляющих сигналов содержит счетчик 19, элементы и 20 и 21 и сумматор 22.

Генератор 3 псевдослучайной тесто-35 псевдослучайной последовательности

и начальной установкой (11001).; счетчик 4 должен быть двух разрядным. Таким образом, счетчик 4 предназначен для определения колич ва цикх1ов записи-считывания, необх димых для контроля испытуемого эле мента памяти, в течение которых фо мируется сигнатура контролируемой линейки ячеек памяти. Сигнал Коне цикла поступает также на регистр генератора 3, устанавливая его в н чальное значение. Так как генерато псевдослучайной последовательности формирует на каждом выходе одинако вые последовательности, но сдвинут одна относительно другой на один такт, то дпя перекрытия их серий д статочно записывать в одни и те же ячейки контролируемого запоминающе устрэйства сигналы, формируемые ге ратором 3 на каждом цикле записи- считывания с разных разрядов сдвиг вого регистра 27, что и обеспечива мультиплексор 7, подключающий в за

вой последовательности содержит триггер 23, генератор 24 импульсов, элемент И 25, счетчик 26, регистр 27, сумматор 28 по модулю два и кнопку 29

Сигнатурный анализатор дпя контроля запоминающих устройств работает в режиме формирования сигнатуры и ре- жиме ее контроля и позволяет контролировать запоминающие устройства емкостью п х т, последовательно получая на индикаторе сигнатуры информации каждой i-й линии ().

При включении сигнатурного анализатора счетчик 4, узел В адресации и формирователь 1 управляющих сигналов устанавливаются в нулевое состояние (линия начальной установки не показана) . При этом на первом выходе формирователя 1 управляющих сигналов формируется сигнал Конец цикла, который устанавливает в нулевое состояние генератор 3.

В режиме формирования сигнатуры при нажатии кнопки 29 триггер 23 ус

псевдослучайной последовательности

и начальной установкой (11001).; счетчик 4 должен быть двухразрядным. Таким образом, счетчик 4 предназначен для определения количества цикх1ов записи-считывания, необходимых для контроля испытуемого элемента памяти, в течение которых формируется сигнатура контролируемой линейки ячеек памяти. Сигнал Конец цикла поступает также на регистр 27 генератора 3, устанавливая его в начальное значение. Так как генератор псевдослучайной последовательности формирует на каждом выходе одинаковые последовательности, но сдвинутые одна относительно другой на один такт, то дпя перекрытия их серий достаточно записывать в одни и те же ячейки контролируемого запоминающего устрэйства сигналы, формируемые генератором 3 на каждом цикле записи- считывания с разных разрядов сдвигового регистра 27, что и обеспечивает мультиплексор 7, подключающий в зави51

симости от номера цикла записи-считывания, задаваемого счетчиком , соответствующий выход генератора 3 псевдослучайной последовательности генератора к демультиплексору 9,

Дем льтиплексор 9 передает сигналы с выхода мультиплексора 7 на вход испытуемого элемента памяти, адрес которого задается счетчиком линейки узла 8 адресации, что обеспечивает запись сигналов с генератора 3 в ячейки проверяемой линейки элемента памяти. Таким образом, при появлении первого сигнала Конец цикла выход первого разряда сдвигового регистра 27 генератора 3 подсоединяется к первому входу испытуемого элемента памяти. По приходу каждого следующего сигнала с генератора 24 импульсов значения счетчика адреса ячеек узла 8 адресации и счетчика 26 генератора 3 увеличиваются на единицу и в соответствующую ячейку памяти записывается следующее значение сигнала, сформированного генератором 3. При переполнении счетчика 26 формируется сигнал Начало ПСП, который увеличивает на единицу значение счетчика 19. При этом его значение становится равным (01), единичное состояние на выходе сумматора 22 по модулю два не изменится и, таким образом, разрешается прохождение сигнала с инверсного выхода первого разряда счетчика 19 через элемент И 21, что соответствует переходу устройства с режима записи в испытуемый элемент памяти в режим считывания, при котором нулевое значение сигнала Разрешение записи закрывает прохоясдение тактовых импульсов с генератора 24 импульсов на сдвиговый регистр 27, который через открытый элемент И 13 поступают на тактовый вход формирователя 14 бло ца 2 сжатия данных. Таким образом, на каждом такте происходит считывание информации с ячеек первой линейки испытуемого элемента памяти и сжатие ее на формирователе 14.

При следующем переполнении счетчика 26 генератора 3 формируется сигнал Начало ПСП, который устанавливает счетчик 19 в состояние (I1)i. При этом на выходе сумматора 22 по модулю два формируется сигнал нулевого значения, запрещающий прохождение сигналов Разрешение записи и Разрешение чтения и увеличивающий

064496

значение счетчика на единицу, что соответствует подключение к тому же входу испытуемого элемента памяти следующего выхода генератора 3,

При появлении следующего сигнала Начало ПСП счетчик 19 устанавливается в нулевое состояние, после чего цикл записи тестовой

10 последовательности и цикл ее последующего считывания с формированием сигнатуры начинаются сначала. При этом после каждого цикла записи- считывания значение счетчика 4 уве-

15 личивается на единицу, что соответствует подключению к соответствующему входу испытуемого элемента памяти следующего выхода генератора 3 Таким образом, обеспечивается запись

20 в испытуемый элемент памяти псевдослучайной последовательности, сдвинутой на каждом цикле записи-чтения на один такт, что обеспечивает перекрытие ранее записанных в ячейки па-

25 мяти логических единиц логическими нулями, и наоборот. При переполнении счетчика 4, что соответствует концу контроля i-й линейки испытуемого элемента памяти, на выходе переполнения

30 счетчика 4 появляется сигнал, увеличивающий значение адреса линейки узла 8 адресации и разрешающий перезапись сигнатуры с формирователя 14 блока 2 сжатия данных в буферный регистр 15 для последующей индикации. Этот же сигнал через время, установленное элементом 5 задержки, устанавливает в начальное состояние адрес ячейки в узел 8 адресации и формиро35

ватель 14.

Таким образом, описанный сигнатурный анализатор позволяет обнаружить все отказы запоминающего устройства типа Залипание 1 и Залипа- ние О, что повьшает достоверность контроля запоминающих устройств. Формула изобретения Сигнатурный анализатор для контр- роля устройств памяти, содержащий фор- , мирователь управляющих сигналов, блок сжатия данных, генератор псевдослучайной тестовой последовательности, узел синхронизации записи-чтения, узел адресации, элемент задержки и блок индикации, причем управляющий выход начала теста генератора псевдослучайной тестовой последовательности соединен с входом формирователя управляю цих сигналов, выход разреше-

ния чтения которого соединен с входом окна измерения блока сжатия данных и с входом чтения узла синхронизации записи-чтения, вход записи которого соединен с выходом разрешения записи формирователя управляющих сигналов и входом запуска генератора псевдослучайной тестовой последовательности, выходы записи и чтения УЭла синхронизации записи-чт.ения являются соответствующими выходами анализатора для подключения входов записи и чтения контролируемого устройства памяти, тактовый выход генератора псевдослучайной тестовой последовательности соединен с тактовыми входами блока сжатия данных, узла синхронизации записи-чтения и с первым тестовым входом узла адресации, первая и вторая группы выходов которого являются первой и второй группой адресных выходов анализатора для подключения соответствую1цих входов контролируемого устройства памяти, выход элемента задержки соединен с входами начальной установки узла адресации и блока сжатия данных, группа выходов которого соединена с группой информационных входов блока индикации, а информационный вход является информационным входом анализатора, отч г Юна/ тнсив

.2

личающийся тем, что, с целью повышения достоверности контроля, анализатор содержит счетчик, мультиплексор и демультиплексор, причем группа информационных выходов генератора псевдослучайной тестовой последовательности соединена с группой информационных входов мультиплексора, группа адресных входов которого соединена с группой разрядных выходов счетчика, тактовый вход которого соединен с выходом конца цикла формирователя управляющих сигналов и с входом начальной установки генератора псевдослучайной тестовой последовательности, выход переполнения счетчика соединен с вторым тактовым входом узла адресации, входом разрешения записи блока индикации и входом зле- мента задержки, выход м льтиплексора соединен с информационным входом де- м льтиплексора, группа адресных входов которого соединена с второй группой выходов узла адресации, группа выходов демультиплексора является группой информационных выходов анализатора для подключения соответствующих входов контролируемого устройства памяти, выход записи узла синхронизации записи-чтения соединен с разрешающим входом мультиплексора.

OP-J,

Авторы

Даты

1989-09-07—Публикация

1987-05-29—Подача