Изобретение относится к цифровой вычислительной технике, в частности к устройствам для проверки микросхем, в том числе БИС микропроцессорных наборов.

Цель изобретения - расширение области применения за счет обеспечения возможности контроля цифровых блоков с двунаправленной передачей информации.

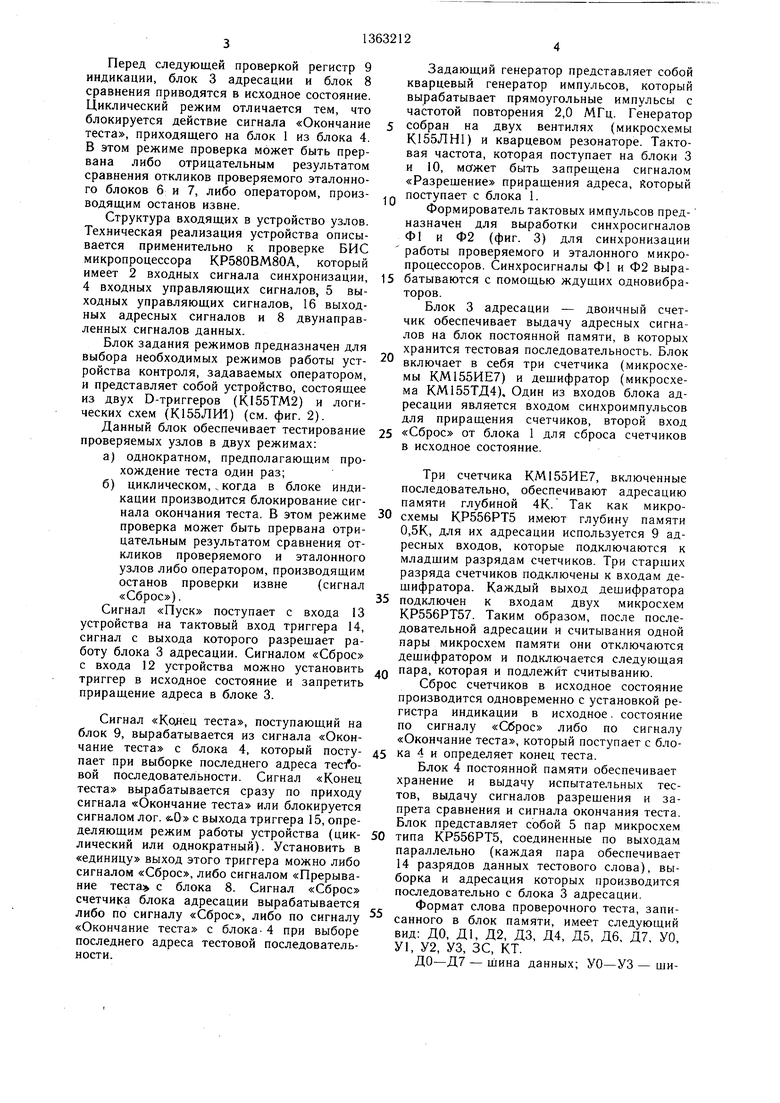

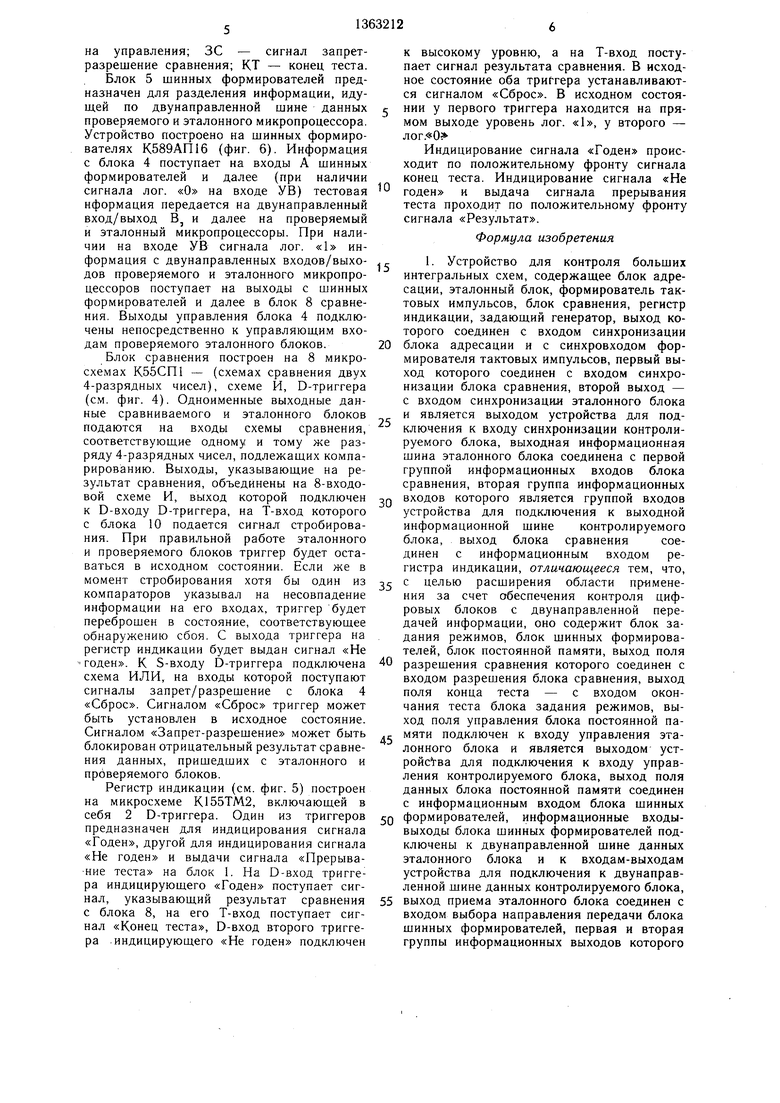

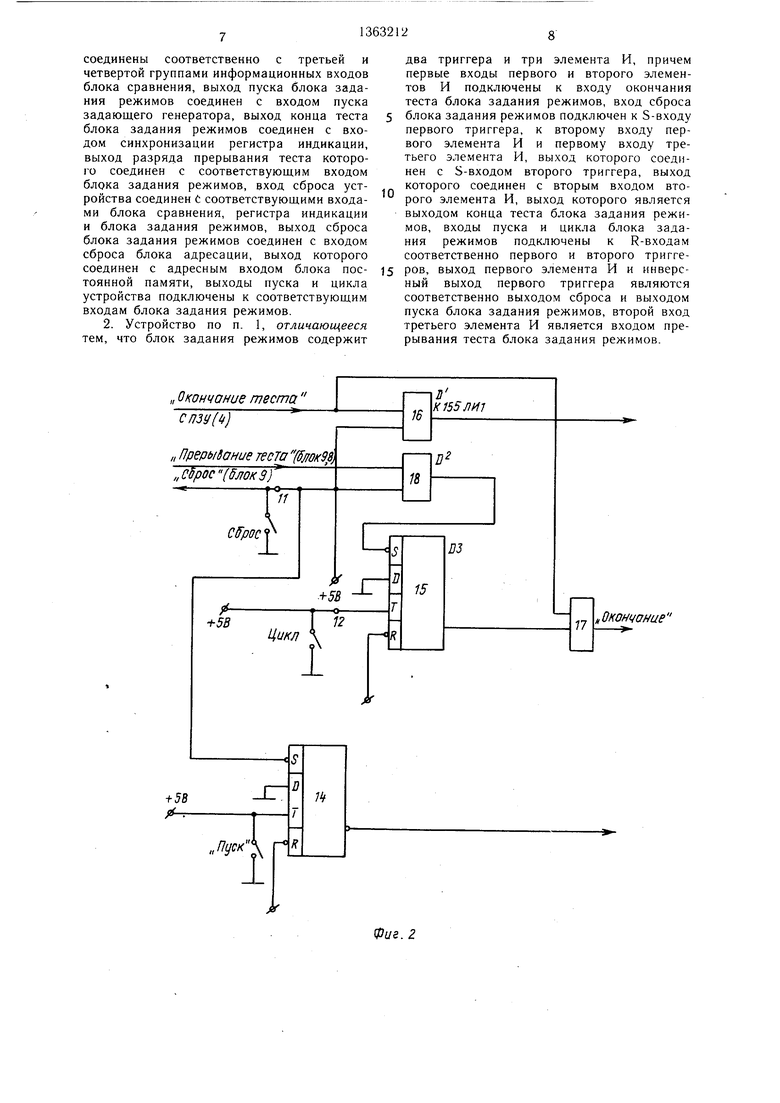

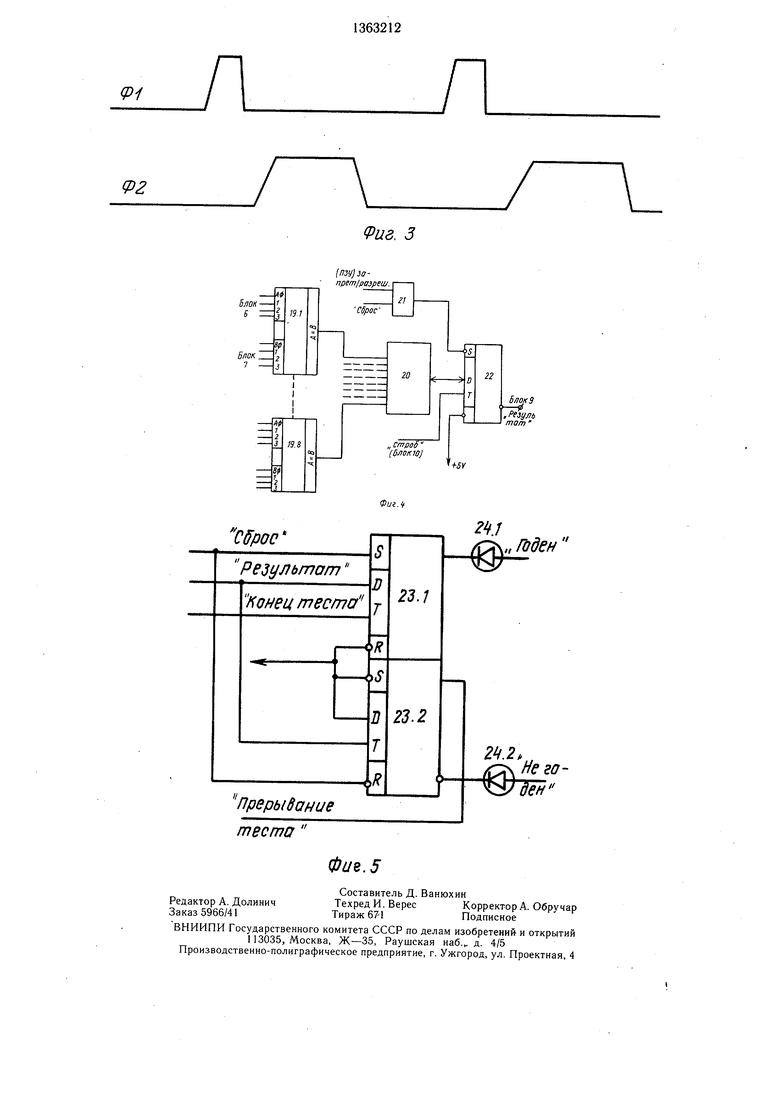

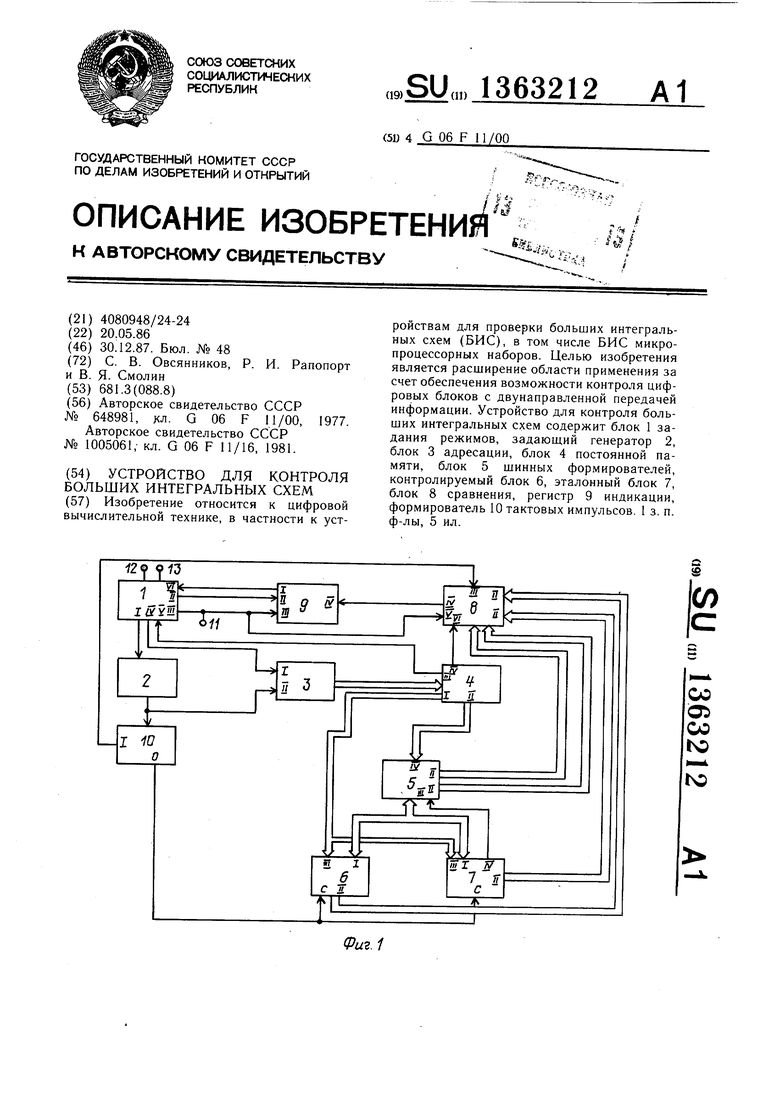

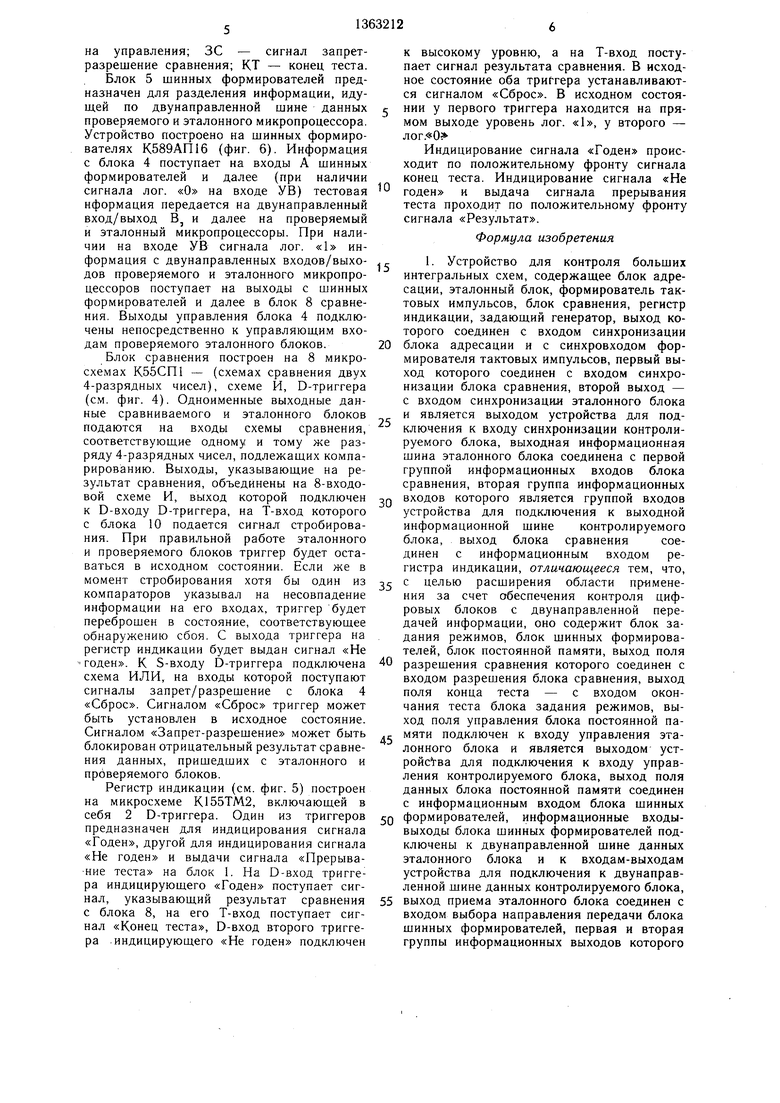

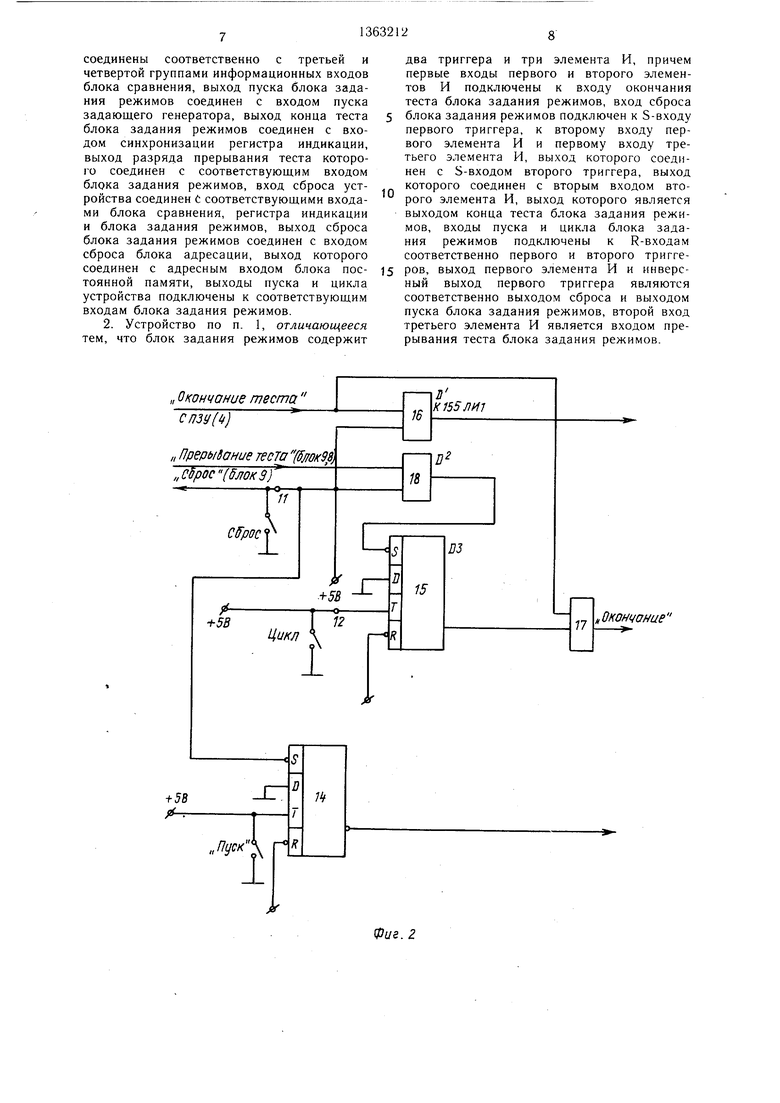

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока задания режимов; на фиг. 3 - синхросигналы, вырабатываемые блоком формирования тактовых импульсов; на фиг. 4 - схема блока сравнения; на фиг. 5 - схема регистра индикации.

Устройство (фиг. 1) содержит блок 1 за- Дания режимов, задающий генератор 2, блок 3 адресации, блок 4 постоянной памяти, блок 5 шинных формирователей, контролируемый блок 6, эталонный блок 7, блок 8 сравнения, регистр 9 индикации, формирователь 10 тактовых импульсов, вход 11 сброса устройства, вход 12 цикла устройства, вход 13 пуска устройства. Блок 1 задания режимов содержит первый 14 и второй 15 триггеры, первый 16, второй 17 и третий 18 элементы И.

Блок 8 сравнения содержит схемы 19.1 -19.8 сравнения, элемент И 20, элемент ИЛИ 21, триггер 22.

Регистр 9 индикации содержит первый 23.1 и второй 23.2 триггеры индикации, первый 24.1 и второй 24.2 элементы ин- дикации.

Устройство работает следующим образом.

Проверка цифрового блока начинается с выдачи блоком 1 сигнала, разреш.ающе- го работу задающего генератора 2, выра- батывающего сигналы определенной частоты, поступающие на вход формирователя тактовых импульсов и на вход 3 блока адресации. Формирователь 10 тактовых импульсов вырабатывает последовательности импульсных сигналов, необходимых для син- хронизации проверяемого эталонного блоков 6 и 7, на соответствующие входы которых поступают эти сигналы. Блок 3 адресации выполняет функцию адресования блока 4 памяти. Информация в блоке пос- тоянной памяти хранится в виде слов, выбираемых последовательно по одному за один такт работы задающего генератора 2. Слово состоит из двух полей. Одни разряды первого поля соединены с входами блока 5, который передает информацию с этих разрядов через двунаправленнук) щину на двунаправленные входы/выходы проверяемого и эталонного блоков 6 и 7 в те моменты, когда последние принимают команды или данные. Другие разряды соединены с управляющими входами проверяе- мого эталонного блоков 6 и 7. Последовательность первых полей является испытательным тестом. Разрядность первого поля зависит от типа полей про веряемого и эталонного блоков. Второе поле состоит из двух разрядов. Один из них, связанный с управляющим входом блока 8 сравнения, разрешает или запрещает сравнение данных, поступающих на -этот блок с проверяемого эталонного блока, в те или иные моменты времени. А второй разряд формирует сигнал «Окончание теста, поступающий на вход блока 1 задания режимов. В те моменты времени, когда проверяемый и эталонный блоки 6 и 7 вырабатывают выходную информацию на своих двунаправленных входах/выходах, блок 5 шинных формирователей осуществляет передачу данных с этих входов/выходов на входы блока 8 сравнения. Данные с однонаправленных выходов проверяемого и эталонного блоков 6 и 7 поступают непосредственно на блок 8 сравнения. Кроме того, один из управляющих выходов эталонного блока 7 используется для управления направлением передачи данных, осуществляемой блоком 5.

Блок 8 сравнения осуществляет операцию сравнения данных, поступающих с проверяемого и эталонного блоков 6 и 7 в каждом такте задающего генератора за исключением тех тактов, которые запрещены сигналом «Запрет/разрешение, поступающим из блока 4. Этот сигнал запрещает сравнение в те такты, когда выходы проверяемого и эталонного блоков 6 и 7 находятся в неопределенном состоянии.

Синхронизация процесса сравнения осуществляется синхронизирующим сигналом, поступающим на синхро-вход блока 8 сравнения с одного из выходов формирователя 10 тактовых импульсов.

Сигнал результата сравнения с выхода блока 8 сравнения поступает на вход регистра 9 индикации.

Предлагаемое устройство может работать в двух режимах, определяемых блоком 1 задания режимов: однократном; циклическом.

В однократном режиме, если в течение всего времени выполнения теста результаты сравнения были положительными, то при приходе нз блока постоянной памяти 4 на блок 1 сигнала «Окончание теста, этим блоком вырабатывается сигнал «Конец теста, поступающий на регистр 9 индикации, который вырабатывает при этом сигнал «Годен. Одновременно с выработкой сигнала «Конец теста блок 1 вырабатывает сигнал сброса, поступающий на блок 3 адресации. Первое же несовпадение сравниваемых данных приводит к тому, что регистр 9 индикации формирует сигнал «Не годен, а также сигнал «Прерывание теста, который поступает на блок 1 и вызывает прекращение проверки, снимая сигнал разрешения работы задающего генератора 2.

Перед следующей проверкой регистр 9 индикации, блок 3 адресации и блок 8 сравнения приводятся в исходное состояние. Циклический режим отличается тем, что блокируется действие сигнала «Окончание теста, приходящего на блок 1 из блока 4. В этом режиме проверка может быть прервана либо отрицательным результатом сравнения откликов проверяемого эталонного блоков 6 и 7, либо оператором, производящим останов извне.

Структура входящих в устройство узлов. Техническая реализация устройства описывается применительно к проверке БИС микропроцессора КР580ВМ80А, который имеет 2 входных сигнала синхронизации, 4 входных управляющих сигналов, 5 выходных управляющих сигналов, 16 выходных адресных сигналов и 8 двунаправленных сигналов данных.

Блок задания режимов предназначен для выбора необходимых режимов работы устройства контроля, задаваемых оператором, и представляет собой устройство, состоящее из двух D-триггеров (К155ТМ2) и логических схем (К155ЛИ1) (см. фиг. 2).

Данный блок обеспечивает тестирование проверяемых узлов в двух режимах:

а)однократном, предполагающим прохождение теста один раз;

б)циклическом,,когда в блоке индикации производится блокирование сигнала окончания теста. В этом режиме проверка может быть прервана отрицательным результатом сравнения откликов проверяемого и эталонного узлов либо оператором, производящим останов проверки извне (сигнал «Сброс).

Сигнал «Пуск поступает с входа 13 устройства на тактовый вход триггера 14, сигнал с выхода которого разрещает работу блока 3 адресации. Сигналом «Сброс с входа 12 устройства можно установить триггер в исходное состояние и запретить приращение адреса в блоке 3.

Сигнал «Колец теста, поступающий на блок 9, вырабатывается из сигнала «Окончание теста с блока 4, который поступает при выборке последнего адреса вой последовательности. Сигнал «Конец теста вырабатывается сразу по приходу сигнала «Окончание теста или блокируется сигналом лог. «.О с выхода триггера 15, определяющим режим работы устройства (циклический или однократный). Установить в «единицу выход этого триггера можно либо сигналом «Сброс, либо сигналом «Прерывание теста с блока 8. Сигнал «Сброс счетчика блока адресации вырабатывается либо по сигналу «Сброс, либо по сигналу «Окончание теста с блока- 4 при выборе последнего адреса тестовой последовательности.

Задающий генератор представляет собой кварцевый генератор импульсов, который вырабатывает прямоугольные импульсы с частотой повторения 2,0 МГц. Генератор

собран на двух вентилях (микросхемы К155ЛН1) и кварцевом резонаторе. Тактовая частота, которая поступает на блоки 3 и 10, может быть запрещена сигналом «Разрещение приращения адреса, Который

-ч поступает с блока 1.

Формирователь тактовых импульсов предназначен для выработки синхросигналов Ф1 и Ф2 (фиг. 3) для синхронизации работы проверяемого и эталонного микропроцессоров. Синхросигналы Ф1 и Ф2 выра5 батываются с помощью ждущих одновибра- торов.

Блок 3 адресации - двоичный счетчик обеспечивает выдачу адресных сигналов на блок постоянной памяти, в которых хранится тестовая последовательность. Блок

включает в себя три счетчика (микросхемы КМ155ИЕ7) и дещифратор (микросхема КМ155ТД4). Один из входов блока адресации является входом синхроимпульсов для приращения счетчиков, второй вход

5 «Сброс от блока 1 для сброса счетчиков в исходное состояние.

Три счетчика КМ155ИЕ7, включенные последовательно, обеспечивают адресацию памяти глубиной 4К. Так как микро0 схемы КР556РТ5 имеют глубину памяти 0,5К, для их адресации используется 9 адресных входов, которые подключаются к младшим разрядам счетчиков. Три старщих разряда счетчиков подключены к входам де- щифратора. Каждый выход дешифратора

5 подключен к входам двух микросхем КР556РТ57. Таким образом, после последовательной адресации и считывания одной пары микросхем памяти они отключаются дешифратором и подключается следующая

Q пара, которая и подлежит считыванию.

Сброс счетчиков в исходное состояние производится одновременно с установкой регистра индикации в исходное. состояние по сигналу «Сброс либо по сигналу «Окончание теста, который поступает с бло5 ка 4 и определяет конец теста.

Блок 4 постоянной памяти обеспечивает хранение и выдачу испытательных тестов, выдачу сигналов разрешения и запрета сравнения и сигнала окончания теста. Блок представляет собой 5 пар микросхем

0 типа КР556РТ5, соединенные по выходам параллельно (каждая пара обеспечивает 14 разрядов данных тестового слова), выборка и адресация которых производится последовательно с блока 3 адресации.

Формат слова проверочного теста, записанного в блок памяти, имеет следующий вид: ДО, Д1, Д2, ДЗ, Д4, Д5, Д6, Д7, УО, У1, У2, УЗ, ЗС, КТ.

ДО-Д7 - Щина данных; УО-УЗ - щи5 13632126

на управления; ЗС - сигнал запрет-к высокому уровню, а на Т-вход посту- разрешение сравнения; КТ - конец теста.пает сигнал результата сравнения. В исход- Блок 5 шинных формирователей пред-ное состояние оба триггера устанавливают- назначен для разделения информации, иду-ся сигналом «Сброс. В исходном состоящей по двунаправленной шине данныхс нии у первого триггера находится на пря- проверяемого и эталонного микропроцессора.мом выходе уровень лог. «1, у второго - Устройство построено на шинных формиро-лог.«0

вателях К589АП16 (фиг. 6). ИнформацияИндицирование сигнала «Годен проис- с блока 4 поступает на входы А шинныхходит по положительному фронту сигнала формирователей и далее (при наличииконец теста. Индицирование сигнала «Не сигнала лог. «О на входе УВ) тестовая годен и выдача сигнала прерывания нформация передается на двунаправленныйтеста проходит по положительному фронту вход/выход В, и далее на проверяемыйсигнала «Результат, и эталонный микропроцессоры. При нали-Формула изобретения чии на входе УВ сигнала лог. «1 информация с двунаправленных входов/выхо-. 1- Устройство для контроля больших дов проверяемого и эталонного микропро-интегральных схем, содержащее блок адре- цессоров поступает на выходы с шинныхсации, эталонный блок, формирователь так- формирователей и далее в блок 8 сравне-товых импульсов, блок сравнения, регистр ния. Выходы управления блока 4 подклю-индикации, задающий генератор, выход ко- чены непосредственно к управляющим вхо-торого соединен с входом синхронизации дам проверяемого эталонного блоков.20 блока адресации и с синхровходом фор- Блок сравнения построен на 8 микро-мирователя тактовых импульсов, первый вы- схемах К55СП1 - (схемах сравнения двухход которого соединен с входом синхро- 4-разрядных чисел), схеме И, D-триггеранизации блока сравнения, второй выход - (см. фиг. 4). Одноименные выходные дан-с входом синхронизация эталонного блока ные сравниваемого и эталонного блокови является выходом устройства для под- подаются на входы схемы сравнения,ключения к входу синхронизации контроли- соответствующие одному и тому же раз-руемого блока, выходная информационная ряду 4-разрядных чясел, подлежащих компа-шина эталонного блока соединена с первой рированию. Выходы, указывающие на ре-группой информационных входов блока зультат сравнения, объединены на 8-входо-сравнения, вторая группа информационных вой схеме И, выход которой подключен п входов которого является группой входов к D-входу D-триггера, на Т-вход которогоустройства для подключения к выходной с блока 10 подается сигнал стробирова-информационной шине контролируемого ния. При правильной работе эталонногоблока, выход блока сравнения сое- и проверяемого блоков триггер будет оста-динен с информационным входом ре- ваться в исходном состоянии. Если же вгистра индикации, отличающееся тем, что, момент стробирования хотя бы один из-js целью расширения области примене- компараторов указывал на несовпадениения за счет обеспечения контроля циф- информации на его входах, триггер будетровых блоков с двунаправленной перепереброшен в состояние, соответствуюшеедачей информации, оно содержит блок за- обнаружению сбоя. С выхода триггера надания режимов, блок щинных формирова- регистр индикации будет выдан сигнал «Нетелей, блок постоянной памяти, выход поля годен. К S-входу D-триггера подключена40 разрешения сравнения которого соединен с схема ИЛИ, на входы которой поступаютвходом разрешения блока сравнения, выход сигналы запрет/разрешение с блока 4поля конца теста - с входом окон- «Сброс. Сигналом «Сброс триггер можетчания теста блока задания режимов, выбыть установлен в исходное состояние.ход поля управления блока постоянной па- Сигналом «Запрет-разрешение может быть. мяти подключен к входу управления эта- блокирован отрицательный результат сравне-лонного блока и является выходом уст- ния данных, пришедших с эталонного иройс ва для подключения к входу управ- прбверяемого блоков.ления контролируемого блока, выход поля Регистр индикации (см. фиг. 5) построенданных блока постоянной памяти соединен на микросхеме К155ТМ2, включающей вс информационным входом блока щинных себя 2 D-триггера. Один из триггеров о формирователей, информационные входы- предназначен для индицирования сигналавыходы блока шинных формирователей под- «Годен, другой для индицирования сигналаключены к двунаправленной щине данных «Не годен и выдачи сигнала «Прерыва-эталонного блока и к входам-выходам ние теста на блок 1. На О-вход тригге-устройства для подключения к двунаправ- ра индицирующего «Годен поступает сиг-ленной шине данных контролируемого блока, нал, указывающий результат сравнения55 выход приема эталонного блока соединен с с блока 8, на его Т-вход поступает сиг-входом выбора направления передачи блока нал «Конец теста, D-вход второго тригге-шинных формирователей, первая и вторая ра индицирующего «Не годен подключенгруппы информационных выходов которого

соединены соответственно с третьей и четвертой группами информационных входов блока сравнения, выход пуска блока задания режимов соединен с входом пуска задающего генератора, выход конца теста блока задания режимов соединен с входом синхронизации регистра индикации, выход разряда прерывания теста которого соединен с соответствующим входом блока задания режимов, вход сброса устройства соединен С соответствующими входами блока сравнения, регистра индикации и блока задания режимов, выход сброса блока задания режимов соединен с входом сброса блока адресации, выход которого соединен с адресным входом блока постоянной памяти, выходы пуска и цикла устройства подключены к соответствующим входам блока задания режимов.

2. Устройство по п. 1, отличающееся тем, что блок задания режимов содержит

два триггера и три элемента И, причем первые входы первого и второго элементов И подключены к входу окончания теста блока задания режимов, вход сброса

блока задания режимов подключен к S-входу первого триггера, к второму входу первого элемента И и первому входу третьего элемента И, выход которого соединен с S-входом второго триггера, выход которого соединен с вторым входом вто- рого элемента И, выход которого является выходом конца теста блока задания режимов, входы пуска и цикла блока задания режимов подключены к R-входам соответственно первого и второго триггеров, выход первого элемента И и инверсный выход первого триггера являются соответственно выходом сброса и выходом пуска блока задания режимов, второй вход третьего элемента И является входом прерывания теста блока задания режимов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для контроля больших интегральных схем | 1988 |

|

SU1672454A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1290333A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

Изобретение относится к цифровой вычислительной технике, в частности к устройствам для проверки больших интегральных схем (БИС), в том числе БИС микропроцессорных наборов. Целью изобретения является расширение области применения за счет обеспечения возможности контроля цифровых блоков с двунаправленной передачей информации. Устройство для контроля больших интегральных схем содержит блок 1 задания режимов, задающий генератор 2, блок 3 адресации, блок 4 постоянной памяти, блок 5 шинных формирователей, контролируемый блок 6, эталонный блок 7, блок 8 сравнения, регистр 9 индикации, формирователь 10 тактовых импульсов. 1 з. п. ф-лы, 5 ил. (Л 05 со 1чЭ ГЧЭ

„ Окончание теста

с ПЗУ (If)

„ Прерыбоние теста (Sm98,

16

Б

к 155 л т

D

, ,,OKOHWHue

Фиг. 2

(Pi

Фиг. 3

{ПЗУ) за- npim/рюреш.

Влок

ЪлокЗ

, Резу ль тат

„ Пден

шеста

Фиг. 5

Составитель Д. Ванюхин

Техред И. ВересКорректор А. Обру чар

Тираж 67 1Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.„ д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля микросхем | 1977 |

|

SU648981A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1005061A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-20—Подача