. Изобретение относится к автома- тике и -вычислительной технике и может найти применение в системах машинного анализа и обработки изображений, допускающих либо одностроч ное представление объектов, либо построчное сканирование при анализе двумерных изображений. Устройство может стать частью автоматических систем контроля и управления, использоваться в телевизионных и ради локационных следящих и распознающих системах, а также при цифровой обра ботке изображений, полученных при дистанционных исследованиях. Известно устройство для формирования признаков распознаваемых образов, содержащее приемник излучени блок определения разности сигналов, подключенный к выходам приемника излучения, и блок вычисления модуля входы которого соединены с блоком определения разности сигналов lj . В этом устройстве в качестве признаков распознаваемых образов испол зуются, во-первых, суммарная яркост изображения и,во-вторых, сумма модулей разности сигналов |23. Однако в тек случаях, когда прои ходит изменение формы изображения и изменение его положения в поле зрения (что происходит при проективных преобразованиях), характеристики изображения, определяемые данным устройством, не могут -оставаться неизменными, т.е. они не являются в аком случае признаками-инвариантами. Использование таких признаков либо в значительной степени снижает точность распознавания, либо приводит к появлению аномальных ошибок ставящих под сомнение целесообразность использования устройства. Наиболее близко к изобретению устройство, содержащее первый и второй формирователи сигналов, соединенные с сумматором, блок памяти, подключенньй через регистр к аналого-цифровому преобразователю, через первый элемент И - к генератору импульсов и через регистр считывания - к вычислительному блоку, второй ч третий элементы И, входы которых подключены к дешифратору, соединенному с управляющим блоком, и к генератору импульсов и к делителю частоты соответственно, первый счетчик, соединенный с выходами второго 5i и третьего элементов И, с входами , блока памяти-и блока управления, выходы которого через группу блоков памяти подключены к другим входам вычислительного блока 2 Данное устройство имеет недостаточно высокую надежность распознавания по сформированным признакам. Цель изобретения - повьш1ение надежности распознавания. Поставленная цель достигается тем, что в устройство, содержащее сумматор, вход которого соединен с первым формирователем сигналов, а выход подключен к второму формирователю сигналов, со(единенному с одним входом аналого-цифрового преобразователя, другой .вход которого . подключен к выходупервого элемента И, а выход соединен с одним входом регистра, другой вход которого подключен к выходу первого элемента И, а выход соединен с одним входом блока памяти,другие входы которого подключены к выходам первого элемента И и первого счетчика, генератор импульсов, соединенньй с делителем частоты и с одними входами первого и второго элементов И, другие входы которых подключены к дешифратору, третий элемент И, один вход которого соединен с делителем частоты, другой подключен к дешифратору, а выход соединен с входом первого счетчика, подключенным к выходу второго элемента И, первую группу блоков памяти, входы которых соединены с блоком памяти, введены второй счетчик, один вход которого является входом устройства, другой подключен к выходу первого счетчика, а выход соединен с дешифратором, вторую группу блоков памяти, входы которых подключены к выходу первого счетчика, первая группа умножителей, одни входы которых соединены с соответствующими блоками памяти первой группы, четвертый элемент И, входы которого соединены с.делителем частоты и с дешифратором, первая группа интеграторов, входы которых подклюнены к выходу четвертого элемента И и к соответствующим блокам па-. мяти первой группы , а выходы являются первой группой выходов устройства, вторая группа умножителей, входы которых соединены с выходом соответствующего блока памяти первой группы

и выходами соответствующих блоков памяти второй группы, и вторая группа интеграторов, входы которых подключены к соответствующим умножителям первой и второй групп и к выходу 5 четвертого эл.емента-И, а выходы являются второй группой выходов устройства, при этом другой вход одного умножителя первой группы соединен с выходом соответствующего блока Ю памяти второй группы,-а другие входы других умножителей первой группы соединены с выходом первого счетчика .

I

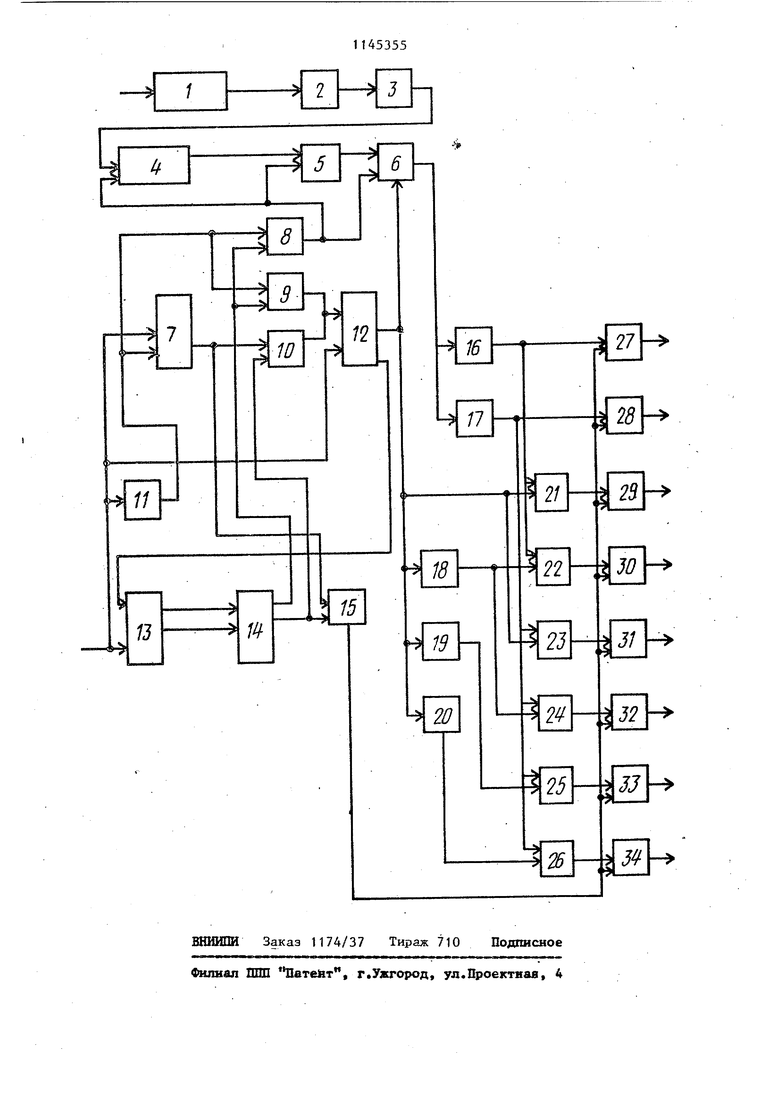

На чертеже представлена блок-схе- 15 ма предложенного устройства.

Устройство включает первьй формирователь 1 сигнала из сигналов изоб- , ражения, поступающих на вход устройства, сумматор 2, предназначенный 20 для определения, разности сигналов, второй формирователь 3 сигнала, предназначенньй для формирования сигнала, пропорционального модулю сигнала, полученного с выхода сум- 25 матора 2, аналого-цифровой преобразователь 4 (АЦП), регистр 5, блок 6 памяти, выполненньйл например, в виде оперативного запоминающего устройства, делитель 7 частоты, первый 8, эо второй 9 и третий 10 элементы И, генератор 11 импульсов, первьш 12 и второй 13.счетчики, дешифратор 14, четвертьш элемент И 15, первая 16-17 и вторая 18, 19 и 20 группы блоков ,, памяти, выполненные, например, в виде постоянных запоминающих устройств, первая 21-23 и вторая 24-26 группы умножителей, первая 27-28 и вторая 29-34 группы интеграторов, до

В формирователе 1 происходит преобразование изображения в электрический сигнал. Сумматор 2 предназначен ДЛЯ определения разности сигналов яркости. В формирователе 3 45 определяется модуль разности сигналов яркости. АЦП 4 предназначен для преобразования значений модуля разности сигналов в цифровую форму. Регистр 5 предназначен для хранения JQ и передачи в блок 6 значений модуля разности сигналов, где они запоминаются..

Генератор 11 импульсов вырабатывает последовательность импульсов, 55 которая через элемент И 8 управляет работой АЦП 4, регистра 5, записью данных в блок 6, а через элемент И

9 - работой счетчика 12, предназначенного для формирования адреса, счетчика 13, служащего для управления входами дешифратора 1:4.

Делитель 7 частоты предназначен для выработки последовательности импульсов, которая через элемент И 1 управляет работой счетчиков 12 и 13, дешифратора 14 и записью информации в цифровых интеграторах. 27-34.

В зависимости от состояния выхо дов дешифратора 14 переключение счетчика 12 осуществляется сигналами, проходящими на вход счетчика 12 чере элементы И 9 или 10.

Временные интервалы управляющих сигналов выбираются с учетом полного окончания переходных процессов и пояления установивщихся кодов на входах соответствующих элементов устройства

Блок 16 предназначен для,возведения модуля разности сигналов в квадрат, блок 17 - в куб, блоки 18-20 предназначены длА возведения в квадрат, третью и четвертую степень .значений координаты. В эти блоки записываются таблицы значений соответствующих функций. В этих блоках код аргумента функции поступает на адресные входы. Через некоторое время, определяемое типом ПЗУ, на выходе появляется числовое значение функции которое было занесено заранее, на этапе изготовления этого ПЗУ.

Умножители 21-25 предназначены для вычисления произведений.

. Блоки 27-34 являются цифровыми интеграторами, предназначенными для вычисления сумм.

Работа предлагаемого устройства состоит из двух циклов.

1.Прием изображения, определение разности сигналов, вычисление модуля разности сигналов, аналогоцифровое преобразование значений модуля разности сигналов и запоминание значений кодов.

2.Считывание информации из первого блока памяти, определение признаков изображения.

В первом цикле изображение, характеризуемое некоторой функцией распределения яркости и подвергнутое действие группы проективных преобразователей, принимается приемником излучения.

Сигнал Пуск, поступающий на первый вход счетчика 13, устанавли5

вает в исходное состояние счетчики 12 и 13. Комбинация разрядов счетчика 13 поступает на дешифратор 14 с нулевого выхода которого появляется разрешающийсигнал-.

При поступлении сигнала Начало строки на первый вход счетчика 13 генератором 11 импульсов вырабатывается последовательность импульсов, которая проходит через элемент И 8 на управляющие входы А1ДП 4 регистра 5 и на вход Запись блока 6.

Последовательно для всех точек изображения в плоскости приемника излучения в заданных направлениях для кшкдых двух соседних элементов разложения определяется разность сигналов в блоке 2, вычисляется модуль разности и сигнал поступает на вход ЛЦП, где на каждом периоде частоты происходит аналого-цифрово преобразование информации, запись информации в регистре 5 и.затем в блоке 6 по адресу, который формируется счетчиком 12 при поступлении на его .вход, через элемент И 9 импульсов.

После перебора всех значений адреса с выхода счетчика 12 появляется сигнал переноса, который поступает на вход счетчик-а режимов 13, изменяет его состояние на 01 и переводит работу устройства во второй цикл.

Во втором цикле активируется единичный выход дешифратора 14, который разрешает прохождение импульсов с делителя 7 частоты через элемент И 10 на счетчик 12 и через элемент И 15 на первые входы цртфровьпс пнтеграторов для управления записью информации. Работа АЦП 4 и

453556.

регистра 5 блокируется, блок 6 работает в режиме считывания. С его выхода выдается последовательность значений модуля разности сигналов, 5 ас выхода 12 вьщается последовательность значений координат. Полученные значения поступают на входы блоков 16 и 17, с выходов которых снимаются квадрат {ПЗУ 16) и куб (ПЗУ 17) значений модуля разности сигналов. Значения кодов из счетчика 12 поступают на входы блоков 18-20, с вьпсодом которых снимаются квадрат (ПЗУ 18),-куб (ПЗУ 19)

5 и четвертая степень (ПЗУ 20) значений координаты каждого элемента разложения .

С выхода блока 16 коды поступают на первые входы умножителей 21, 22

0 и на первый вход цифрового интегратора 27. С выхода блока 17 коды поступают на первые входы умножителей 23-26 и на первый вход цифрового интегратора 28. Коды с второго выхода счетчика 12 поступают на вторые входы умножителей 21и 23. С выходов блока 18 коды поступают на вторые входы умножителей .22 и 24. С выхода блока 19 коды-поступают.

0 на второй вход умножителя 25, а с вьгхода блока 20 коды - на второй вход умножителя 26.

С выходов умножителей 21-26 сигналы поступают на первые входы цифровых интеграторов 29-34.

После проведения всех тактов суммирования на выходах цифровых инте граторов 27-34 формируются значения признаков изображения.

0 Введение в устройство новых узлов и элементов, а Taitace новых конструктивных связей существенно повышает надежность распознавания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нормализации изображений объектов | 1984 |

|

SU1211771A1 |

| Устройство для формирования признаков распознаваемых образов | 1986 |

|

SU1328830A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭТАЛОННОЙ КАРТЫ МЕСТНОСТИ ДЛЯ НАВИГАЦИОННЫХ СИСТЕМ | 1992 |

|

RU2022355C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Дискретный регулятор уровня | 1984 |

|

SU1262461A1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2139640C1 |

| СЕЛЕКТИВНОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОДНОФАЗНЫХ ЗАМЫКАНИЙ В КАБЕЛЬНЫХ ЛИНИЯХ | 2006 |

|

RU2316010C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРИЗНАКОВ РАСПОЗНАВАЕМЫХ ОБРАЗОВ, содержащее сумматор, вход которого соединен с первым формирователем сигналов, а выход подключен к второрому формирователю сигналов, соединенному с одним входом аналогового преобразователя, другой вход которого подключен к выходу первого элемента И, а выход соединен с одним входом регистра, другой вход которого подключен к выходу первого элемента И, а выход соединен с одним входом блока памяти, другие входы которого подключены к выходам первого, элемента И и первого счетчика, генератор и fflyльcoв, соединенный .с делителем частоты и с одними входами первого и второго элементов И, другие входы которых подключены к дешифратору, третий элемент И, один вход которого соединен с делителем частоты, другой подключен к дешифратору, а выход соединен с входом первого счетчика, подключенным к выходу второго элемента И, первую группу блоков памяти, входы которых соединены с блоком памяти, отличаю тем, что, с целью повышения надежности распознавания, оно содержит Второй счетчик, один вход которого является входом устройства, другой подключен к выходу первого счетчика, а выход соединен с дешифратором, вторую группу блоков памяти, входы которых подключены к выходу первого счетчика, первую группу умножителей, одни входы которых соединены с соответствующими блоками памяти первой группы, четвертьй элемент И, входы которого соединены с делисл телем частоты и с дешифратором,первую группу интеграторов, входы которых подключены к выходу четвертого элемента Ник соответствующим блокам памяти первой группы, а выходы являются первой группой выходов устройства, вторую группу умножителей, входы которых соединены с выхо4 дом соответствующего блока памяти ел первой группы и выходами соответст00 вующих блоков памяти второй группы, ел и вторую группу интеграторов, входы о которых подключены к соответствующим умножителям первой и второй группы и к выходу четвертого элемента И, а выходы являются второй группой выходов устройства, при этом другой вход одного умножителя первой группы соединен с выходом соответствующего блока памяти второй группы, адругие входы других умножителей п&рвой группы соединены с выходом первого счетчика.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Линейный вибрационный двигатель | 1976 |

|

SU614478A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3863218, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| I | |||

Авторы

Даты

1985-03-15—Публикация

1983-11-21—Подача