(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU898509A1 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU746744A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875470A1 |

| Постоянное запоминающее устройство с самоконтролем | 1985 |

|

SU1285538A1 |

| Устройство для контроля цепей коррекции ошибок | 1988 |

|

SU1647653A1 |

1

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с самоконтролем, которое содержит накопитель, регистр адреса, блоки кодирования и декодирования, связанные с накопителем, входной и выходной регистры, блоки схем И к ИЛИ 11/

Недостатком этого устройства является невысокая надежность.

Наиболее близким техническим решением к изобретению является запомннаюшее устройство, содержащее накопитель, подключенный через адресные форвлнрователи и вентили к регастру адреса и через разрядные формирователи Н вентили - к выходу блока кодирования и входу блока декодирования, подсоединенному к блоку управления и выходному регистру, входному регистру н блоку схем И; схему п-разрядного сравнения, входы которой подключены к выходам входного и выходного регистра, а выходы - к блоку управления и блоку схем ИЛИ, к которому подсоединен выход входного регистра н выход блока схем И; блок схем ИЛИ, к которому подключены

.входной регистр н информационные шинь, н выход которого соединен со ..ходом блока кодирования (2.

Недостатками этого устройства являютс малая эффективная емкость и низкая надежность, так как при возникновении многократных ошибок, превышающих корректирующую способность применяемого кода, они исправляются неверно.

Цель нзобретення -оповышение надежности и эффективной емкости устрстства.

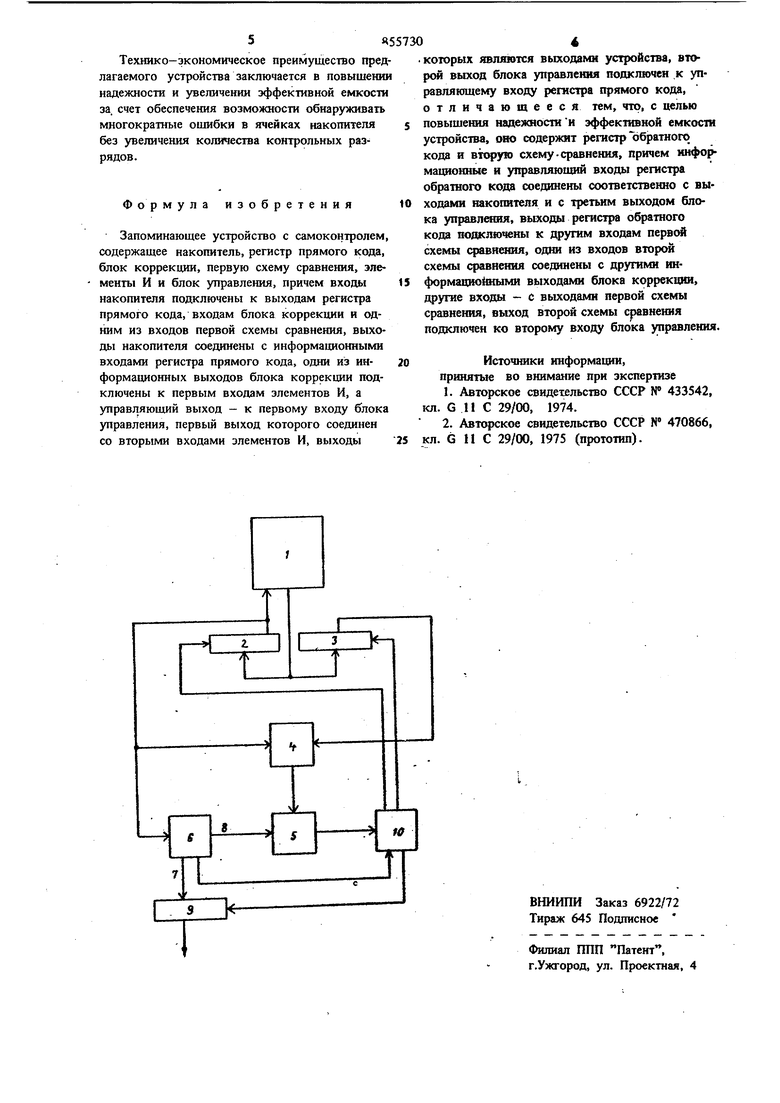

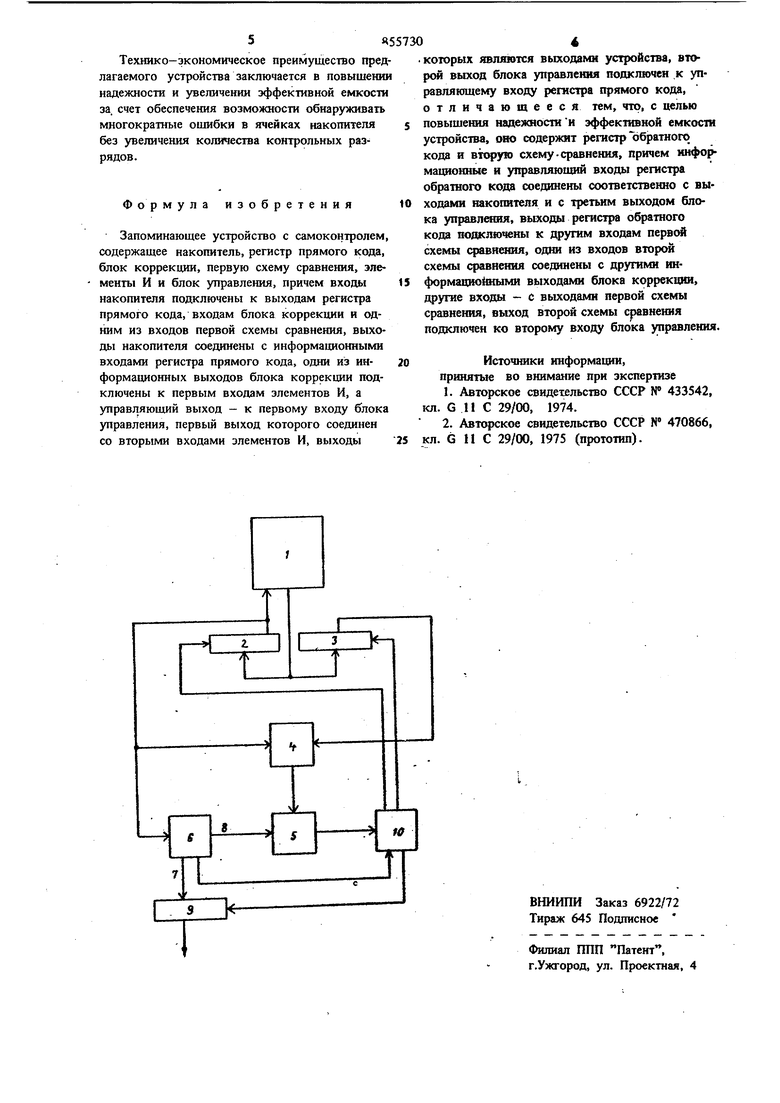

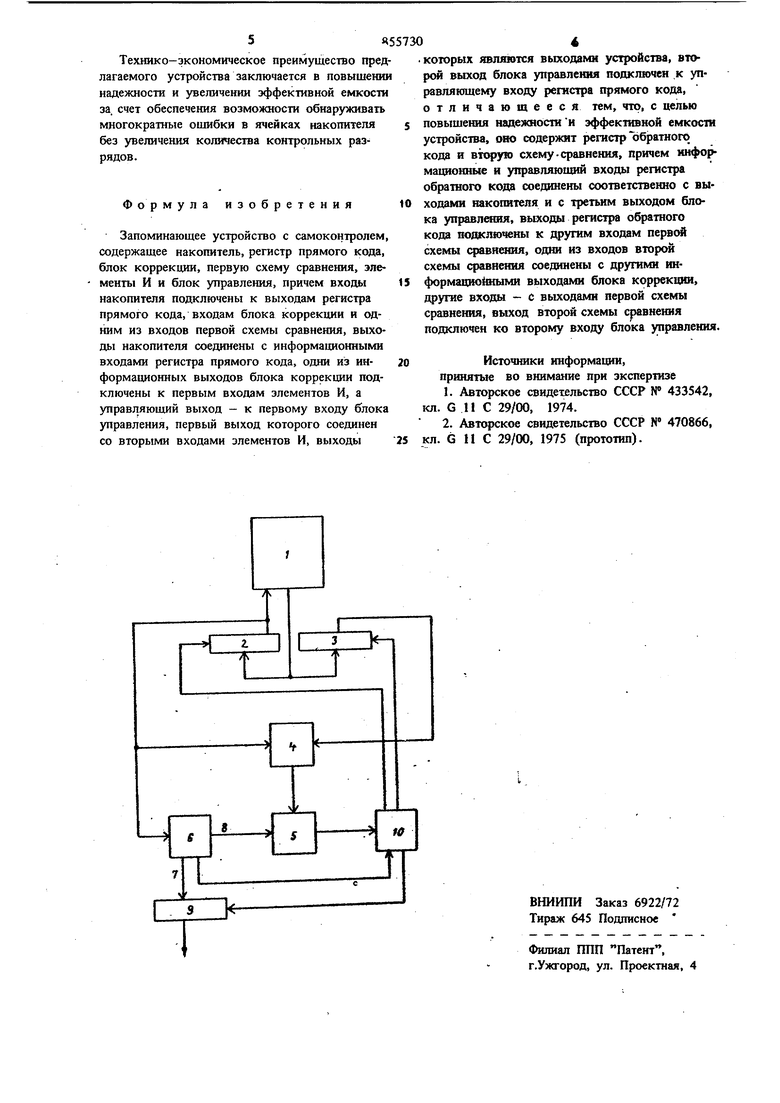

Поставленная цель достигается тем, что в запокшнающее устройство с самоконтролем, содержащее накопитель, регистр прямого кода, блок коррекции, первую схему сравнения, элементы И и блок управления, причем входы накопителя подключены к выходам регистра прямого кода, входам блока коррекции и одним нз входов первой схемы сравнения, выходы накопителя соединены с информационными входами регистра прямого кода, одни из информационных выходов блока коррекции подключены к первым входам элементов И, а управляющий выход - к первому входу 38 блока управления, первый выход которого соединен со вторыми входами элементов И, выходы которых являются выходами устройства, второй выход блока управления подключен к управляющему входу регистра прямого кода, введены регистр обратного кода и вторая схема сравнения, причем информационные и управляющий входы регистра обратного кода соединены соответственно с выходами накопите ля и с третьим выходом блока управления, выходы регистра обратного кода подключены к дрзтнм входам первой схемы сравнения, одни из входов второй схемы сравнения соеди нены с другими информационными выходами блока коррекции, другие входы - с выходами первой схемы сравнения, выход второй схемы сравнения подключен ко второму входу блока управления. На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит накопитель 1, регистр прямого кода, регистр 3 обратного кода, перву 4 и вторую S схемы сравнения, блок 6 коррек ции с информационнь 1ми выходами 7 и 8, элементы И 9 и блок 10 управления. Входы накопителя 1 подключены к выходам регистра 2 прямого кода, входам блока 6 коррекций и одним из входов первой схемы 4 сравнения. Выходы накопителя 1 соединены с информацион ными входами регистра 2 прямого кода. Одни из информационных выходов 7 блока 6 коррекции подключены к первым входам элементов И 9, а управляющий выход - к первому входу блока 10 управленид, первый выход которого соединен со втррыми входами злементов И 9, выходы которых являются выходами устройства. Второй выход блока 10 управления подключен к управляющему входу регистра 2 прямого кода. Входы регистра 3 обратного кода соединены соответственно с выходами накопителя 1 и с третьим выходом блока 10 управления. Выхо ды регистра 3 обратного кода подключены к другим входам первой схемы 4 сравнения. Одн из входов второй схемы 5 сравнения соединены с другими информационными выходами 8 блок 6 коррекции, другие - с выходами первой схемы 4 сравнения. Выход второй схемы сравнения подключен ко второму входу блока 10 управления. Устройство работает лбразом. При решшзации режима чтения на управляющий вход регистра 2 прямого кода со второго выхода блока 10 управления подается разре щающий сигнал, в результате чего кодовое слово считывается с ячейки накопителя 1 на регистр 2 прямого кода, с выхода которого оно поступает на блок 6 коррекции. Если в процес се чтения оншбки не возникают, то контрольые разряды покажут отсутствие ощибок (об этом свидетельствует сигнал на управляющем выходе блока 6 коррекции, подключенном к ервому входу блока 10 управления, и блок 10 управления выдает разрешающий сигнал, по которому считанное из накопителя 1 число с нформационного выхода 7 блока 6 коррекдаи ерез элементы И 9 поступает на выход устойства. Если в режиме -хранения и чтения произошли ошибки, то при декодировании считанного слова в блоке 6 коррекщга контрольные разряды покажут, в каких именно разрядах слова они имеются. Затем производится коррекшм .этих ошибок {например, инвертирование ошибочных разрядов). При наличии ошибок сигнал на первом выходе блока 10 управления запрещает прохождение числа на выход устройства, кодовое слово с регистра 2 прямого кода записывается обратным кодом в накопитель 1 в ту же ячейку, а затем считывается по разрешающему сигналу на третьем выходе блока 10 управления в регистр 3 обратного кода. После этого коды числа с регистров 2 и 3 поступают на первую схему 4 сравнения, которая поразрядно сравнивает их и фиксирует номера разрядов, в которых прямой и обратной коды числа совпадают, следовательно, в этих разрядах ячейка накопителя 1 имеет отказы. Номера разрядов, в которых имеются ошибки, определенные при декодировании, с выхода 8 блока 6 коррекции поступают на вторую схему 5 сравнения, где последовательно сравниваются с каждым из элементов множества номеров отказавших разрядов, которые поступают с выхода первой схемы 4 сравнения, и производатся определение попадания множества разрядов, в которых осуществлена коррекция, в множество отказавших разрядов. Если имеет место попадание, о чем свидетельствует сигнал на выходе первой схемы 5 сравнения, то блок 10 управления выдает на первый выход разрешающий сигнал, по которому скорректированное кодовое слово с информационного выхода 7 блока 6 коррекции через элементы И 9 поступает на йыход устройства. В случае непопадания сигнал на первом выходе блока 10 управления запрещает постуошениа считанного слова на выход устройства. Это означает, что произошла многократная ошибка, превышающая корректирующую возможность кода, и номера разрядов, подлежащих коррекции, определены при декодировании неверно. Обнаружить зту ситуацию удается за счет определения множества отказавюих разрядов тл определения: попадания в это множество номеров содержащих ошибки разрядов, опредеЛешшх при декодировании.

Авторы

Даты

1981-08-15—Публикация

1979-11-16—Подача