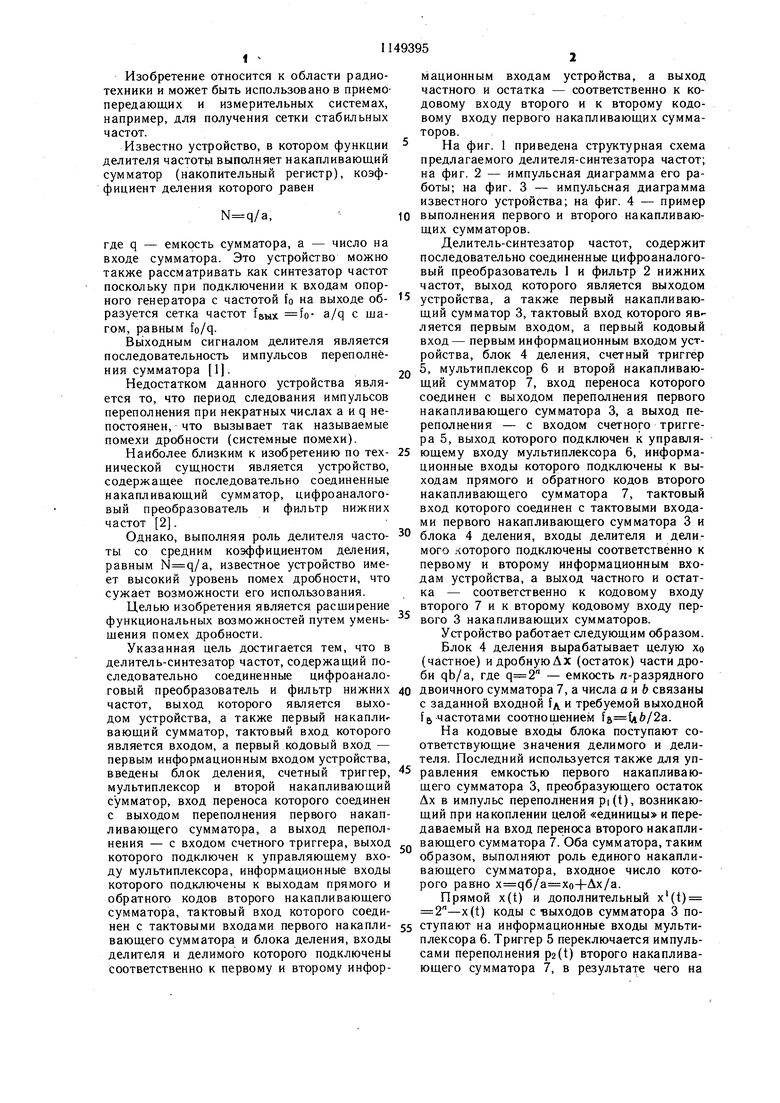

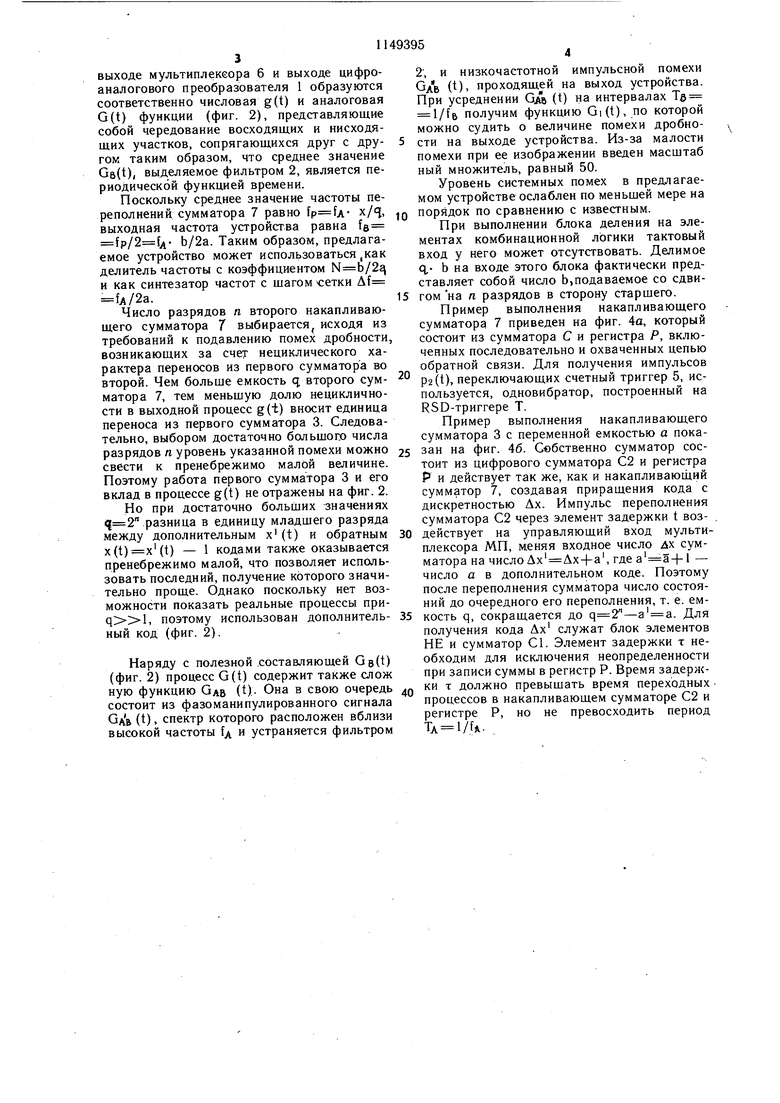

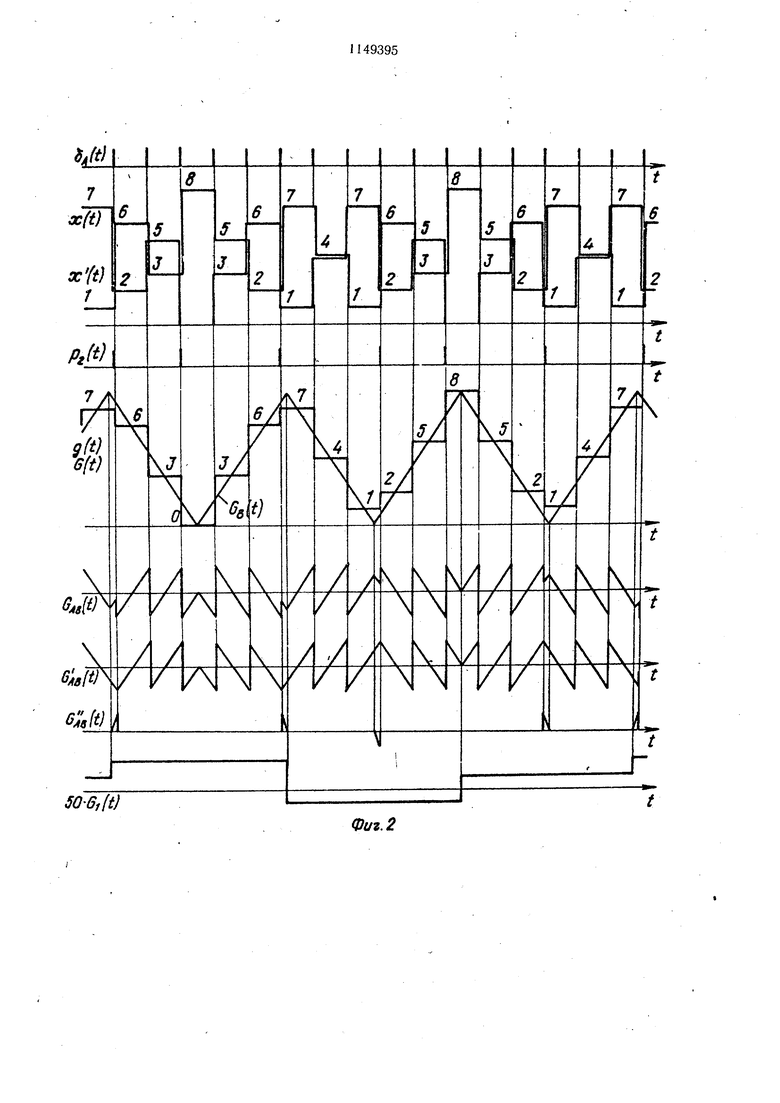

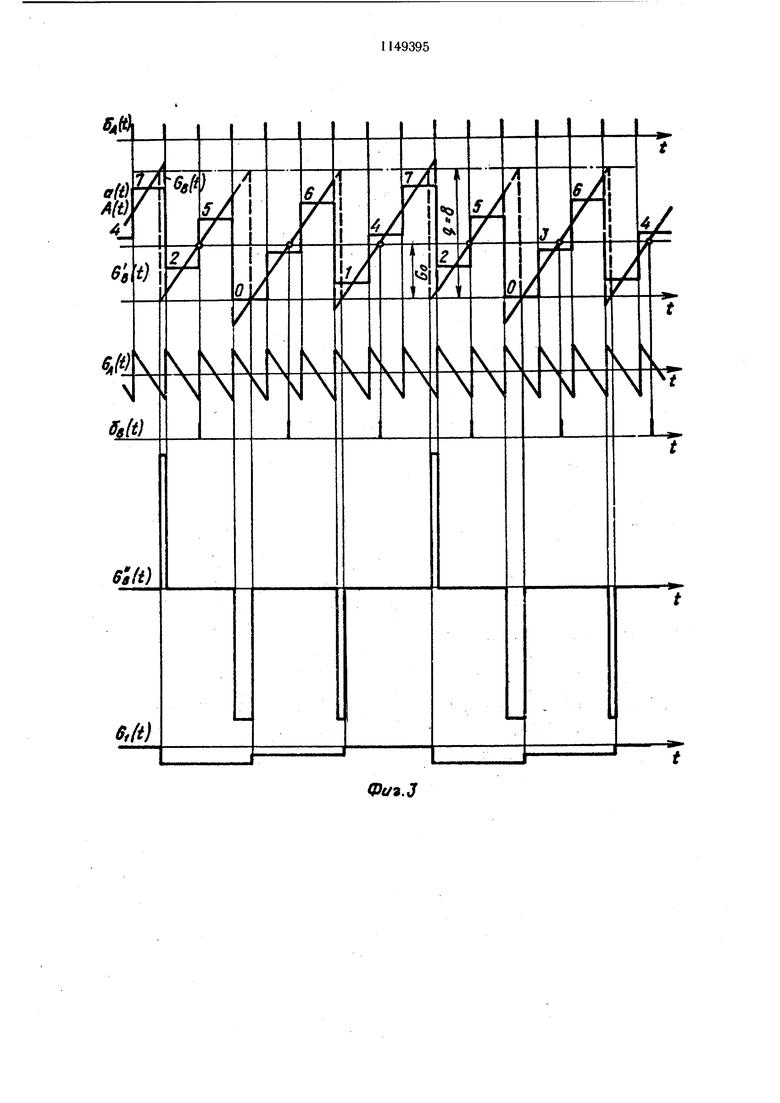

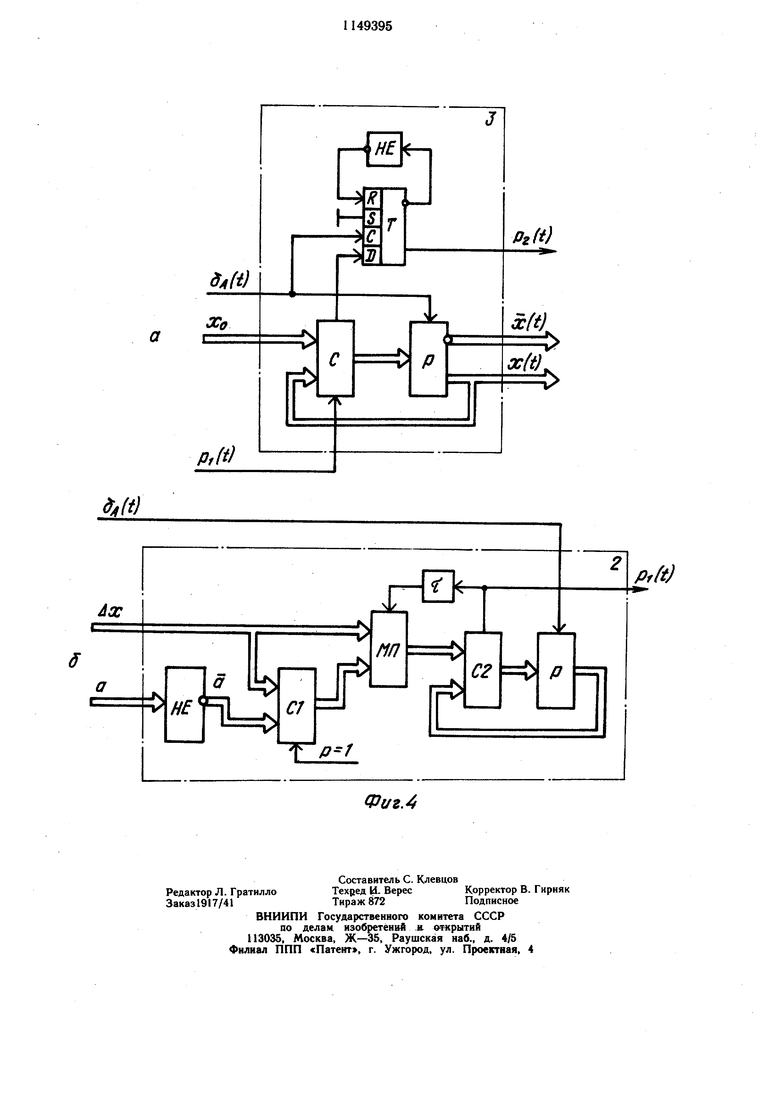

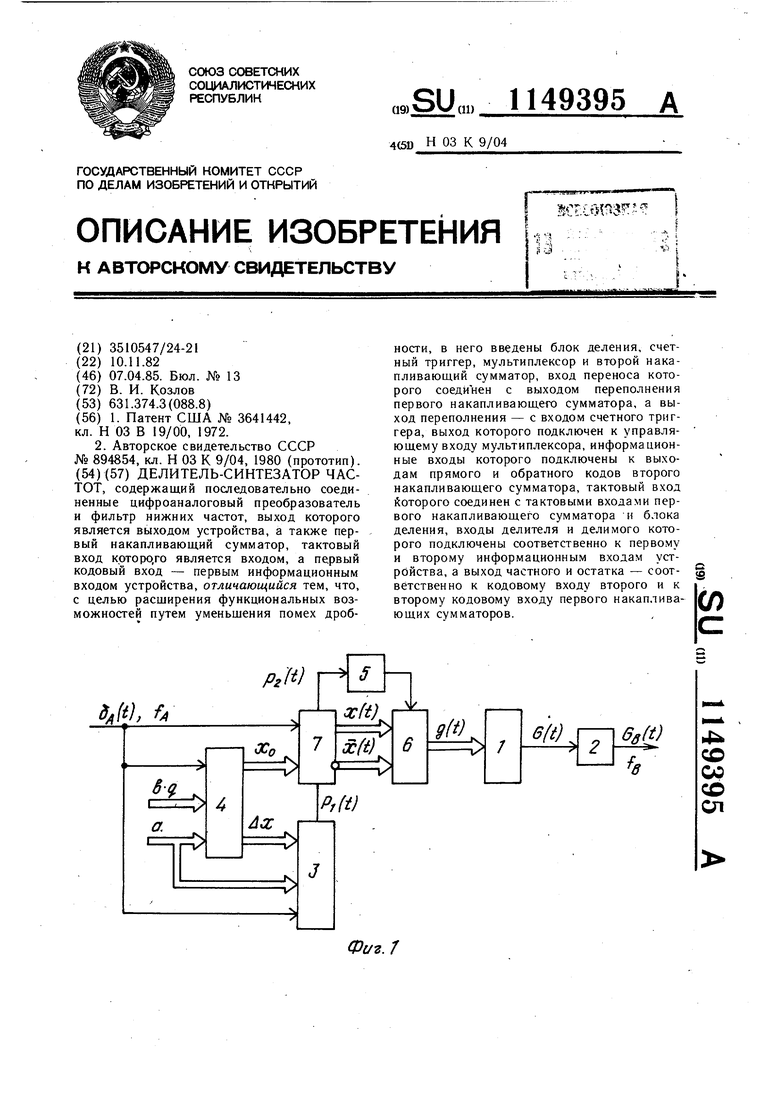

Фи.7 Изобретение относится к области радиотехники и может быть использовано в приемопередающих и измерительных системах, например, для получения сетки стабильных частот. Известно устройство, в котором функции делителя частоть выполняет накапливающий сумматор (накопительный регистр), коэффициент деления которого равен , где q - емкость сумматора, а - число на входе сумматора. Это устройство можно также рассматривать как синтезатор частот поскольку при подключении к входам опорного генератора с частотой fo на выходе образуется сетка частот fsux fo- a/q с щагом, равным fo/q. Вь1ходным сигналом делителя является последовательность импульсов переполнения сумматора 1. Недостатком данного устройства является то, что период следования импульсов переполнения при некратных числах а и q непостоянен, что вызывает так называемые помехи дробности (системные помехи). Наиболее близким к изобретению по технической сущности является устройство, содержащее последовательно соединенные накапливающий сумматор, цифроаналоговый преобразователь и фильтр нижних частот 2. Однако, выполняя роль делителя частоты со средним коэффициентом деления, равным , известное устройство имеет высокий уровень помех дробности, что сужает возможности его использования. Целью изобретения является расщирение функциональных возможностей путем уменьшения помех дробности. Указанная цель достигается тем, что в делитель-синтезатор частот, содержащий последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом устройства, а также первый накапли вающий сумматор, тактовый вход которого является входом, а первый кодовый вход - первым информационным входом устройства, введены блок деления, счетный триггер, мультиплексор и второй накапливающий сумматор, вход переноса которого соединен с выходом переполнения первого накапливающего сумматора, а выход переполнения - с входом счетного триггера, выход которого подключен к управляющему входу мультиплексора, информационные входы которого подключены к выходам прямого и обратного кодов второго накапливающего сумматора, тактовый вход которого соединен с тактовыми входами первого накапливающего сумматора и блока деления, входы делителя и делимого которого подключены соответственно к первому и второму информационным входам устройства, а выход частного и остатка - соответственно к кодовому входу второго и к второму кодовому входу первого накапливающих сумматоров. На фиг. 1 приведена структурная схема предлагаемого делителя-синтезатора частот; на фиг. 2 - импульсная диаграмма его работы; на фиг. 3 - импульсная диаграмма известного устройства; на фиг. 4 - пример выполнения первого и второго накапливающих сумматоров. Делитель-синтезатор частот, содержит последовательно соединенные цифроаналоговый преобразователь 1 и фильтр 2 нижних частот, выход которого является выходом устройства, а также первый накапливающий сумматор 3, тактовый вход которого является первым входом, а первый кодовый вход- первым информационным входом устройства, блок 4 деления, счетный триггер 5, мультиплексор 6 и второй накапливающий сумматор 7, вход переноса которого соединен с выходом переполнения первого накапливающего сумматора 3, а выход переполнения - с входом счетного триггера 5, выход которого подключен к управляющему входу мультиплексора 6, информационные входы которого подключены к выходам прямого и обратного кодов второго накапливающего сумматора 7, тактовый вход которого соединен с тактовыми входами первого накапливающего сумматора 3 и блока 4 деления, входы делителя и делимого которого подключены соответственно к первому и второму информационным входам устройства, а выход частного и остатка - соответственно к кодовому входу второго 7 и к второму кодовому входу первого 3 накапливающих сумматоров. Устройство работает следующим образом. Блок 4 деления вырабатывает целую хо (частное) и дробную Ах (остаток) части дроби qb/a, где - емкость «-разрядного двоичного сумматора 7, а числа аи & связаны с заданной входной ГА и требуемой выходной fb частотами соотношением в иЬ/2а. На кодовые входы блока поступают соответствующие значения делимого и делителя. Последний используется также для управления емкостью первого накапливающего сумматора 3, преобразующего остаток Ах в импульс переполнения pi(t), возникающий при накоплении целой «единицы и передаваемый на вход переноса второго накапливающего сумматора 7. Оба сумматора, таким образом, выполняют роль единого накапливающего сумматора, входное число которого равно x q6/a xo+Ax/a. Прямой x(t) и дополнительный x(t) (t) коды с-выходов сумматора 3 поступают на информационные входы мультиплексора 6. Триггер 5 переключается импульсами переполнения p2(t) второго накапливающего сумматора 7, в результате чего на выходе мультиплексора 6 и выходе цифроаналогового преобразователя 1 образуются соответственно числовая g(t) и аналоговая G(t) функции (фиг. 2), представляющие собой чередование восходящих и нисходящих участков, сопрягающихся друг с другом таким образом, что среднее значение Ge(t), выделяемое фильтром 2, является периодической функцией времени. Поскольку среднее значение частоты переполнений сумматора 7 равно х/1, выходная частота устройства равна fe Ь/2а. Таким образом, предлагаемое устройство может использоваться ,как делитель частоты с коэффициентом и как синтезатор частот с щагом сетки Af {А/2а. Число разрядов п второго накапливающего сумматора 7 выбирается исходя из требований к подавлению помех дробности, возникающих за счет нециклического характера переносов из первого сумматора во второй. Чем больше емкость q. второго сумматора 7, тем меньщую долю нецикличности в выходной процесс g(t) вносит единица переноса из первого сумматора 3. Следовательно, выбором достаточно больщого числа разрядов п уровень указанной помехи можно свести к пренебрежимо малой величине. Поэтому работа первого сумматора 3 и его вклад в процессе g(t) не отражены на фиг. 2. Но при достаточно больщих значениях q 2 разница в единицу младшего разряда между дополнительным х (t) и обратным x(t)x(t) - 1 кодами также оказывается пренебрежимо малой, что позволяет использовать последний, получение которого значительно проще. Однако поскольку нет возможности показать реальные процессы приq l, поэтому использован дополнительный код (фиг. 2). Наряду с полезной .составляющей Ов() (фиг. 2) процесс G(t) содержит также слож ную функцию GAB (t).- Она в свою очередь состоит из фазоманипулированного сигнала GAU (t), спектр которого расположен вблизи высокой частоты f и устраняется фильтром 2, и низкочастотной импульсной помехи (t) проходящей на выход устройства. При усреднении Оде (t) на интервалах Те 1/Гб получим функцию Gi(t), по которой можно судить о величине помехи дробности на выходе устройства. Из-за малости помехи при ее изображении введен масщтаб ный множитель, равный 50. Уровень системных помех в предлагаемом устройстве ослаблен по меньщей мере на порядок по сравнению с известным. При выполнении блока деления на элементах комбинационной логики тактовый вход у него может отсутствовать. Делимое q,- b на входе этого блока фактически представляет собой число Ь,подаваемое со сдвигомна п разрядов в сторону старщего. Пример выполнения накапливающего сумматора 7 приведен на фиг. 4а, который состоит из сумматора С и регистра Р, включенных последовательно и охваченных цепью обратной связи. Для получения импульсов p2(t), переключающих счетный триггер 5, используется, одновибратор, построенный на RSD-триггере Т. Пример выполнения накапливающего сумматора 3 с переменной емкостью а показан на фиг. 46. Собственно сумматор состоит из цифрового сумматора С2 и регистра Р и действует так же, как и накапливаюихий сумматор 7, создавая приращения кода с дискретностью Ах. Импульс переполнения сумматора С2 через элемент задержки t воздействует на управляющий вход мультиплексора МП, меняя входное число лх сумматора на число Дх Ах-|--а, где - число а в дополнительном коде. Поэтому после переполнения сумматора число состояний до очередного его переполнения, т. е. емкость q, сокращается до а. Для получения кода Ах служат блок элементов НЕ и сумматор С1. Элемент задержки т необходим для исключения неопределенности при записи суммы в регистр Р. Время задерж должно превыщать время переходных процессов в накапливающем сумматоре С2 и регистре Р, НО не превосходить период ).

Фиг. 2

Фи,3

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| Синтезатор частот | 1985 |

|

SU1254576A1 |

| Синтезатор частот | 1988 |

|

SU1552344A1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| Делитель частоты | 1983 |

|

SU1162014A1 |

| Синтезатор частот | 1987 |

|

SU1610599A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

ДЕЛИТЕЛЬ-СИНТЕЗАТОР ЧАСТОТ, содержащий последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом устройства, а также первый накапливающий сумматор, тактовый вход которого является входом, а первый кодовый вход - первым информационным входом устройства, отличающийся тем, что, с целью расширения функциональных возможностей путем уменьшения помех дробности, в него введены блок деления, счетный триггер, мультиплексор и второй накапливающий сумматор, вход переноса которого соединен с выходом переполнения первого накапливающего сумматора, а выход переполнения - с входом счетного триггера, выход которого подключен к управляющему входу мультиплексора, информационные входы которого подключены к выходам прямого и обратного кодов второго накапливающего сумматора, тактовый вход i OTOporo соединен с тактовыми входами первого накапливающего сумматора н блока деления, входы делителя и делимого которого подключены соответственно к первому и второму информационным входам устi ройства, а выход частного и остатка - соответственно к кодовому входу второго и к СЛ второму кодовому входу первого накапливающих сумматоров. 4 ;о со со ел

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3641442, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой фазовый детектор | 1980 |

|

SU894854A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-07—Публикация

1982-11-10—Подача