Р I

4:

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Устройство для формирования импульсных последовательностей с заданным законом изменения фазы | 1979 |

|

SU862134A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ, -содержащий последовательно соединенные цифроаналрговый преобразователь и фильтр, выход которого является выходом устройства, а также накопительный регистр, тактовый вход .которого является тактовым входом устройства, входы -задания соответственно емкости регистра и дискретности приращения выходного числа являются первым и вторым информационными входами устройства о т л ичающийся тем, что, с целью уменьшения паразитной фазовой моду ляции выходного сигналаJ в него введены мультиплексор и преобразователь кода, выход которого соединен с.первым входом мультиплексора, выход которого соединен с входом цифроаналогового преобразователя, второй вход - с выходом накопительного регистра и первым входом лреобразователя кода, второй вход которого соединен с первым информационным входом устройства, а также счетный триггер, вход которого,соединен с (Л выходом переполнения накопительного регистра, а выход - со входом управления мультиплексора.

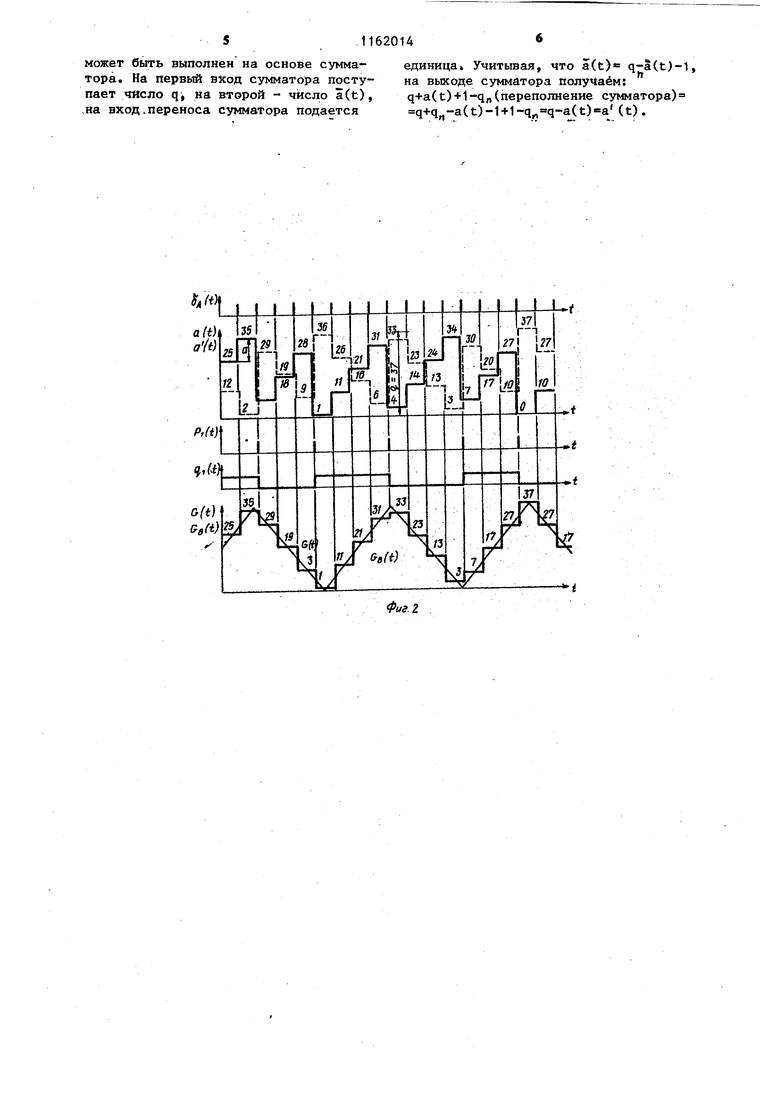

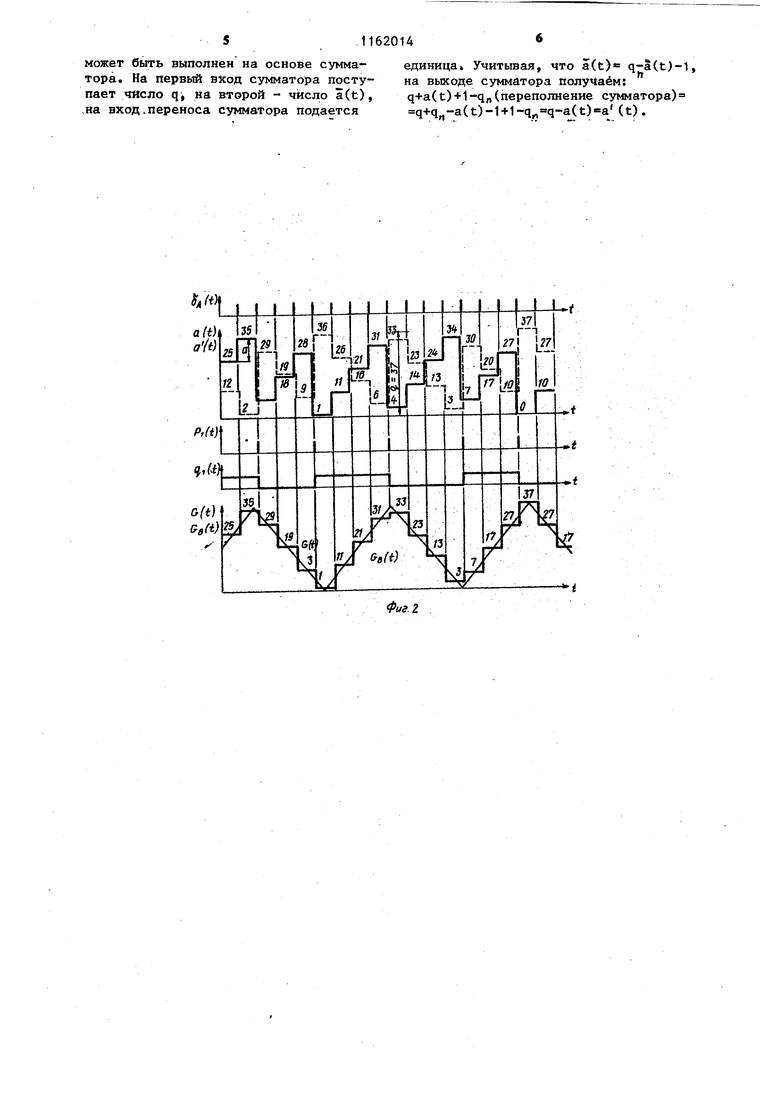

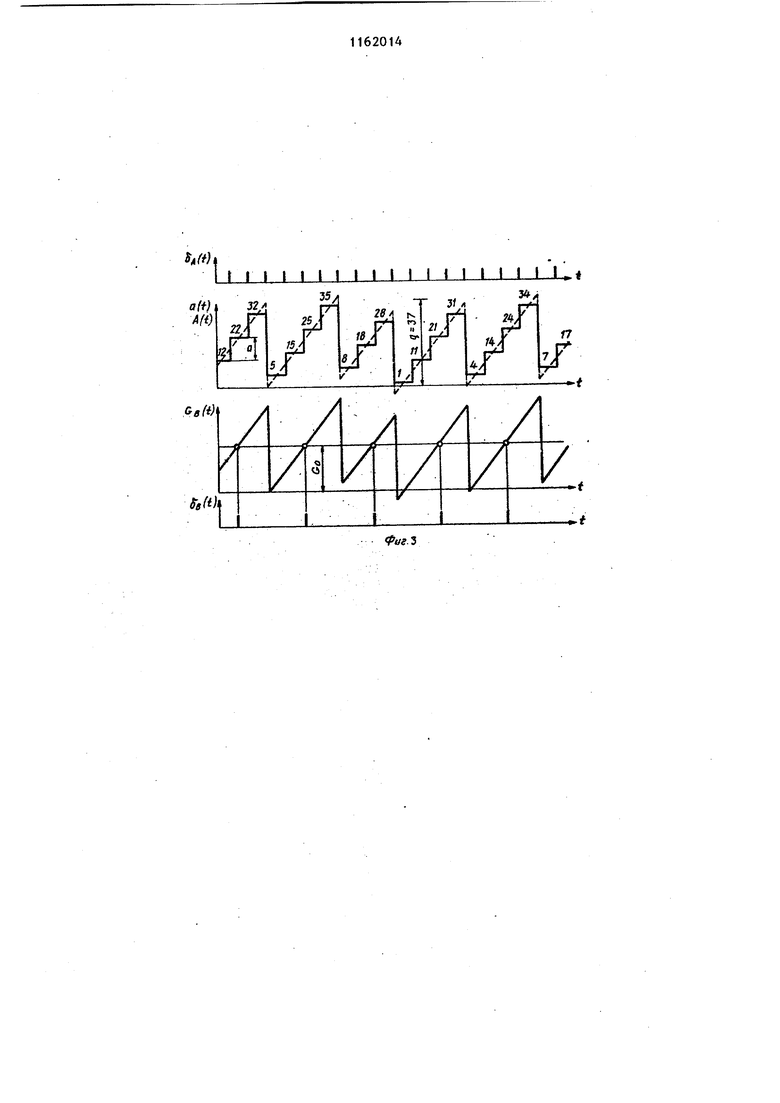

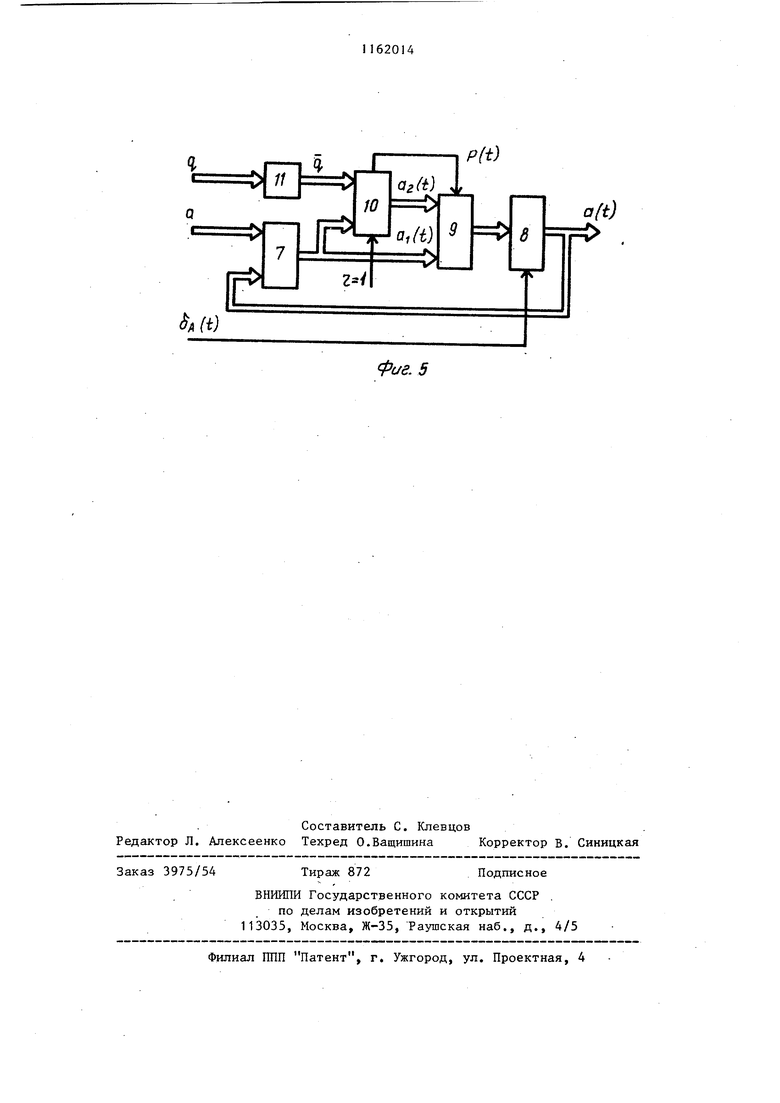

Фиг. 1 Изобретение относится к радиотехнике и может быть использовано в приемопередающих и измерительных системах, например, при построении синтезаторов частот, , Известно устройство, в котором функции делителя частоты вьтолняет накопительный регистр, коэффициент деления которого равен , где . q - емкость регистра, а - число на входе регистра D1 Выходным сигналом такого делител является последовательность импульс переполнения регистра, период следо вания которых при некратных числах а и q непостоянен, что вызывает так называемые помехи дробности. Наиболее близким к предлагаемому является делитель частоты, содержащий последовательно соединенные циф роаналоговый преобразователь, фильт а также накопительный регистр, тактовьй вход которого является тактов входом устройства, входы задания соответственно емкости регистра и дискретности приращения выходных чисел являются первым и вторым инфо мационными входами устройства 2j . Недостатком устройства является то, что, выполняя роль делителя частоты со средним коэффициентом деления , оно имеет высокий уровень амплитудной и фазовой модуляции выходного сигнала при малых дробных значениях N. Цель изобретения - уменьшение паразитной фазовой модуляции выходного сигнала. Поставленная цель достигается тем, что в делитель частоты, содерж щий последовательно соединенные цифроаналоговый преобразователь и фильтр, выход которого является вых дом устройства, а также накопительн регистр, тактовый вход которого явл ется тактовым входом устройства, вх ды задания соответственно емкости регистра и дискретности приращения выходного числа являются первым и вторым информационными входами устройства, введены мультиплексор и преобразователь кода, выход которог соединен с первым входом мультиплек сора, выход которого соединен с входом цифроаналогового преобразователя, второй вход - с выходом накопительного регистра и первым входом преобразователя кода, второй вход которого соединен с первым информационным .входом устройства, а также счетный триггер, вход которого соединен с выходом переполнения накопительного регистра, а выход с входом управления мультиплексора. На фиг, 1 приведена структурная схема предлагаемого делителя частоты; на фиг, 2 - временная диаграмма его работы; на фиг, 3 - временная диаграмма работы прототипа; на фиг, 4 диаграмма формирования выходного напряжения цифроаналогового преобразователя (НАЛ); на фиг, 5 - вариант выполнения накопительного регистра. Делитель частоты содержит последовательно соединенные ЦАП 1 и фильтр 2, а также накопительный регистр 3, тактовый вход которого является тактовым входом устройства, входы задания соответственно емкости регистра и дискретности приращения выходного числа являются первым и вторым информационными входами устройства, мультиплексор 4 и преобразователь 5 кода, выход которого соединен с первым входом мультиплексора 4, выход которого соединен с входом ЦАП 1, второй вход - с выходом накопительного -регистра 3 и первым входом преобразователя5 кода, второй вход которого соединен с первыминформационным входом устройства, а ,также счетньй триггер 6, выход которого соединен с входом переполнения накопительного регистра 3, а выход - с входом-управления мультиплексора 4, Делитель частоты работает следующим образом. Под действием тактовых импульсов 5ii(t) содержимое накопительного регистра 3, имеющего в общем случае переменную емкость q, изменяется на величину а. Числа q и а задаются соответственно -на первом и втором информационных входах устройства. Формируемая регистром 3 ступенчатая числовая функция а(t) поступает на второй вход мультиплексора 4, На первый вход мультиплексора 4 функция a(t) поступает через преобразователь 5 кода, формирующий дополнительный код а (t)q-a(t), Триггер 6 переключается импульсами переполнения Sp(t) накопительного регистра 3, в результате чего на выходах мультиплексора 4 и ЦАП 1 образуются соответственно Числовая g(t) и аналоговая G(t) функции (фиг. 2), предетавляюЕцие собой чередование восходящих и нисхо дящих участков, сопрягающихся друг с другом таким образом, что среднее значение G(t) функции С(В) выделя емые фильтром 2, является периодической функцией с частотой f fдa/2q. Коэффициент деления устройства, таким образом, равен N 2q/a. Сопряжение участков функции подробно представлено на фиг. 4. Линейные участки (восходящие и нисходящие) функции ga(t) проходят через середины ступенек процесса g(t). Они пересекаются при значениях ординат, равных О и q, где q - емкость накопительного регистра 3. При этом функция p,g(t) оказывается периодической с периодом Tg 2qTд/a. Докажем отмеченные свойства функ ции gg(t), для чего воспользуемся фиг. 4, где обозначены а,, ..., а, значения функции a(t) перед перепол нением накопительного регистра 3; 8а, ..., значения a(t) после переполнения; а, дополнения функции a(t) до емкости q перед переполнением; at) tJ - интервалы времени между момен тами пересечения восходящей ветвью Ьси абсцисс или же пересечения ею уровня q и моментами переполнени регистра 3; bt, , ..., bt - то же но для нисходящей ветви. Исходя из принципа работы накопи тельного регистра 3 можно записать равенство а„+а-9,8ап. Учитывая, что , находим . Воспольз вавшись уравнением прямой g (t)i6t, где ог ta/Tд соответственно для восходящих и нисходящих участков, получим (Sd,-ci/2lTu/ci , т.е. точки пересечения участков нах дятся на уровне О и q. Протяженность t, восходящего уча ка можно определить из уравнения gg(t,)-gg(o)q, откуда следует, что t,qTд/a. Поскольку на нисходящем участке наклон gg(t,) отличается ли знаком, то протяженность участка t,,t, и, следовательно, период треугольной функции g0(t) равен ,(. На фиг. 4 принято q 16, а 5. Из сравнения фиг. 2 и 3 следует, что в предлагаемом устройстве отсут 144 ствует паразитная модуляция выходного сигнала, присущая прототипу, и оно может использоваться в качестве синтезатора частот, шаг сетки которого равен uf fj/2q. Пример выполнения накопительного регистра 3 с переменной емкостью q приведен на фиг. 5. Собственно накопительный, регистр представлен сумматором 7 и регистром 8, включенным последовательно через нормально включенный ключ 9. 3а счет действия обратной связи с выхода регистра 8 на один из входов сумматора 7 очередное значение а (га) суммы aj(t), записываемой в регистр 8, превышает значение а, (т-1) впредыдущем такте на величину а, т.е. а,(т)а,(т-1)+а, чем обеспечивается формирование ступенчатой функции a(t). На втором, нормально закрытом входе ключа 9 присутствует функция a(t) a(t)+q+1, получаемая при помощи сумматора 10. Для этого на входы последнего подают суммируемые числа, включая единицу на входе переноса (). Обратный код q снимают с элемента НЕ 1 1. Когда сумматор 10 переполняется, импульс переполнения Р(+) переводит ключ 9 в состояние, при котором на вход регистра 8 проходит функция agCt), значение которой в этот момент времени представляет собой остаток от переполнения сумматора 10. Далее сумматор выходит из состояния переполнения, ключ 9 возвращается в исходное состояние, и процесс формирования функции ,a(t) продолжается, начиная с остатка, точно так же, как это имеет место в обычном накопительном регистре, в котором выход сумматора 7 соединен непосредственно с входом регистра 8 и который имеет емкость , где п - число разрядов. Сумматор 10 таким образом, препятствует переполнению сумматора 7. Добавляемое в него число q+1 сверх переменного числа a,(t) вызывает его переполнение на введенное число ра- нее, чем переполнился бы сумматор 7, имеющий емкость . Учитывая, что q . результирующая емкость накопительного регистра равна (q+1) q +q+l-l q. Преобразователь 5 кода служит для получения кода а (t)q-a(t) и

может быть выполнен на основе сумматора. На первый вход сумматора поступает Число q, на второй - число a(t), .на вход.переноса сумматора подается

единица Учитывая, что a(t) q-a(t)-1, на выходе сумматора получаем: q+a(t)-b1-qn (переполнение сумматора) (t)-H-1-q,,,q-a(t)a (t) .

Фиг.г

Aft)

I Г I I I I t I I I I i I t 1 i I I I I

a(f)(

&вМ

17

fae. 3

fpue. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3641442, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой фазовый детектор | 1980 |

|

SU894854A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-06-15—Публикация

1983-10-28—Подача